f7/pwr.h File Reference

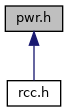

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Macros | |

| #define | PWR_CR1 MMIO32(POWER_CONTROL_BASE + 0x00) |

| Power control register (PWR_CR1) More... | |

| #define | PWR_CSR1 MMIO32(POWER_CONTROL_BASE + 0x04) |

| Power control/status register (PWR_CSR1) More... | |

| #define | PWR_CR2 MMIO32(POWER_CONTROL_BASE + 0x08) |

| Power control register 2 (PWR_CR2) More... | |

| #define | PWR_CSR2 MMIO32(POWER_CONTROL_BASE + 0x0c) |

| Power control/status register 2 (PWR_CSR2) More... | |

| #define | PWR_CR1_UDEN_LSB 18 |

| UDEN[19:18]: Under-drive enable in stop mode. More... | |

| #define | PWR_CR1_UDEN_DISABLED (0x0 << PWR_CR1_UDEN_LSB) |

| #define | PWR_CR1_UDEN_ENABLED (0x3 << PWR_CR1_UDEN_LSB) |

| #define | PWR_CR1_UDEN_MASK (0x3 << PWR_CR1_UDEN_LSB) |

| #define | PWR_CR1_ODSWEN (1 << 17) |

| ODSWEN: Over-drive switching enabled. More... | |

| #define | PWR_CR1_ODEN (1 << 16) |

| ODEN: Over-drive enable. More... | |

| #define | PWR_CR1_VOS_LSB 14 |

| #define | PWR_CR1_VOS_SCALE_3 (0x1 << PWR_CR1_VOS_LSB) |

| #define | PWR_CR1_VOS_SCALE_2 (0x2 << PWR_CR1_VOS_LSB) |

| #define | PWR_CR1_VOS_SCALE_1 (0x3 << PWR_CR1_VOS_LSB) |

| #define | PWR_CR1_VOS_MASK (0x3 << PWR_CR1_VOS_LSB) |

| #define | PWR_CR1_ADCDC1 (1 << 13) |

| ADCDC1: Masks extra flash accesses by prefetch (see AN4073) More... | |

| #define | PWR_CR1_MRUDS (1 << 11) |

| MRUDS: Main regulator in deepsleep under-drive mode. More... | |

| #define | PWR_CR1_LPUDS (1 << 10) |

| LPUDS: Low-power regulator in deepsleep under-drive mode. More... | |

| #define | PWR_CR1_FPDS (1 << 9) |

| FPDS: Flash power-down in Stop mode. More... | |

| #define | PWR_CR1_DBP (1 << 8) |

| DBP: Disable backup domain write protection. More... | |

| #define | PWR_CR1_PLS_LSB 5 |

| #define | PWR_CR1_PLS_2V0 (0x0 << PWR_CR_PLS_LSB) |

| #define | PWR_CR1_PLS_2V1 (0x1 << PWR_CR_PLS_LSB) |

| #define | PWR_CR1_PLS_2V3 (0x2 << PWR_CR_PLS_LSB) |

| #define | PWR_CR1_PLS_2V5 (0x3 << PWR_CR_PLS_LSB) |

| #define | PWR_CR1_PLS_2V6 (0x4 << PWR_CR_PLS_LSB) |

| #define | PWR_CR1_PLS_2V7 (0x5 << PWR_CR_PLS_LSB) |

| #define | PWR_CR1_PLS_2V8 (0x6 << PWR_CR_PLS_LSB) |

| #define | PWR_CR1_PLS_2V9 (0x7 << PWR_CR_PLS_LSB) |

| #define | PWR_CR1_PLS_MASK (0x7 << PWR_CR_PLS_LSB) |

| #define | PWR_CR1_PVDE (1 << 4) |

| PVDE: Power voltage detector enable. More... | |

| #define | PWR_CR1_CSBF (1 << 3) |

| CSBF: Clear standby flag. More... | |

| #define | PWR_CR1_PDDS (1 << 1) |

| PDDS: Power down deepsleep. More... | |

| #define | PWR_CR1_LPDS (1 << 0) |

| LPDS: Low-power deepsleep. More... | |

| #define | PWR_CSR1_UDRDY_LSB 18 |

| #define | PWR_CSR1_UDRDY_DISABLED (0x0 << PWR_CSR1_UDRDY_LSB) |

| #define | PWR_CSR1_UDRDY_ACTIVATED (0x3 << PWR_CSR1_UDRDY_LSB) |

| #define | PWR_CSR1_UDRDY_MASK (0x3 << PWR_CSR1_UDRDY_LSB) |

| #define | PWR_CSR1_ODSWRDY (1 << 17) |

| ODSWRDY: Over-drive mode switching ready. More... | |

| #define | PWR_CSR1_ODRDY (1 << 16) |

| ODRDY: Over-drive mode ready. More... | |

| #define | PWR_CSR1_VOSRDY (1 << 14) |

| VOSRDY: Regulator voltage scaling output selection ready bit. More... | |

| #define | PWR_CSR1_BRE (1 << 9) |

| BRE: Backup regulator enable. More... | |

| #define | PWR_CSR1_EIWUP (1 << 8) |

| EIWUP: Enable internal wakeup. More... | |

| #define | PWR_CSR1_BRR (1 << 3) |

| BRR: Backup regulator ready. More... | |

| #define | PWR_CSR1_PVDO (1 << 2) |

| PVDO: PVD output. More... | |

| #define | PWR_CSR1_SBF (1 << 1) |

| SBF: Standby flag. More... | |

| #define | PWR_CSR1_WUIF (1 << 0) |

| WUIF: Wakeup internal flag. More... | |

| #define | PWR_CR2_WUPP6 (1 << 13) |

| WUPP6: Wakeup pin polarity bit for PI11. More... | |

| #define | PWR_CR2_WUPP5 (1 << 12) |

| WUPP5: Wakeup pin polarity bit for PI8. More... | |

| #define | PWR_CR2_WUPP4 (1 << 11) |

| WUPP4: Wakeup pin polarity bit for PC13. More... | |

| #define | PWR_CR2_WUPP3 (1 << 10) |

| WUPP3: Wakeup pin polarity bit for PC1. More... | |

| #define | PWR_CR2_WUPP2 (1 << 9) |

| WUPP2: Wakeup pin polarity bit for PA2. More... | |

| #define | PWR_CR2_WUPP1 (1 << 8) |

| WUPP1: Wakeup pin polarity bit for PA0. More... | |

| #define | PWR_CR2_CWUPF6 (1 << 5) |

| CWUPF6: Clear Wakeup Pin flag for PI11. More... | |

| #define | PWR_CR2_CWUPF5 (1 << 4) |

| CWUPF5: Clear Wakeup Pin flag for PI8. More... | |

| #define | PWR_CR2_CWUPF4 (1 << 3) |

| CWUPF4: Clear Wakeup Pin flag for PC13. More... | |

| #define | PWR_CR2_CWUPF3 (1 << 2) |

| CWUPF3: Clear Wakeup Pin flag for PC1. More... | |

| #define | PWR_CR2_CWUPF2 (1 << 1) |

| CWUPF2: Clear Wakeup Pin flag for PA2. More... | |

| #define | PWR_CR2_CWUPF1 (1 << 0) |

| CWUPF1: Clear Wakeup Pin flag for PA0. More... | |

| #define | PWR_CSR2_EWUP6 (1 << 13) |

| EWUP6: Enable Wakeup pin for PI11. More... | |

| #define | PWR_CSR2_EWUP5 (1 << 12) |

| EWUP5: Enable Wakeup pin for PI8. More... | |

| #define | PWR_CSR2_EWUP4 (1 << 11) |

| EWUP4: Enable Wakeup pin for PC13. More... | |

| #define | PWR_CSR2_EWUP3 (1 << 10) |

| EWUP3: Enable Wakeup pin for PC1. More... | |

| #define | PWR_CSR2_EWUP2 (1 << 19) |

| EWUP2: Enable Wakeup pin for PA2. More... | |

| #define | PWR_CSR2_EWUP1 (1 << 18) |

| EWUP1: Enable Wakeup pin for PA0. More... | |

| #define | PWR_CSR2_WUPF6 (1 << 5) |

| WUPF6: Wakeup Pin flag for PI11. More... | |

| #define | PWR_CSR2_WUPF5 (1 << 4) |

| WUPF5: Wakeup Pin flag for PI8. More... | |

| #define | PWR_CSR2_WUPF4 (1 << 3) |

| WUPF4: Wakeup Pin flag for PC13. More... | |

| #define | PWR_CSR2_WUPF3 (1 << 2) |

| WUPF3: Wakeup Pin flag for PC1. More... | |

| #define | PWR_CSR2_WUPF2 (1 << 1) |

| WUPF2: Wakeup Pin flag for PA2. More... | |

| #define | PWR_CSR2_WUPF1 (1 << 0) |

| WUPF1: Wakeup Pin flag for PA0. More... | |

Enumerations | |

| enum | pwr_vos_scale { PWR_SCALE1 , PWR_SCALE2 , PWR_SCALE3 } |

Functions | |

| void | pwr_set_vos_scale (enum pwr_vos_scale scale) |

| void | pwr_enable_overdrive (void) |

| void | pwr_disable_overdrive (void) |