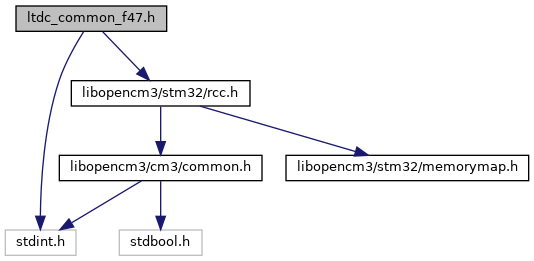

Include dependency graph for ltdc_common_f47.h:

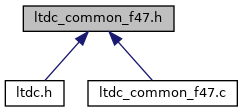

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Functions | |

| static void | ltdc_ctrl_enable (uint32_t ctrl_flags) |

| simple helper macros More... | |

| static void | ltdc_ctrl_disable (uint32_t ctrl_flags) |

| static void | ltdc_reload (uint32_t reload_flags) |

| static void | ltdc_set_background_color (uint8_t r, uint8_t g, uint8_t b) |

| static void | ltdc_get_current_position (uint16_t *x, uint16_t *y) |

| static uint16_t | ltdc_get_current_position_x (void) |

| static uint16_t | ltdc_get_current_position_y (void) |

| static uint32_t | ltdc_get_display_status (uint32_t status_flags) |

| static void | ltdc_layer_ctrl_enable (uint32_t layer, uint32_t ctrl_flags) |

| static void | ltdc_layer_ctrl_disable (uint32_t layer, uint32_t ctrl_flags) |

| static void | ltdc_set_color_key (uint32_t layer, uint8_t r, uint8_t g, uint8_t b) |

| static void | ltdc_set_pixel_format (uint32_t layer, uint32_t format) |

| static void | ltdc_set_constant_alpha (uint32_t layer, uint8_t alpha) |

| static void | ltdc_set_default_colors (uint32_t layer, uint8_t a, uint8_t r, uint8_t g, uint8_t b) |

| static void | ltdc_set_blending_factors (uint32_t layer, uint8_t bf1, uint8_t bf2) |

| static void | ltdc_set_fbuffer_address (uint32_t layer, uint32_t address) |

| static uint32_t | ltdc_get_fbuffer_address (uint32_t layer) |

| static void | ltdc_set_fb_line_length (uint32_t layer, uint16_t len, uint16_t pitch) |

| static void | ltdc_set_fb_line_count (uint32_t layer, uint16_t linecount) |

| void | ltdc_set_tft_sync_timings (uint16_t sync_width, uint16_t sync_height, uint16_t h_back_porch, uint16_t v_back_porch, uint16_t active_width, uint16_t active_height, uint16_t h_front_porch, uint16_t v_front_porch) |

| more complicated helper functions More... | |

| void | ltdc_setup_windowing (uint8_t layer_number, uint16_t h_back_porch, uint16_t v_back_porch, uint16_t h_sync, uint16_t v_sync, uint16_t width, uint16_t height) |

| LTDC Windowing Setup. More... | |

| static bool | LTDC_SRCR_IS_RELOADING (void) |

| Helper function to wait for SRCR reload to complete or so. More... | |

| static uint32_t | ltdc_get_rgb888_from_rgb565 (uint16_t rgb565) |

| color conversion helper function (simulate the ltdc color conversion) More... | |