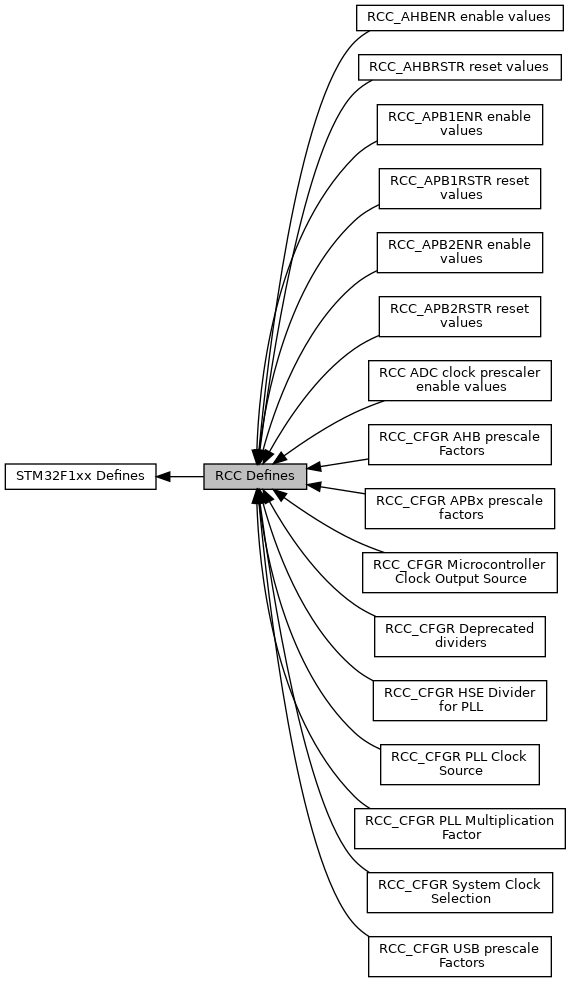

Defined Constants and Types for the STM32F1xx Reset and Clock Control More...

Data Structures | |

| struct | rcc_clock_scale |

Modules | |

| RCC_CFGR Microcontroller Clock Output Source | |

| RCC_CFGR USB prescale Factors | |

| RCC_CFGR PLL Multiplication Factor | |

| RCC_CFGR HSE Divider for PLL | |

| RCC_CFGR PLL Clock Source | |

| RCC ADC clock prescaler enable values | |

| RCC_CFGR APBx prescale factors | |

| These can be used for both APB1 and APB2 prescaling. | |

| RCC_CFGR AHB prescale Factors | |

| RCC_CFGR System Clock Selection | |

| RCC_CFGR Deprecated dividers | |

| Older compatible definitions to ease migration. | |

| RCC_APB2RSTR reset values | |

| RCC_APB1RSTR reset values | |

| RCC_AHBENR enable values | |

| RCC_APB2ENR enable values | |

| RCC_APB1ENR enable values | |

| RCC_AHBRSTR reset values | |

Enumerations | |

| enum | rcc_osc { RCC_PLL , RCC_PLL2 , RCC_PLL3 , RCC_HSE , RCC_HSI , RCC_LSE , RCC_LSI } |

| enum | rcc_periph_clken { RCC_DMA1 = _REG_BIT(0x14, 0) , RCC_DMA2 = _REG_BIT(0x14, 1) , RCC_SRAM = _REG_BIT(0x14, 2) , RCC_FLTF = _REG_BIT(0x14, 4) , RCC_CRC = _REG_BIT(0x14, 6) , RCC_FSMC = _REG_BIT(0x14, 8) , RCC_SDIO = _REG_BIT(0x14, 10) , RCC_OTGFS = _REG_BIT(0x14, 12) , RCC_ETHMAC = _REG_BIT(0x14, 14) , RCC_ETHMACTX = _REG_BIT(0x14, 15) , RCC_ETHMACRX = _REG_BIT(0x14, 16) , RCC_AFIO = _REG_BIT(0x18, 0) , RCC_GPIOA = _REG_BIT(0x18, 2) , RCC_GPIOB = _REG_BIT(0x18, 3) , RCC_GPIOC = _REG_BIT(0x18, 4) , RCC_GPIOD = _REG_BIT(0x18, 5) , RCC_GPIOE = _REG_BIT(0x18, 6) , RCC_GPIOF = _REG_BIT(0x18, 7) , RCC_GPIOG = _REG_BIT(0x18, 8) , RCC_ADC1 = _REG_BIT(0x18, 9) , RCC_ADC2 = _REG_BIT(0x18, 10) , RCC_TIM1 = _REG_BIT(0x18, 11) , RCC_SPI1 = _REG_BIT(0x18, 12) , RCC_TIM8 = _REG_BIT(0x18, 13) , RCC_USART1 = _REG_BIT(0x18, 14) , RCC_ADC3 = _REG_BIT(0x18, 15) , RCC_TIM15 = _REG_BIT(0x18, 16) , RCC_TIM16 = _REG_BIT(0x18, 17) , RCC_TIM17 = _REG_BIT(0x18, 18) , RCC_TIM9 = _REG_BIT(0x18, 19) , RCC_TIM10 = _REG_BIT(0x18, 20) , RCC_TIM11 = _REG_BIT(0x18, 21) , RCC_TIM2 = _REG_BIT(0x1C, 0) , RCC_TIM3 = _REG_BIT(0x1C, 1) , RCC_TIM4 = _REG_BIT(0x1C, 2) , RCC_TIM5 = _REG_BIT(0x1C, 3) , RCC_TIM6 = _REG_BIT(0x1C, 4) , RCC_TIM7 = _REG_BIT(0x1C, 5) , RCC_TIM12 = _REG_BIT(0x1C, 6) , RCC_TIM13 = _REG_BIT(0x1C, 7) , RCC_TIM14 = _REG_BIT(0x1C, 8) , RCC_WWDG = _REG_BIT(0x1C, 11) , RCC_SPI2 = _REG_BIT(0x1C, 14) , RCC_SPI3 = _REG_BIT(0x1C, 15) , RCC_USART2 = _REG_BIT(0x1C, 17) , RCC_USART3 = _REG_BIT(0x1C, 18) , RCC_UART4 = _REG_BIT(0x1C, 19) , RCC_UART5 = _REG_BIT(0x1C, 20) , RCC_I2C1 = _REG_BIT(0x1C, 21) , RCC_I2C2 = _REG_BIT(0x1C, 22) , RCC_USB = _REG_BIT(0x1C, 23) , RCC_CAN = _REG_BIT(0x1C, 25) , RCC_CAN1 = _REG_BIT(0x1C, 25) , RCC_CAN2 = _REG_BIT(0x1C, 26) , RCC_BKP = _REG_BIT(0x1C, 27) , RCC_PWR = _REG_BIT(0x1C, 28) , RCC_DAC = _REG_BIT(0x1C, 29) , RCC_CEC = _REG_BIT(0x1C, 30) } |

| enum | rcc_periph_rst { RST_OTGFS = _REG_BIT(0x28, 12) , RST_ETHMAC = _REG_BIT(0x28, 14) , RST_AFIO = _REG_BIT(0x0c, 0) , RST_GPIOA = _REG_BIT(0x0c, 2) , RST_GPIOB = _REG_BIT(0x0c, 3) , RST_GPIOC = _REG_BIT(0x0c, 4) , RST_GPIOD = _REG_BIT(0x0c, 5) , RST_GPIOE = _REG_BIT(0x0c, 6) , RST_GPIOF = _REG_BIT(0x0c, 7) , RST_GPIOG = _REG_BIT(0x0c, 8) , RST_ADC1 = _REG_BIT(0x0c, 9) , RST_ADC2 = _REG_BIT(0x0c, 10) , RST_TIM1 = _REG_BIT(0x0c, 11) , RST_SPI1 = _REG_BIT(0x0c, 12) , RST_TIM8 = _REG_BIT(0x0c, 13) , RST_USART1 = _REG_BIT(0x0c, 14) , RST_ADC3 = _REG_BIT(0x0c, 15) , RST_TIM15 = _REG_BIT(0x0c, 16) , RST_TIM16 = _REG_BIT(0x0c, 17) , RST_TIM17 = _REG_BIT(0x0c, 18) , RST_TIM9 = _REG_BIT(0x0c, 19) , RST_TIM10 = _REG_BIT(0x0c, 20) , RST_TIM11 = _REG_BIT(0x0c, 21) , RST_TIM2 = _REG_BIT(0x10, 0) , RST_TIM3 = _REG_BIT(0x10, 1) , RST_TIM4 = _REG_BIT(0x10, 2) , RST_TIM5 = _REG_BIT(0x10, 3) , RST_TIM6 = _REG_BIT(0x10, 4) , RST_TIM7 = _REG_BIT(0x10, 5) , RST_TIM12 = _REG_BIT(0x10, 6) , RST_TIM13 = _REG_BIT(0x10, 7) , RST_TIM14 = _REG_BIT(0x10, 8) , RST_WWDG = _REG_BIT(0x10, 11) , RST_SPI2 = _REG_BIT(0x10, 14) , RST_SPI3 = _REG_BIT(0x10, 15) , RST_USART2 = _REG_BIT(0x10, 17) , RST_USART3 = _REG_BIT(0x10, 18) , RST_UART4 = _REG_BIT(0x10, 19) , RST_UART5 = _REG_BIT(0x10, 20) , RST_I2C1 = _REG_BIT(0x10, 21) , RST_I2C2 = _REG_BIT(0x10, 22) , RST_USB = _REG_BIT(0x10, 23) , RST_CAN = _REG_BIT(0x10, 25) , RST_CAN1 = _REG_BIT(0x10, 25) , RST_CAN2 = _REG_BIT(0x10, 26) , RST_BKP = _REG_BIT(0x10, 27) , RST_PWR = _REG_BIT(0x10, 28) , RST_DAC = _REG_BIT(0x10, 29) , RST_CEC = _REG_BIT(0x10, 30) } |

| enum | rcc_clock_hsi { RCC_CLOCK_HSI_24MHZ , RCC_CLOCK_HSI_48MHZ , RCC_CLOCK_HSI_64MHZ , RCC_CLOCK_HSI_END } |

| enum | rcc_clock_hse { RCC_CLOCK_HSE12_72MHZ , RCC_CLOCK_HSE16_72MHZ , RCC_CLOCK_HSE25_72MHZ , RCC_CLOCK_HSE8_24MHZ , RCC_CLOCK_HSE8_72MHZ , RCC_CLOCK_HSE_END } |

Functions | |

| void | rcc_osc_ready_int_clear (enum rcc_osc osc) |

| RCC Clear the Oscillator Ready Interrupt Flag. More... | |

| void | rcc_osc_ready_int_enable (enum rcc_osc osc) |

| RCC Enable the Oscillator Ready Interrupt. More... | |

| void | rcc_osc_ready_int_disable (enum rcc_osc osc) |

| RCC Disable the Oscillator Ready Interrupt. More... | |

| int | rcc_osc_ready_int_flag (enum rcc_osc osc) |

| RCC Read the Oscillator Ready Interrupt Flag. More... | |

| void | rcc_css_int_clear (void) |

| RCC Clear the Clock Security System Interrupt Flag. More... | |

| int | rcc_css_int_flag (void) |

| RCC Read the Clock Security System Interrupt Flag. More... | |

| void | rcc_osc_on (enum rcc_osc osc) |

| RCC Turn on an Oscillator. More... | |

| void | rcc_osc_off (enum rcc_osc osc) |

| RCC Turn off an Oscillator. More... | |

| void | rcc_css_enable (void) |

| RCC Enable the Clock Security System. More... | |

| void | rcc_css_disable (void) |

| RCC Disable the Clock Security System. More... | |

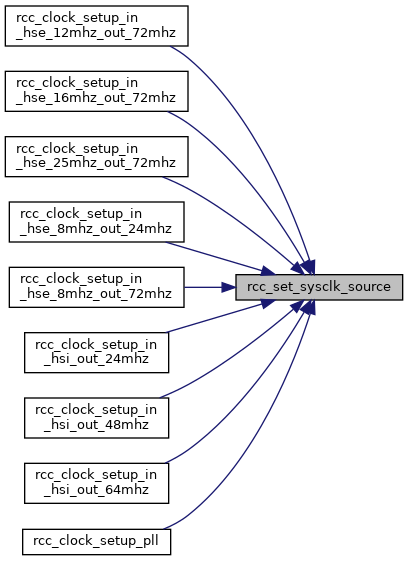

| void | rcc_set_sysclk_source (uint32_t clk) |

| RCC Set the Source for the System Clock. More... | |

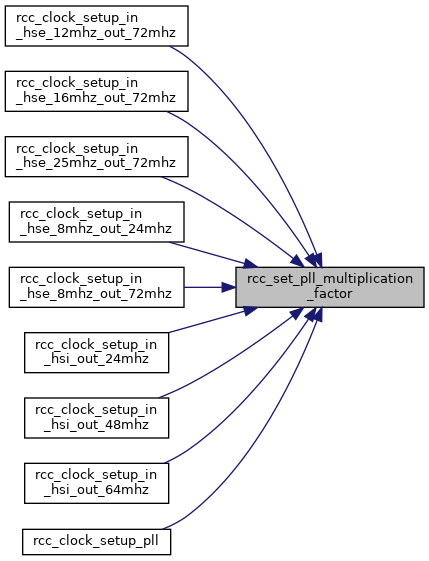

| void | rcc_set_pll_multiplication_factor (uint32_t mul) |

| RCC Set the PLL Multiplication Factor. More... | |

| void | rcc_set_pll2_multiplication_factor (uint32_t mul) |

| RCC Set the PLL2 Multiplication Factor. More... | |

| void | rcc_set_pll3_multiplication_factor (uint32_t mul) |

| RCC Set the PLL3 Multiplication Factor. More... | |

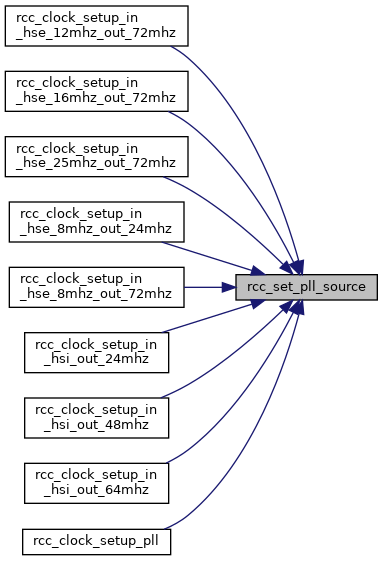

| void | rcc_set_pll_source (uint32_t pllsrc) |

| RCC Set the PLL Clock Source. More... | |

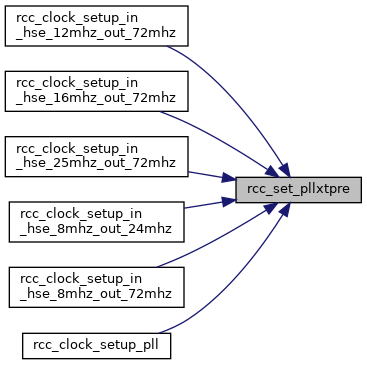

| void | rcc_set_pllxtpre (uint32_t pllxtpre) |

| RCC Set the HSE Frequency Divider used as PLL Clock Source. More... | |

| uint32_t | rcc_rtc_clock_enabled_flag (void) |

| RCC RTC Clock Enabled Flag. More... | |

| void | rcc_enable_rtc_clock (void) |

| RCC Enable the RTC clock. More... | |

| void | rcc_set_rtc_clock_source (enum rcc_osc clock_source) |

| RCC Set the Source for the RTC clock. More... | |

| void | rcc_set_adcpre (uint32_t adcpre) |

| ADC Setup the A/D Clock. More... | |

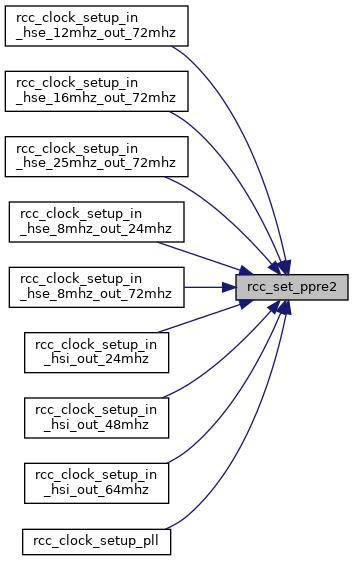

| void | rcc_set_ppre2 (uint32_t ppre2) |

| RCC Set the APB2 Prescale Factor. More... | |

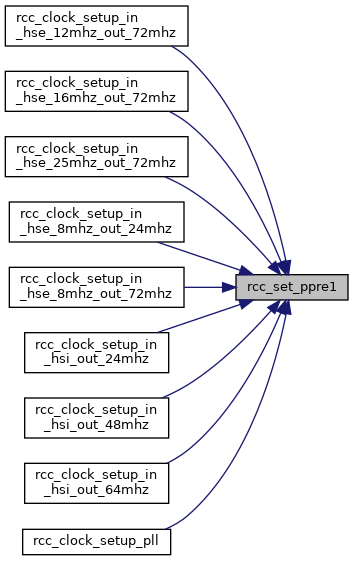

| void | rcc_set_ppre1 (uint32_t ppre1) |

| RCC Set the APB1 Prescale Factor. More... | |

| void | rcc_set_hpre (uint32_t hpre) |

| RCC Set the AHB Prescale Factor. More... | |

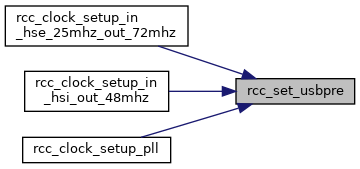

| void | rcc_set_usbpre (uint32_t usbpre) |

| RCC Set the USB Prescale Factor. More... | |

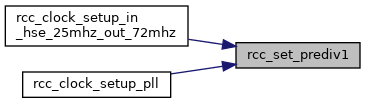

| void | rcc_set_prediv1 (uint32_t prediv) |

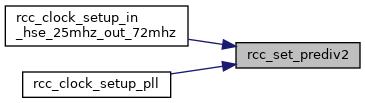

| void | rcc_set_prediv2 (uint32_t prediv) |

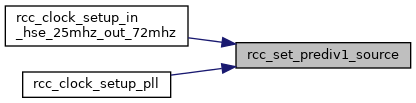

| void | rcc_set_prediv1_source (uint32_t rccsrc) |

| uint32_t | rcc_system_clock_source (void) |

| RCC Get the System Clock Source. More... | |

| void | rcc_clock_setup_in_hsi_out_64mhz (void) LIBOPENCM3_DEPRECATED("use rcc_clock_setup_pll( &rcc_hsi_configs[RCC_CLOCK_HSI_64MHZ])") |

| void | rcc_clock_setup_in_hsi_out_48mhz (void) LIBOPENCM3_DEPRECATED("use rcc_clock_setup_pll( &rcc_hsi_configs[RCC_CLOCK_HSI_48MHZ])") |

| void | rcc_clock_setup_in_hsi_out_24mhz (void) LIBOPENCM3_DEPRECATED("use rcc_clock_setup_pll( &rcc_hsi_configs[RCC_CLOCK_HSI_24MHZ])") |

| void | rcc_clock_setup_in_hse_8mhz_out_24mhz (void) LIBOPENCM3_DEPRECATED("use rcc_clock_setup_pll( &rcc_hse_configs[RCC_CLOCK_HSE8_24MHZ])") |

| void | rcc_clock_setup_in_hse_8mhz_out_72mhz (void) LIBOPENCM3_DEPRECATED("use rcc_clock_setup_pll( &rcc_hse_configs[RCC_CLOCK_HSE8_72MHZ])") |

| void | rcc_clock_setup_in_hse_12mhz_out_72mhz (void) LIBOPENCM3_DEPRECATED("use rcc_clock_setup_pll( &rcc_hse_configs[RCC_CLOCK_HSE12_72MHZ])") |

| void | rcc_clock_setup_in_hse_16mhz_out_72mhz (void) LIBOPENCM3_DEPRECATED("use rcc_clock_setup_pll( &rcc_hse_configs[RCC_CLOCK_HSE16_72MHZ])") |

| void | rcc_clock_setup_in_hse_25mhz_out_72mhz (void) LIBOPENCM3_DEPRECATED("use rcc_clock_setup_pll( &rcc_hse_configs[RCC_CLOCK_HSE25_72MHZ])") |

| void | rcc_clock_setup_pll (const struct rcc_clock_scale *clock) |

| Switch sysclock to PLL with the given parameters. More... | |

| void | rcc_backupdomain_reset (void) |

| RCC Reset the Backup Domain. More... | |

| uint32_t | rcc_get_usart_clk_freq (uint32_t usart) |

| Get the peripheral clock speed for the USART at base specified. More... | |

| uint32_t | rcc_get_timer_clk_freq (uint32_t timer) |

| Get the peripheral clock speed for the Timer at base specified. More... | |

| uint32_t | rcc_get_i2c_clk_freq (uint32_t i2c) |

| Get the peripheral clock speed for the I2C device at base specified. More... | |

| uint32_t | rcc_get_spi_clk_freq (uint32_t spi) |

| void | rcc_peripheral_enable_clock (volatile uint32_t *reg, uint32_t en) |

| RCC Enable Peripheral Clocks. More... | |

| void | rcc_peripheral_disable_clock (volatile uint32_t *reg, uint32_t en) |

| RCC Disable Peripheral Clocks. More... | |

| void | rcc_peripheral_reset (volatile uint32_t *reg, uint32_t reset) |

| RCC Reset Peripherals. More... | |

| void | rcc_peripheral_clear_reset (volatile uint32_t *reg, uint32_t clear_reset) |

| RCC Remove Reset on Peripherals. More... | |

| void | rcc_periph_clock_enable (enum rcc_periph_clken clken) |

| Enable Peripheral Clock in running mode. More... | |

| void | rcc_periph_clock_disable (enum rcc_periph_clken clken) |

| Disable Peripheral Clock in running mode. More... | |

| void | rcc_periph_reset_pulse (enum rcc_periph_rst rst) |

| Reset Peripheral, pulsed. More... | |

| void | rcc_periph_reset_hold (enum rcc_periph_rst rst) |

| Reset Peripheral, hold. More... | |

| void | rcc_periph_reset_release (enum rcc_periph_rst rst) |

| Reset Peripheral, release. More... | |

| void | rcc_set_mco (uint32_t mcosrc) |

| Select the source of Microcontroller Clock Output. More... | |

| void | rcc_osc_bypass_enable (enum rcc_osc osc) |

| RCC Enable Bypass. More... | |

| void | rcc_osc_bypass_disable (enum rcc_osc osc) |

| RCC Disable Bypass. More... | |

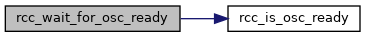

| bool | rcc_is_osc_ready (enum rcc_osc osc) |

| Is the given oscillator ready? More... | |

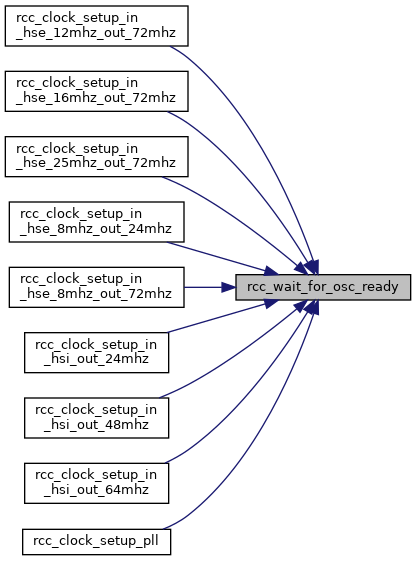

| void | rcc_wait_for_osc_ready (enum rcc_osc osc) |

| Wait for Oscillator Ready. More... | |

| uint16_t | rcc_get_div_from_hpre (uint8_t div_val) |

| This will return the divisor 1/2/4/8/16/64/128/256/512 which is set as a 4-bit value, typically used for hpre and other prescalers. More... | |

Variables | |

| uint32_t | rcc_ahb_frequency |

| uint32_t | rcc_apb1_frequency |

| Set the default clock frequencies. More... | |

| uint32_t | rcc_apb2_frequency |

| const struct rcc_clock_scale | rcc_hsi_configs [RCC_CLOCK_HSI_END] |

| const struct rcc_clock_scale | rcc_hse_configs [RCC_CLOCK_HSE_END] |

Detailed Description

Defined Constants and Types for the STM32F1xx Reset and Clock Control

- Version

- 1.0.0

- Date

- 18 August 2012

LGPL License Terms libopencm3 License

Macro Definition Documentation

◆ _REG_BIT

◆ RCC_AHBENR

◆ RCC_AHBRSTR

◆ RCC_APB1ENR

◆ RCC_APB1RSTR

◆ RCC_APB2ENR

◆ RCC_APB2RSTR

◆ RCC_BDCR

◆ RCC_BDCR_BDRST

◆ RCC_BDCR_LSEBYP

◆ RCC_BDCR_LSEON

◆ RCC_BDCR_LSERDY

◆ RCC_BDCR_RTCEN

◆ RCC_CFGR

◆ RCC_CFGR2

◆ RCC_CFGR2_I2S2SRC

◆ RCC_CFGR2_I2S2SRC_PLL3_VCO_CLK

◆ RCC_CFGR2_I2S2SRC_SYSCLK

◆ RCC_CFGR2_I2S3SRC_PLL3_VCO_CLK

◆ RCC_CFGR2_I2S3SRC_SYSCLK

◆ RCC_CFGR2_PLL2MUL

| #define RCC_CFGR2_PLL2MUL (0xF << RCC_CFGR2_PLL2MUL_SHIFT) |

◆ RCC_CFGR2_PLL2MUL_PLL2_CLK_MUL10

◆ RCC_CFGR2_PLL2MUL_PLL2_CLK_MUL11

◆ RCC_CFGR2_PLL2MUL_PLL2_CLK_MUL12

◆ RCC_CFGR2_PLL2MUL_PLL2_CLK_MUL13

◆ RCC_CFGR2_PLL2MUL_PLL2_CLK_MUL14

◆ RCC_CFGR2_PLL2MUL_PLL2_CLK_MUL16

◆ RCC_CFGR2_PLL2MUL_PLL2_CLK_MUL20

◆ RCC_CFGR2_PLL2MUL_PLL2_CLK_MUL8

◆ RCC_CFGR2_PLL2MUL_PLL2_CLK_MUL9

◆ RCC_CFGR2_PLL2MUL_SHIFT

◆ RCC_CFGR2_PLL3MUL

| #define RCC_CFGR2_PLL3MUL (0xF << RCC_CFGR2_PLL3MUL_SHIFT) |

◆ RCC_CFGR2_PLL3MUL_PLL3_CLK_MUL10

◆ RCC_CFGR2_PLL3MUL_PLL3_CLK_MUL11

◆ RCC_CFGR2_PLL3MUL_PLL3_CLK_MUL12

◆ RCC_CFGR2_PLL3MUL_PLL3_CLK_MUL13

◆ RCC_CFGR2_PLL3MUL_PLL3_CLK_MUL14

◆ RCC_CFGR2_PLL3MUL_PLL3_CLK_MUL16

◆ RCC_CFGR2_PLL3MUL_PLL3_CLK_MUL20

◆ RCC_CFGR2_PLL3MUL_PLL3_CLK_MUL8

◆ RCC_CFGR2_PLL3MUL_PLL3_CLK_MUL9

◆ RCC_CFGR2_PLL3MUL_SHIFT

◆ RCC_CFGR2_PREDIV1

| #define RCC_CFGR2_PREDIV1 (0xF << RCC_CFGR2_PREDIV1_SHIFT) |

◆ RCC_CFGR2_PREDIV1_SHIFT

◆ RCC_CFGR2_PREDIV1SRC

◆ RCC_CFGR2_PREDIV1SRC_HSE_CLK

◆ RCC_CFGR2_PREDIV1SRC_PLL2_CLK

◆ RCC_CFGR2_PREDIV2

| #define RCC_CFGR2_PREDIV2 (0xF << RCC_CFGR2_PREDIV2_SHIFT) |

◆ RCC_CFGR2_PREDIV2_DIV10

◆ RCC_CFGR2_PREDIV2_DIV11

◆ RCC_CFGR2_PREDIV2_DIV12

◆ RCC_CFGR2_PREDIV2_DIV13

◆ RCC_CFGR2_PREDIV2_DIV14

◆ RCC_CFGR2_PREDIV2_DIV15

◆ RCC_CFGR2_PREDIV2_DIV16

◆ RCC_CFGR2_PREDIV2_DIV2

◆ RCC_CFGR2_PREDIV2_DIV3

◆ RCC_CFGR2_PREDIV2_DIV4

◆ RCC_CFGR2_PREDIV2_DIV5

◆ RCC_CFGR2_PREDIV2_DIV6

◆ RCC_CFGR2_PREDIV2_DIV7

◆ RCC_CFGR2_PREDIV2_DIV8

◆ RCC_CFGR2_PREDIV2_DIV9

◆ RCC_CFGR2_PREDIV2_NODIV

◆ RCC_CFGR2_PREDIV2_SHIFT

◆ RCC_CFGR2_PREDIV_DIV10

◆ RCC_CFGR2_PREDIV_DIV11

◆ RCC_CFGR2_PREDIV_DIV12

◆ RCC_CFGR2_PREDIV_DIV13

◆ RCC_CFGR2_PREDIV_DIV14

◆ RCC_CFGR2_PREDIV_DIV15

◆ RCC_CFGR2_PREDIV_DIV16

◆ RCC_CFGR2_PREDIV_DIV2

◆ RCC_CFGR2_PREDIV_DIV3

◆ RCC_CFGR2_PREDIV_DIV4

◆ RCC_CFGR2_PREDIV_DIV5

◆ RCC_CFGR2_PREDIV_DIV6

◆ RCC_CFGR2_PREDIV_DIV7

◆ RCC_CFGR2_PREDIV_DIV8

◆ RCC_CFGR2_PREDIV_DIV9

◆ RCC_CFGR2_PREDIV_NODIV

◆ RCC_CFGR_ADCPRE

| #define RCC_CFGR_ADCPRE (3 << RCC_CFGR_ADCPRE_SHIFT) |

◆ RCC_CFGR_ADCPRE_SHIFT

◆ RCC_CFGR_HPRE

| #define RCC_CFGR_HPRE (0xF << RCC_CFGR_HPRE_SHIFT) |

◆ RCC_CFGR_HPRE_SHIFT

◆ RCC_CFGR_OTGFSPRE

◆ RCC_CFGR_PLLMUL

| #define RCC_CFGR_PLLMUL (0xF << RCC_CFGR_PLLMUL_SHIFT) |

◆ RCC_CFGR_PLLMUL_SHIFT

◆ RCC_CFGR_PLLSRC

◆ RCC_CFGR_PLLXTPRE

◆ RCC_CFGR_PPRE1

| #define RCC_CFGR_PPRE1 (7 << RCC_CFGR_PPRE1_SHIFT) |

◆ RCC_CFGR_PPRE1_MASK

◆ RCC_CFGR_PPRE1_SHIFT [1/2]

◆ RCC_CFGR_PPRE1_SHIFT [2/2]

◆ RCC_CFGR_PPRE2

| #define RCC_CFGR_PPRE2 (7 << RCC_CFGR_PPRE2_SHIFT) |

◆ RCC_CFGR_PPRE2_MASK

◆ RCC_CFGR_PPRE2_SHIFT [1/2]

◆ RCC_CFGR_PPRE2_SHIFT [2/2]

◆ RCC_CFGR_SW

| #define RCC_CFGR_SW (3 << RCC_CFGR_SW_SHIFT) |

◆ RCC_CFGR_SW_SHIFT

◆ RCC_CFGR_SWS

| #define RCC_CFGR_SWS (3 << RCC_CFGR_SWS_SHIFT) |

◆ RCC_CFGR_SWS_SHIFT

◆ RCC_CFGR_SWS_SYSCLKSEL_HSECLK

◆ RCC_CFGR_SWS_SYSCLKSEL_HSICLK

◆ RCC_CFGR_SWS_SYSCLKSEL_PLLCLK

◆ RCC_CFGR_USBPRE

◆ RCC_CFGR_USBPRE_PLL_VCO_CLK_DIV2

◆ RCC_CFGR_USBPRE_PLL_VCO_CLK_DIV3

◆ RCC_CIR

◆ RCC_CIR_CSSC

◆ RCC_CIR_CSSF

◆ RCC_CIR_HSERDYC

◆ RCC_CIR_HSERDYF

◆ RCC_CIR_HSERDYIE

◆ RCC_CIR_HSIRDYC

◆ RCC_CIR_HSIRDYF

◆ RCC_CIR_HSIRDYIE

◆ RCC_CIR_LSERDYC

◆ RCC_CIR_LSERDYF

◆ RCC_CIR_LSERDYIE

◆ RCC_CIR_LSIRDYC

◆ RCC_CIR_LSIRDYF

◆ RCC_CIR_LSIRDYIE

◆ RCC_CIR_PLL2RDYC

◆ RCC_CIR_PLL2RDYF

◆ RCC_CIR_PLL2RDYIE

◆ RCC_CIR_PLL3RDYC

◆ RCC_CIR_PLL3RDYF

◆ RCC_CIR_PLL3RDYIE

◆ RCC_CIR_PLLRDYC

◆ RCC_CIR_PLLRDYF

◆ RCC_CIR_PLLRDYIE

◆ RCC_CR

◆ RCC_CR_CSSON

◆ RCC_CR_HSEBYP

◆ RCC_CR_HSEON

◆ RCC_CR_HSERDY

◆ RCC_CR_HSION

◆ RCC_CR_HSIRDY

◆ RCC_CR_PLL2ON

◆ RCC_CR_PLL2RDY

◆ RCC_CR_PLL3ON

◆ RCC_CR_PLL3RDY

◆ RCC_CR_PLLON

◆ RCC_CR_PLLRDY

◆ RCC_CSR

◆ RCC_CSR_IWDGRSTF

◆ RCC_CSR_LPWRRSTF

◆ RCC_CSR_LSION

◆ RCC_CSR_LSIRDY

◆ RCC_CSR_PINRSTF

◆ RCC_CSR_PORRSTF

◆ RCC_CSR_RESET_FLAGS

| #define RCC_CSR_RESET_FLAGS |

◆ RCC_CSR_RMVF

◆ RCC_CSR_SFTRSTF

◆ RCC_CSR_WWDGRSTF

Enumeration Type Documentation

◆ rcc_clock_hse

| enum rcc_clock_hse |

◆ rcc_clock_hsi

| enum rcc_clock_hsi |

◆ rcc_osc

| enum rcc_osc |

◆ rcc_periph_clken

| enum rcc_periph_clken |

◆ rcc_periph_rst

| enum rcc_periph_rst |

Function Documentation

◆ rcc_backupdomain_reset()

| void rcc_backupdomain_reset | ( | void | ) |

RCC Reset the Backup Domain.

The backup domain registers are reset to disable RTC controls and clear user data.

Definition at line 1283 of file rcc.c.

References RCC_BDCR, and RCC_BDCR_BDRST.

◆ rcc_clock_setup_in_hse_12mhz_out_72mhz()

| void rcc_clock_setup_in_hse_12mhz_out_72mhz | ( | void | ) | & |

◆ rcc_clock_setup_in_hse_16mhz_out_72mhz()

| void rcc_clock_setup_in_hse_16mhz_out_72mhz | ( | void | ) | & |

◆ rcc_clock_setup_in_hse_25mhz_out_72mhz()

| void rcc_clock_setup_in_hse_25mhz_out_72mhz | ( | void | ) | & |

◆ rcc_clock_setup_in_hse_8mhz_out_24mhz()

| void rcc_clock_setup_in_hse_8mhz_out_24mhz | ( | void | ) | & |

◆ rcc_clock_setup_in_hse_8mhz_out_72mhz()

| void rcc_clock_setup_in_hse_8mhz_out_72mhz | ( | void | ) | & |

◆ rcc_clock_setup_in_hsi_out_24mhz()

| void rcc_clock_setup_in_hsi_out_24mhz | ( | void | ) | & |

◆ rcc_clock_setup_in_hsi_out_48mhz()

| void rcc_clock_setup_in_hsi_out_48mhz | ( | void | ) | & |

◆ rcc_clock_setup_in_hsi_out_64mhz()

| void rcc_clock_setup_in_hsi_out_64mhz | ( | void | ) | & |

◆ rcc_clock_setup_pll()

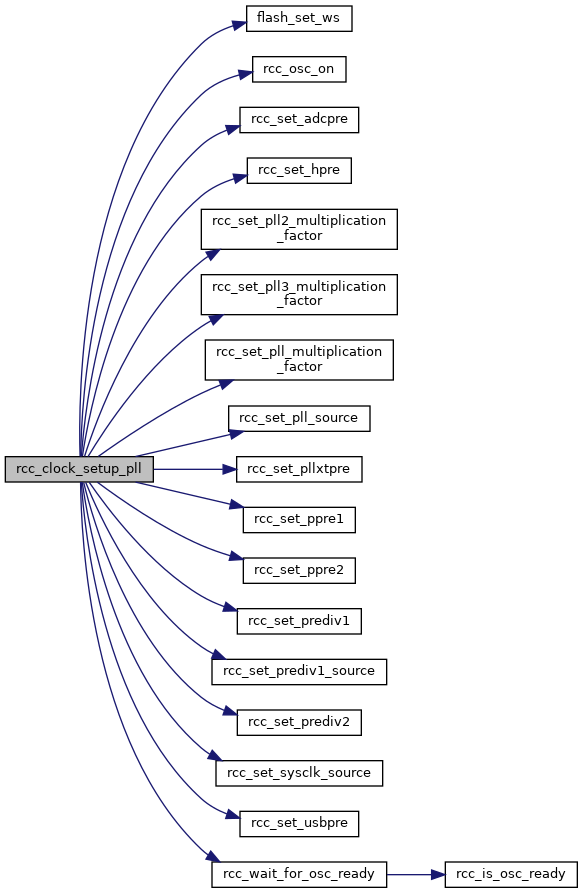

| void rcc_clock_setup_pll | ( | const struct rcc_clock_scale * | clock | ) |

Switch sysclock to PLL with the given parameters.

This should be usable from any point in time, but only if you have used library functions to manage clocks.

- Parameters

-

clock full struct with desired parameters

Definition at line 1213 of file rcc.c.

References rcc_clock_scale::adcpre, rcc_clock_scale::ahb_frequency, rcc_clock_scale::apb1_frequency, rcc_clock_scale::apb2_frequency, flash_set_ws(), rcc_clock_scale::flash_waitstates, rcc_clock_scale::hpre, rcc_clock_scale::pll2_mul, rcc_clock_scale::pll3_mul, rcc_clock_scale::pll_mul, rcc_clock_scale::pll_source, rcc_clock_scale::ppre1, rcc_clock_scale::ppre2, rcc_clock_scale::prediv1, rcc_clock_scale::prediv1_source, rcc_clock_scale::prediv2, rcc_ahb_frequency, rcc_apb1_frequency, rcc_apb2_frequency, RCC_CFGR2_PREDIV_DIV2, RCC_CFGR_PLLSRC_HSE_CLK, RCC_CFGR_SW_SYSCLKSEL_PLLCLK, RCC_HSE, RCC_HSI, rcc_osc_on(), RCC_PLL, RCC_PLL2, RCC_PLL3, rcc_set_adcpre(), rcc_set_hpre(), rcc_set_pll2_multiplication_factor(), rcc_set_pll3_multiplication_factor(), rcc_set_pll_multiplication_factor(), rcc_set_pll_source(), rcc_set_pllxtpre(), rcc_set_ppre1(), rcc_set_ppre2(), rcc_set_prediv1(), rcc_set_prediv1_source(), rcc_set_prediv2(), rcc_set_sysclk_source(), rcc_set_usbpre(), rcc_wait_for_osc_ready(), and rcc_clock_scale::usbpre.

◆ rcc_css_disable()

| void rcc_css_disable | ( | void | ) |

◆ rcc_css_enable()

| void rcc_css_enable | ( | void | ) |

RCC Enable the Clock Security System.

Definition at line 457 of file rcc.c.

References RCC_CR, and RCC_CR_CSSON.

◆ rcc_css_int_clear()

| void rcc_css_int_clear | ( | void | ) |

RCC Clear the Clock Security System Interrupt Flag.

Definition at line 327 of file rcc.c.

References RCC_CIR, and RCC_CIR_CSSC.

◆ rcc_css_int_flag()

| int rcc_css_int_flag | ( | void | ) |

RCC Read the Clock Security System Interrupt Flag.

- Returns

- int. Boolean value for flag set.

Definition at line 338 of file rcc.c.

References RCC_CIR, and RCC_CIR_CSSF.

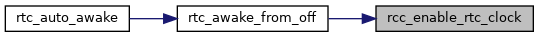

◆ rcc_enable_rtc_clock()

| void rcc_enable_rtc_clock | ( | void | ) |

RCC Enable the RTC clock.

Definition at line 570 of file rcc.c.

References RCC_BDCR, and RCC_BDCR_RTCEN.

Referenced by rtc_awake_from_off().

◆ rcc_get_div_from_hpre()

| uint16_t rcc_get_div_from_hpre | ( | uint8_t | div_val | ) |

This will return the divisor 1/2/4/8/16/64/128/256/512 which is set as a 4-bit value, typically used for hpre and other prescalers.

- Parameters

-

div_val Masked and shifted divider value from register (e.g. RCC_CFGR)

Definition at line 260 of file rcc_common_all.c.

◆ rcc_get_i2c_clk_freq()

| uint32_t rcc_get_i2c_clk_freq | ( | uint32_t | i2c | ) |

Get the peripheral clock speed for the I2C device at base specified.

- Parameters

-

i2c Base address of I2C to get clock frequency for.

Definition at line 1328 of file rcc.c.

References rcc_apb1_frequency.

◆ rcc_get_spi_clk_freq()

| uint32_t rcc_get_spi_clk_freq | ( | uint32_t | spi | ) |

◆ rcc_get_timer_clk_freq()

| uint32_t rcc_get_timer_clk_freq | ( | uint32_t | timer | ) |

Get the peripheral clock speed for the Timer at base specified.

- Parameters

-

timer Base address of TIM to get clock frequency for.

Definition at line 1309 of file rcc.c.

References cm3_assert_not_reached, rcc_clock_scale::ppre1, rcc_clock_scale::ppre2, rcc_apb1_frequency, rcc_apb2_frequency, RCC_CFGR, RCC_CFGR_PPRE1_HCLK_NODIV, RCC_CFGR_PPRE1_MASK, RCC_CFGR_PPRE1_SHIFT, RCC_CFGR_PPRE2_HCLK_NODIV, RCC_CFGR_PPRE2_MASK, RCC_CFGR_PPRE2_SHIFT, TIM14_BASE, and TIM2_BASE.

◆ rcc_get_usart_clk_freq()

| uint32_t rcc_get_usart_clk_freq | ( | uint32_t | usart | ) |

Get the peripheral clock speed for the USART at base specified.

- Parameters

-

usart Base address of USART to get clock frequency for.

Definition at line 1296 of file rcc.c.

References rcc_apb1_frequency, rcc_apb2_frequency, and USART1_BASE.

Referenced by usart_set_baudrate().

◆ rcc_is_osc_ready()

| bool rcc_is_osc_ready | ( | enum rcc_osc | osc | ) |

Is the given oscillator ready?

- Parameters

-

osc Oscillator ID

- Returns

- true if the hardware indicates the oscillator is ready.

Definition at line 343 of file rcc.c.

References RCC_BDCR, RCC_BDCR_LSERDY, RCC_CR, RCC_CR_HSERDY, RCC_CR_HSIRDY, RCC_CR_PLL2RDY, RCC_CR_PLL3RDY, RCC_CR_PLLRDY, RCC_CSR, RCC_CSR_LSIRDY, RCC_HSE, RCC_HSI, RCC_LSE, RCC_LSI, RCC_PLL, RCC_PLL2, and RCC_PLL3.

Referenced by rcc_wait_for_osc_ready().

◆ rcc_osc_bypass_disable()

| void rcc_osc_bypass_disable | ( | enum rcc_osc | osc | ) |

RCC Disable Bypass.

Re-enable the internal clock (high speed and low speed clocks only). The internal clock must be disabled (see rcc_osc_off) for this to have effect.

- Note

- The LSE clock is in the backup domain and cannot have bypass removed until the backup domain write protection has been removed (see pwr_disable_backup_domain_write_protect) or the backup domain has been reset (see rcc_backupdomain_reset).

- Parameters

-

[in] osc Oscillator ID. Only HSE and LSE have effect.

Definition at line 238 of file rcc_common_all.c.

◆ rcc_osc_bypass_enable()

| void rcc_osc_bypass_enable | ( | enum rcc_osc | osc | ) |

RCC Enable Bypass.

Enable an external clock to bypass the internal clock (high speed and low speed clocks only). The external clock must be enabled (see rcc_osc_on) and the internal clock must be disabled (see rcc_osc_off) for this to have effect.

- Note

- The LSE clock is in the backup domain and cannot be bypassed until the backup domain write protection has been removed (see pwr_disable_backup_domain_write_protect).

- Parameters

-

[in] osc Oscillator ID. Only HSE and LSE have effect.

Definition at line 208 of file rcc_common_all.c.

References RCC_BDCR, RCC_BDCR_LSEBYP, RCC_CR, RCC_CR_HSEBYP, RCC_CSR, RCC_HSE, and RCC_LSE.

◆ rcc_osc_off()

| void rcc_osc_off | ( | enum rcc_osc | osc | ) |

RCC Turn off an Oscillator.

Disable an oscillator and power off.

- Note

- An oscillator cannot be turned off if it is selected as the system clock.

- The LSE clock is in the backup domain and cannot be disabled until the backup domain write protection has been removed (see pwr_disable_backup_domain_write_protect) or the backup domain has been (see reset rcc_backupdomain_reset).

- Parameters

-

[in] osc Oscillator ID

Definition at line 425 of file rcc.c.

References RCC_BDCR, RCC_CR, RCC_CSR, RCC_HSE, RCC_HSI, RCC_LSE, RCC_LSI, RCC_PLL, RCC_PLL2, and RCC_PLL3.

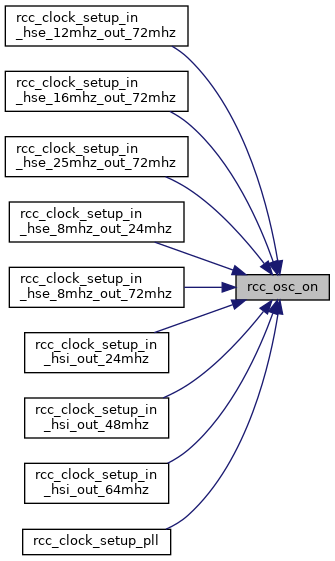

◆ rcc_osc_on()

| void rcc_osc_on | ( | enum rcc_osc | osc | ) |

RCC Turn on an Oscillator.

Enable an oscillator and power on. Each oscillator requires an amount of time to settle to a usable state. Refer to datasheets for time delay information. A status flag is available to indicate when the oscillator becomes ready (see rcc_osc_ready_int_flag and rcc_wait_for_osc_ready).

- Note

- The LSE clock is in the backup domain and cannot be enabled until the backup domain write protection has been removed (see pwr_disable_backup_domain_write_protect).

- Parameters

-

[in] osc Oscillator ID

Definition at line 384 of file rcc.c.

References RCC_BDCR, RCC_BDCR_LSEON, RCC_CR, RCC_CR_HSEON, RCC_CR_HSION, RCC_CR_PLL2ON, RCC_CR_PLL3ON, RCC_CR_PLLON, RCC_CSR, RCC_CSR_LSION, RCC_HSE, RCC_HSI, RCC_LSE, RCC_LSI, RCC_PLL, RCC_PLL2, and RCC_PLL3.

Referenced by rcc_clock_setup_in_hse_12mhz_out_72mhz(), rcc_clock_setup_in_hse_16mhz_out_72mhz(), rcc_clock_setup_in_hse_25mhz_out_72mhz(), rcc_clock_setup_in_hse_8mhz_out_24mhz(), rcc_clock_setup_in_hse_8mhz_out_72mhz(), rcc_clock_setup_in_hsi_out_24mhz(), rcc_clock_setup_in_hsi_out_48mhz(), rcc_clock_setup_in_hsi_out_64mhz(), and rcc_clock_setup_pll().

◆ rcc_osc_ready_int_clear()

| void rcc_osc_ready_int_clear | ( | enum rcc_osc | osc | ) |

RCC Clear the Oscillator Ready Interrupt Flag.

Clear the interrupt flag that was set when a clock oscillator became ready to use.

- Parameters

-

[in] osc Oscillator ID

Definition at line 193 of file rcc.c.

References RCC_CIR, RCC_CIR_HSERDYC, RCC_CIR_HSIRDYC, RCC_CIR_LSERDYC, RCC_CIR_LSIRDYC, RCC_CIR_PLL2RDYC, RCC_CIR_PLL3RDYC, RCC_CIR_PLLRDYC, RCC_HSE, RCC_HSI, RCC_LSE, RCC_LSI, RCC_PLL, RCC_PLL2, and RCC_PLL3.

◆ rcc_osc_ready_int_disable()

| void rcc_osc_ready_int_disable | ( | enum rcc_osc | osc | ) |

◆ rcc_osc_ready_int_enable()

| void rcc_osc_ready_int_enable | ( | enum rcc_osc | osc | ) |

RCC Enable the Oscillator Ready Interrupt.

- Parameters

-

osc Oscillator ID

Definition at line 226 of file rcc.c.

References RCC_CIR, RCC_CIR_HSERDYIE, RCC_CIR_HSIRDYIE, RCC_CIR_LSERDYIE, RCC_CIR_LSIRDYIE, RCC_CIR_PLL2RDYIE, RCC_CIR_PLL3RDYIE, RCC_CIR_PLLRDYIE, RCC_HSE, RCC_HSI, RCC_LSE, RCC_LSI, RCC_PLL, RCC_PLL2, and RCC_PLL3.

◆ rcc_osc_ready_int_flag()

| int rcc_osc_ready_int_flag | ( | enum rcc_osc | osc | ) |

RCC Read the Oscillator Ready Interrupt Flag.

- Parameters

-

[in] osc Oscillator ID

- Returns

- int. Boolean value for flag set.

Definition at line 293 of file rcc.c.

References cm3_assert_not_reached, RCC_CIR, RCC_CIR_HSERDYF, RCC_CIR_HSIRDYF, RCC_CIR_LSERDYF, RCC_CIR_LSIRDYF, RCC_CIR_PLL2RDYF, RCC_CIR_PLL3RDYF, RCC_CIR_PLLRDYF, RCC_HSE, RCC_HSI, RCC_LSE, RCC_LSI, RCC_PLL, RCC_PLL2, and RCC_PLL3.

◆ rcc_periph_clock_disable()

| void rcc_periph_clock_disable | ( | enum rcc_periph_clken | clken | ) |

Disable Peripheral Clock in running mode.

Disable the clock on particular peripheral.

- Parameters

-

[in] clken rcc_periph_clken Peripheral RCC

For available constants, see rcc_periph_clken (RCC_UART1 for example)

Definition at line 139 of file rcc_common_all.c.

References _RCC_REG.

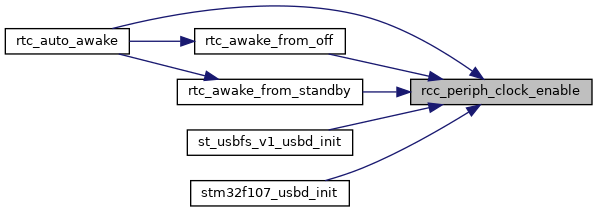

◆ rcc_periph_clock_enable()

| void rcc_periph_clock_enable | ( | enum rcc_periph_clken | clken | ) |

Enable Peripheral Clock in running mode.

Enable the clock on particular peripheral.

- Parameters

-

[in] clken rcc_periph_clken Peripheral RCC

For available constants, see rcc_periph_clken (RCC_UART1 for example)

Definition at line 127 of file rcc_common_all.c.

References _RCC_BIT, and _RCC_REG.

Referenced by rtc_auto_awake(), rtc_awake_from_off(), rtc_awake_from_standby(), st_usbfs_v1_usbd_init(), and stm32f107_usbd_init().

◆ rcc_periph_reset_hold()

| void rcc_periph_reset_hold | ( | enum rcc_periph_rst | rst | ) |

Reset Peripheral, hold.

Reset particular peripheral, and hold in reset state.

- Parameters

-

[in] rst rcc_periph_rst Peripheral reset

For available constants, see rcc_periph_rst (RST_UART1 for example)

Definition at line 166 of file rcc_common_all.c.

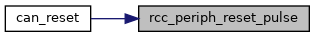

◆ rcc_periph_reset_pulse()

| void rcc_periph_reset_pulse | ( | enum rcc_periph_rst | rst | ) |

Reset Peripheral, pulsed.

Reset particular peripheral, and restore to working state.

- Parameters

-

[in] rst rcc_periph_rst Peripheral reset

For available constants, see rcc_periph_rst (RST_UART1 for example)

Definition at line 152 of file rcc_common_all.c.

References _RCC_BIT, and _RCC_REG.

Referenced by can_reset().

◆ rcc_periph_reset_release()

| void rcc_periph_reset_release | ( | enum rcc_periph_rst | rst | ) |

Reset Peripheral, release.

Restore peripheral from reset state to working state.

- Parameters

-

[in] rst rcc_periph_rst Peripheral reset

For available constants, see rcc_periph_rst (RST_UART1 for example)

Definition at line 179 of file rcc_common_all.c.

References _RCC_REG.

◆ rcc_peripheral_clear_reset()

| void rcc_peripheral_clear_reset | ( | volatile uint32_t * | reg, |

| uint32_t | clear_reset | ||

| ) |

RCC Remove Reset on Peripherals.

Remove the reset on particular peripherals. There are three registers involved, each one controlling reset of peripherals associated with the AHB, APB1 and APB2 respectively. Several peripherals could have the reset removed simultaneously only if they are controlled by the same register.

- See also

- rcc_periph_reset_release for a less error prone version, if you only need to unreset a single peripheral.

- rcc_periph_reset_pulse if you are only going to toggle reset anyway.

- Parameters

-

[in] *reg Unsigned int32. Pointer to a Reset Register (either RCC_AHBENR, RCC_APB1ENR or RCC_APB2ENR) [in] clear_reset Unsigned int32. Logical OR of all resets to be removed: - If register is RCC_AHBRSTR, from RCC_AHBRSTR reset values

- If register is RCC_APB1RSTR, from RCC_APB1RSTR reset values

- If register is RCC_APB2RSTR, from RCC_APB2RSTR reset values

Definition at line 111 of file rcc_common_all.c.

◆ rcc_peripheral_disable_clock()

| void rcc_peripheral_disable_clock | ( | volatile uint32_t * | reg, |

| uint32_t | en | ||

| ) |

RCC Disable Peripheral Clocks.

Disable the clock on particular peripherals. There are three registers involved, each one controlling the enabling of clocks associated with the AHB, APB1 and APB2 respectively. Several peripherals could be disabled simultaneously only if they are controlled by the same register.

- See also

- rcc_periph_clock_disable for a less error prone version, if you only need to disable a single peripheral.

- Parameters

-

[in] *reg Unsigned int32. Pointer to a Clock Enable Register (either RCC_AHBENR, RCC_APB1ENR or RCC_APB2ENR) [in] en Unsigned int32. Logical OR of all enables to be used for disabling. - If register is RCC_AHBENR, from RCC_AHBENR enable values

- If register is RCC_APB1ENR, from RCC_APB1ENR enable values

- If register is RCC_APB2ENR, from RCC_APB2ENR enable values

Definition at line 66 of file rcc_common_all.c.

◆ rcc_peripheral_enable_clock()

| void rcc_peripheral_enable_clock | ( | volatile uint32_t * | reg, |

| uint32_t | en | ||

| ) |

RCC Enable Peripheral Clocks.

Enable the clock on particular peripherals. There are three registers involved, each one controlling the enabling of clocks associated with the AHB, APB1 and APB2 respectively. Several peripherals could be enabled simultaneously only if they are controlled by the same register.

- See also

- rcc_periph_clock_enable for a less error prone version, if you only need to enable a single peripheral.

- Parameters

-

[in] *reg Unsigned int32. Pointer to a Clock Enable Register (either RCC_AHBENR, RCC_APB1ENR or RCC_APB2ENR) [in] en Unsigned int32. Logical OR of all enables to be set - If register is RCC_AHBENR, from RCC_AHBENR enable values

- If register is RCC_APB1ENR, from RCC_APB1ENR enable values

- If register is RCC_APB2ENR, from RCC_APB2ENR enable values

Definition at line 44 of file rcc_common_all.c.

◆ rcc_peripheral_reset()

| void rcc_peripheral_reset | ( | volatile uint32_t * | reg, |

| uint32_t | reset | ||

| ) |

RCC Reset Peripherals.

Reset particular peripherals. There are three registers involved, each one controlling reset of peripherals associated with the AHB, APB1 and APB2 respectively. Several peripherals could be reset simultaneously only if they are controlled by the same register.

- See also

- rcc_periph_reset_hold for a less error prone version, if you only need to reset a single peripheral.

- rcc_periph_reset_pulse if you are only going to toggle reset anyway.

- Parameters

-

[in] *reg Unsigned int32. Pointer to a Reset Register (either RCC_AHBENR, RCC_APB1ENR or RCC_APB2ENR) [in] reset Unsigned int32. Logical OR of all resets. - If register is RCC_AHBRSTR, from RCC_AHBRSTR reset values

- If register is RCC_APB1RSTR, from RCC_APB1RSTR reset values

- If register is RCC_APB2RSTR, from RCC_APB2RSTR reset values

Definition at line 88 of file rcc_common_all.c.

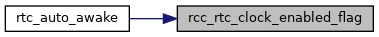

◆ rcc_rtc_clock_enabled_flag()

| uint32_t rcc_rtc_clock_enabled_flag | ( | void | ) |

RCC RTC Clock Enabled Flag.

- Returns

- uint32_t. Nonzero if the RTC Clock is enabled.

Definition at line 560 of file rcc.c.

References RCC_BDCR, and RCC_BDCR_RTCEN.

Referenced by rtc_auto_awake().

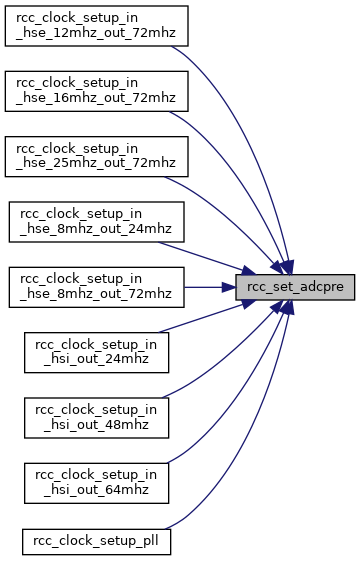

◆ rcc_set_adcpre()

| void rcc_set_adcpre | ( | uint32_t | adcpre | ) |

ADC Setup the A/D Clock.

The ADC's have a common clock prescale setting.

- Parameters

-

[in] adcpre uint32_t. Prescale divider taken from RCC ADC clock prescaler enable values

Definition at line 632 of file rcc.c.

References rcc_clock_scale::adcpre, RCC_CFGR, and RCC_CFGR_ADCPRE_SHIFT.

Referenced by rcc_clock_setup_in_hse_12mhz_out_72mhz(), rcc_clock_setup_in_hse_16mhz_out_72mhz(), rcc_clock_setup_in_hse_25mhz_out_72mhz(), rcc_clock_setup_in_hse_8mhz_out_24mhz(), rcc_clock_setup_in_hse_8mhz_out_72mhz(), rcc_clock_setup_in_hsi_out_24mhz(), rcc_clock_setup_in_hsi_out_48mhz(), rcc_clock_setup_in_hsi_out_64mhz(), and rcc_clock_setup_pll().

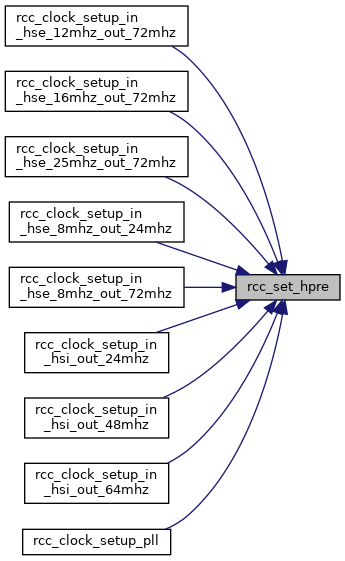

◆ rcc_set_hpre()

| void rcc_set_hpre | ( | uint32_t | hpre | ) |

RCC Set the AHB Prescale Factor.

- Parameters

-

[in] hpre Unsigned int32. AHB prescale factor RCC_CFGR AHB prescale Factors

Definition at line 671 of file rcc.c.

References rcc_clock_scale::hpre, RCC_CFGR, and RCC_CFGR_HPRE_SHIFT.

Referenced by rcc_clock_setup_in_hse_12mhz_out_72mhz(), rcc_clock_setup_in_hse_16mhz_out_72mhz(), rcc_clock_setup_in_hse_25mhz_out_72mhz(), rcc_clock_setup_in_hse_8mhz_out_24mhz(), rcc_clock_setup_in_hse_8mhz_out_72mhz(), rcc_clock_setup_in_hsi_out_24mhz(), rcc_clock_setup_in_hsi_out_48mhz(), rcc_clock_setup_in_hsi_out_64mhz(), and rcc_clock_setup_pll().

◆ rcc_set_mco()

| void rcc_set_mco | ( | uint32_t | mcosrc | ) |

Select the source of Microcontroller Clock Output.

Exact sources available depend on your target. On devices with multiple MCO pins, this function controls MCO1

- Parameters

-

[in] mcosrc the unshifted source bits

Definition at line 191 of file rcc_common_all.c.

References RCC_CFGR, RCC_CFGR_MCO_MASK, and RCC_CFGR_MCO_SHIFT.

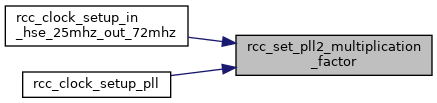

◆ rcc_set_pll2_multiplication_factor()

| void rcc_set_pll2_multiplication_factor | ( | uint32_t | mul | ) |

RCC Set the PLL2 Multiplication Factor.

- Note

- This only has effect when the PLL is disabled.

- Parameters

-

[in] mul Unsigned int32. PLL multiplication factor RCC_CFGR PLL Multiplication Factor

Definition at line 506 of file rcc.c.

References RCC_CFGR2, and RCC_CFGR2_PLL2MUL_SHIFT.

Referenced by rcc_clock_setup_in_hse_25mhz_out_72mhz(), and rcc_clock_setup_pll().

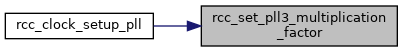

◆ rcc_set_pll3_multiplication_factor()

| void rcc_set_pll3_multiplication_factor | ( | uint32_t | mul | ) |

RCC Set the PLL3 Multiplication Factor.

- Note

- This only has effect when the PLL is disabled.

- Parameters

-

[in] mul Unsigned int32. PLL multiplication factor RCC_CFGR PLL Multiplication Factor

Definition at line 520 of file rcc.c.

References RCC_CFGR2, and RCC_CFGR2_PLL3MUL_SHIFT.

Referenced by rcc_clock_setup_pll().

◆ rcc_set_pll_multiplication_factor()

| void rcc_set_pll_multiplication_factor | ( | uint32_t | mul | ) |

RCC Set the PLL Multiplication Factor.

- Note

- This only has effect when the PLL is disabled.

- Parameters

-

[in] mul Unsigned int32. PLL multiplication factor RCC_CFGR PLL Multiplication Factor

Definition at line 492 of file rcc.c.

References RCC_CFGR, and RCC_CFGR_PLLMUL_SHIFT.

Referenced by rcc_clock_setup_in_hse_12mhz_out_72mhz(), rcc_clock_setup_in_hse_16mhz_out_72mhz(), rcc_clock_setup_in_hse_25mhz_out_72mhz(), rcc_clock_setup_in_hse_8mhz_out_24mhz(), rcc_clock_setup_in_hse_8mhz_out_72mhz(), rcc_clock_setup_in_hsi_out_24mhz(), rcc_clock_setup_in_hsi_out_48mhz(), rcc_clock_setup_in_hsi_out_64mhz(), and rcc_clock_setup_pll().

◆ rcc_set_pll_source()

| void rcc_set_pll_source | ( | uint32_t | pllsrc | ) |

RCC Set the PLL Clock Source.

- Note

- This only has effect when the PLL is disabled.

- Parameters

-

[in] pllsrc Unsigned int32. PLL clock source RCC_CFGR PLL Clock Source

Definition at line 534 of file rcc.c.

References RCC_CFGR.

Referenced by rcc_clock_setup_in_hse_12mhz_out_72mhz(), rcc_clock_setup_in_hse_16mhz_out_72mhz(), rcc_clock_setup_in_hse_25mhz_out_72mhz(), rcc_clock_setup_in_hse_8mhz_out_24mhz(), rcc_clock_setup_in_hse_8mhz_out_72mhz(), rcc_clock_setup_in_hsi_out_24mhz(), rcc_clock_setup_in_hsi_out_48mhz(), rcc_clock_setup_in_hsi_out_64mhz(), and rcc_clock_setup_pll().

◆ rcc_set_pllxtpre()

| void rcc_set_pllxtpre | ( | uint32_t | pllxtpre | ) |

RCC Set the HSE Frequency Divider used as PLL Clock Source.

- Note

- This only has effect when the PLL is disabled.

- Parameters

-

[in] pllxtpre Unsigned int32. HSE division factor RCC_CFGR HSE Divider for PLL

Definition at line 548 of file rcc.c.

References RCC_CFGR.

Referenced by rcc_clock_setup_in_hse_12mhz_out_72mhz(), rcc_clock_setup_in_hse_16mhz_out_72mhz(), rcc_clock_setup_in_hse_25mhz_out_72mhz(), rcc_clock_setup_in_hse_8mhz_out_24mhz(), rcc_clock_setup_in_hse_8mhz_out_72mhz(), and rcc_clock_setup_pll().

◆ rcc_set_ppre1()

| void rcc_set_ppre1 | ( | uint32_t | ppre1 | ) |

RCC Set the APB1 Prescale Factor.

- Note

- The APB1 clock frequency must not exceed 36MHz.

- Parameters

-

[in] ppre1 Unsigned int32. APB1 prescale factor rcc_cfgr_apb1pre

Definition at line 658 of file rcc.c.

References rcc_clock_scale::ppre1, RCC_CFGR, and RCC_CFGR_PPRE1_SHIFT.

Referenced by rcc_clock_setup_in_hse_12mhz_out_72mhz(), rcc_clock_setup_in_hse_16mhz_out_72mhz(), rcc_clock_setup_in_hse_25mhz_out_72mhz(), rcc_clock_setup_in_hse_8mhz_out_24mhz(), rcc_clock_setup_in_hse_8mhz_out_72mhz(), rcc_clock_setup_in_hsi_out_24mhz(), rcc_clock_setup_in_hsi_out_48mhz(), rcc_clock_setup_in_hsi_out_64mhz(), and rcc_clock_setup_pll().

◆ rcc_set_ppre2()

| void rcc_set_ppre2 | ( | uint32_t | ppre2 | ) |

RCC Set the APB2 Prescale Factor.

- Parameters

-

[in] ppre2 Unsigned int32. APB2 prescale factor rcc_cfgr_apb2pre

Definition at line 644 of file rcc.c.

References rcc_clock_scale::ppre2, RCC_CFGR, and RCC_CFGR_PPRE2_SHIFT.

Referenced by rcc_clock_setup_in_hse_12mhz_out_72mhz(), rcc_clock_setup_in_hse_16mhz_out_72mhz(), rcc_clock_setup_in_hse_25mhz_out_72mhz(), rcc_clock_setup_in_hse_8mhz_out_24mhz(), rcc_clock_setup_in_hse_8mhz_out_72mhz(), rcc_clock_setup_in_hsi_out_24mhz(), rcc_clock_setup_in_hsi_out_48mhz(), rcc_clock_setup_in_hsi_out_64mhz(), and rcc_clock_setup_pll().

◆ rcc_set_prediv1()

| void rcc_set_prediv1 | ( | uint32_t | prediv | ) |

Definition at line 698 of file rcc.c.

References RCC_CFGR2, and RCC_CFGR2_PREDIV1_SHIFT.

Referenced by rcc_clock_setup_in_hse_25mhz_out_72mhz(), and rcc_clock_setup_pll().

◆ rcc_set_prediv1_source()

| void rcc_set_prediv1_source | ( | uint32_t | rccsrc | ) |

Definition at line 710 of file rcc.c.

References RCC_CFGR2, and RCC_CFGR2_PREDIV1SRC.

Referenced by rcc_clock_setup_in_hse_25mhz_out_72mhz(), and rcc_clock_setup_pll().

◆ rcc_set_prediv2()

| void rcc_set_prediv2 | ( | uint32_t | prediv | ) |

Definition at line 704 of file rcc.c.

References RCC_CFGR2, and RCC_CFGR2_PREDIV2_SHIFT.

Referenced by rcc_clock_setup_in_hse_25mhz_out_72mhz(), and rcc_clock_setup_pll().

◆ rcc_set_rtc_clock_source()

| void rcc_set_rtc_clock_source | ( | enum rcc_osc | clock_source | ) |

RCC Set the Source for the RTC clock.

- Parameters

-

[in] clock_source RTC clock source. Only HSE/128, LSE and LSI.

Definition at line 581 of file rcc.c.

References RCC_BDCR, RCC_BDCR_LSEON, RCC_BDCR_LSERDY, RCC_CR, RCC_CR_HSEON, RCC_CR_HSERDY, RCC_CSR, RCC_CSR_LSION, RCC_CSR_LSIRDY, RCC_HSE, RCC_HSI, RCC_LSE, RCC_LSI, RCC_PLL, RCC_PLL2, and RCC_PLL3.

Referenced by rtc_awake_from_off().

◆ rcc_set_sysclk_source()

| void rcc_set_sysclk_source | ( | uint32_t | clk | ) |

RCC Set the Source for the System Clock.

- Parameters

-

[in] clk Unsigned int32. System Clock Selection RCC_CFGR System Clock Selection

Definition at line 478 of file rcc.c.

References RCC_CFGR, and RCC_CFGR_SW_SHIFT.

Referenced by rcc_clock_setup_in_hse_12mhz_out_72mhz(), rcc_clock_setup_in_hse_16mhz_out_72mhz(), rcc_clock_setup_in_hse_25mhz_out_72mhz(), rcc_clock_setup_in_hse_8mhz_out_24mhz(), rcc_clock_setup_in_hse_8mhz_out_72mhz(), rcc_clock_setup_in_hsi_out_24mhz(), rcc_clock_setup_in_hsi_out_48mhz(), rcc_clock_setup_in_hsi_out_64mhz(), and rcc_clock_setup_pll().

◆ rcc_set_usbpre()

| void rcc_set_usbpre | ( | uint32_t | usbpre | ) |

RCC Set the USB Prescale Factor.

The prescale factor can be set to 1 (no prescale) for use when the PLL clock is 48MHz, or 1.5 to generate the 48MHz USB clock from a 72MHz PLL clock.

- Note

- This bit cannot be reset while the USB clock is enabled.

- Parameters

-

[in] usbpre Unsigned int32. USB prescale factor RCC_CFGR USB prescale Factors

Definition at line 689 of file rcc.c.

References RCC_CFGR, RCC_CFGR_USBPRE, and rcc_clock_scale::usbpre.

Referenced by rcc_clock_setup_in_hse_25mhz_out_72mhz(), rcc_clock_setup_in_hsi_out_48mhz(), and rcc_clock_setup_pll().

◆ rcc_system_clock_source()

| uint32_t rcc_system_clock_source | ( | void | ) |

RCC Get the System Clock Source.

- Returns

- Unsigned int32. System clock source:

- 00 indicates HSE

- 01 indicates LSE

- 02 indicates PLL

Definition at line 728 of file rcc.c.

References RCC_CFGR, RCC_CFGR_SWS, and RCC_CFGR_SWS_SHIFT.

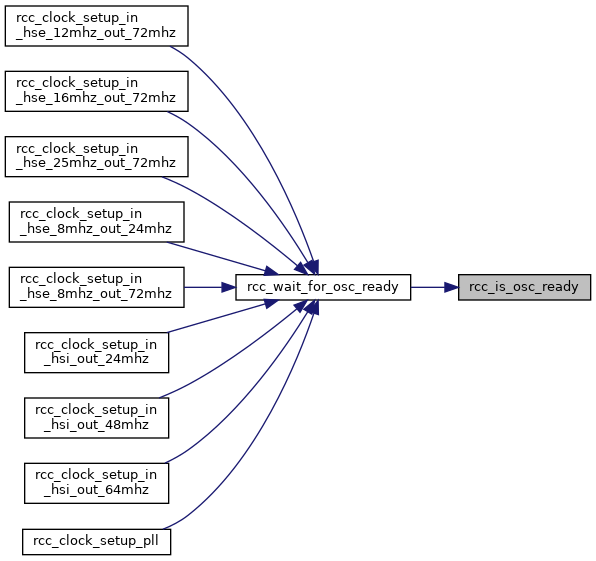

◆ rcc_wait_for_osc_ready()

| void rcc_wait_for_osc_ready | ( | enum rcc_osc | osc | ) |

Wait for Oscillator Ready.

Block until the hardware indicates that the Oscillator is ready.

- Parameters

-

osc Oscillator ID

Definition at line 364 of file rcc.c.

References rcc_is_osc_ready().

Referenced by rcc_clock_setup_in_hse_12mhz_out_72mhz(), rcc_clock_setup_in_hse_16mhz_out_72mhz(), rcc_clock_setup_in_hse_25mhz_out_72mhz(), rcc_clock_setup_in_hse_8mhz_out_24mhz(), rcc_clock_setup_in_hse_8mhz_out_72mhz(), rcc_clock_setup_in_hsi_out_24mhz(), rcc_clock_setup_in_hsi_out_48mhz(), rcc_clock_setup_in_hsi_out_64mhz(), and rcc_clock_setup_pll().

Variable Documentation

◆ rcc_ahb_frequency

|

extern |

Definition at line 59 of file rcc.c.

Referenced by rcc_clock_setup_in_hse_12mhz_out_72mhz(), rcc_clock_setup_in_hse_16mhz_out_72mhz(), rcc_clock_setup_in_hse_25mhz_out_72mhz(), rcc_clock_setup_in_hse_8mhz_out_24mhz(), rcc_clock_setup_in_hse_8mhz_out_72mhz(), rcc_clock_setup_in_hsi_out_24mhz(), rcc_clock_setup_in_hsi_out_48mhz(), rcc_clock_setup_in_hsi_out_64mhz(), and rcc_clock_setup_pll().

◆ rcc_apb1_frequency

|

extern |

Set the default clock frequencies.

Definition at line 57 of file rcc.c.

Referenced by rcc_clock_setup_in_hse_12mhz_out_72mhz(), rcc_clock_setup_in_hse_16mhz_out_72mhz(), rcc_clock_setup_in_hse_25mhz_out_72mhz(), rcc_clock_setup_in_hse_8mhz_out_24mhz(), rcc_clock_setup_in_hse_8mhz_out_72mhz(), rcc_clock_setup_in_hsi_out_24mhz(), rcc_clock_setup_in_hsi_out_48mhz(), rcc_clock_setup_in_hsi_out_64mhz(), rcc_clock_setup_pll(), rcc_get_i2c_clk_freq(), rcc_get_timer_clk_freq(), and rcc_get_usart_clk_freq().

◆ rcc_apb2_frequency

|

extern |

Definition at line 58 of file rcc.c.

Referenced by rcc_clock_setup_in_hse_12mhz_out_72mhz(), rcc_clock_setup_in_hse_16mhz_out_72mhz(), rcc_clock_setup_in_hse_25mhz_out_72mhz(), rcc_clock_setup_in_hse_8mhz_out_24mhz(), rcc_clock_setup_in_hse_8mhz_out_72mhz(), rcc_clock_setup_in_hsi_out_24mhz(), rcc_clock_setup_in_hsi_out_48mhz(), rcc_clock_setup_in_hsi_out_64mhz(), rcc_clock_setup_pll(), rcc_get_timer_clk_freq(), and rcc_get_usart_clk_freq().

◆ rcc_hse_configs

|

extern |

◆ rcc_hsi_configs

|

extern |