#include <libopencm3/stm32/common/adc_common_v1.h>

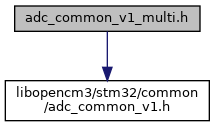

Include dependency graph for adc_common_v1_multi.h:

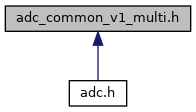

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Macros | |

| #define | ADC_COMMON_REGISTERS_BASE (ADC1_BASE+0x300) |

| #define | ADC_CSR MMIO32(ADC_COMMON_REGISTERS_BASE + 0x0) |

| #define | ADC_CCR MMIO32(ADC_COMMON_REGISTERS_BASE + 0x4) |

| #define | ADC_CDR MMIO32(ADC_COMMON_REGISTERS_BASE + 0x8) |

| #define | ADC_SR_OVR (1 << 5) |

| Overrun. More... | |

| #define | ADC_CR1_OVRIE (1 << 26) |

| #define | ADC_CR1_RES_12BIT (0x0 << 24) |

| #define | ADC_CR1_RES_10BIT (0x1 << 24) |

| #define | ADC_CR1_RES_8BIT (0x2 << 24) |

| #define | ADC_CR1_RES_6BIT (0x3 << 24) |

| #define | ADC_CR1_RES_MASK (0x3 << 24) |

| #define | ADC_CR1_RES_SHIFT 24 |

| #define | ADC_CR2_SWSTART (1 << 30) |

| #define | ADC_CR2_EXTEN_SHIFT 28 |

| #define | ADC_CR2_EXTEN_MASK (0x3 << ADC_CR2_EXTEN_SHIFT) |

| #define | ADC_CR2_EXTEN_DISABLED (0x0 << ADC_CR2_EXTEN_SHIFT) |

| #define | ADC_CR2_EXTEN_RISING_EDGE (0x1 << ADC_CR2_EXTEN_SHIFT) |

| #define | ADC_CR2_EXTEN_FALLING_EDGE (0x2 << ADC_CR2_EXTEN_SHIFT) |

| #define | ADC_CR2_EXTEN_BOTH_EDGES (0x3 << ADC_CR2_EXTEN_SHIFT) |

| #define | ADC_CR2_EXTSEL_MASK (0xF << 24) |

| #define | ADC_CR2_EXTSEL_SHIFT 24 |

| #define | ADC_CR2_JSWSTART (1 << 22) |

| #define | ADC_CR2_JEXTEN_SHIFT 20 |

| #define | ADC_CR2_JEXTEN_MASK (0x3 << ADC_CR2_JEXTEN_SHIFT) |

| #define | ADC_CR2_JEXTEN_DISABLED (0x0 << ADC_CR2_JEXTEN_SHIFT) |

| #define | ADC_CR2_JEXTEN_RISING_EDGE (0x1 << ADC_CR2_JEXTEN_SHIFT) |

| #define | ADC_CR2_JEXTEN_FALLING_EDGE (0x2 << ADC_CR2_JEXTEN_SHIFT) |

| #define | ADC_CR2_JEXTEN_BOTH_EDGES (0x3 << ADC_CR2_JEXTEN_SHIFT) |

| #define | ADC_CR2_JEXTSEL_SHIFT 16 |

| #define | ADC_CR2_JEXTSEL_MASK (0xF << ADC_CR2_JEXTSEL_SHIFT) |

| #define | ADC_CR2_ALIGN_RIGHT (0 << 11) |

| #define | ADC_CR2_ALIGN_LEFT (1 << 11) |

| #define | ADC_CR2_ALIGN (1 << 11) |

| #define | ADC_CR2_EOCS (1 << 10) |

| #define | ADC_CR2_DDS (1 << 9) |

| #define | ADC_CR2_DMA (1 << 8) |

| #define | ADC_CR2_CONT (1 << 1) |

| #define | ADC_CR2_ADON (1 << 0) |

| #define | ADC_SQRx_MASK 0x1f |

| #define | ADC_JDATA_LSB 0 |

| #define | ADC_DATA_LSB 0 |

| #define | ADC_JDATA_MSK (0xffff << ADC_JDATA_LSB) |

| #define | ADC_DATA_MSK (0xffff << ADC_DA) |

| #define | ADC_CSR_OVR3 (1 << 21) |

| #define | ADC_CSR_STRT3 (1 << 20) |

| #define | ADC_CSR_JSTRT3 (1 << 19) |

| #define | ADC_CSR_JEOC3 (1 << 18) |

| #define | ADC_CSR_EOC3 (1 << 17) |

| #define | ADC_CSR_AWD3 (1 << 16) |

| #define | ADC_CSR_OVR2 (1 << 13) |

| #define | ADC_CSR_STRT2 (1 << 12) |

| #define | ADC_CSR_JSTRT2 (1 << 11) |

| #define | ADC_CSR_JEOC2 (1 << 10) |

| #define | ADC_CSR_EOC2 (1 << 9) |

| #define | ADC_CSR_AWD2 (1 << 8) |

| #define | ADC_CSR_OVR1 (1 << 5) |

| #define | ADC_CSR_STRT1 (1 << 4) |

| #define | ADC_CSR_JSTRT1 (1 << 3) |

| #define | ADC_CSR_JEOC1 (1 << 2) |

| #define | ADC_CSR_EOC1 (1 << 1) |

| #define | ADC_CSR_AWD1 (1 << 0) |

| #define | ADC_CCR_TSVREFE (1 << 23) |

| #define | ADC_CCR_VBATE (1 << 22) |

| #define | ADC_CCR_DMA_DISABLE (0x0 << 14) |

| #define | ADC_CCR_DMA_MODE_1 (0x1 << 14) |

| #define | ADC_CCR_DMA_MODE_2 (0x2 << 14) |

| #define | ADC_CCR_DMA_MODE_3 (0x3 << 14) |

| #define | ADC_CCR_DMA_MASK (0x3 << 14) |

| #define | ADC_CCR_DMA_SHIFT 14 |

| #define | ADC_CCR_DDS (1 << 13) |

| #define | ADC_CCR_DELAY_5ADCCLK (0x0 << 8) |

| #define | ADC_CCR_DELAY_6ADCCLK (0x1 << 8) |

| #define | ADC_CCR_DELAY_7ADCCLK (0x2 << 8) |

| #define | ADC_CCR_DELAY_8ADCCLK (0x3 << 8) |

| #define | ADC_CCR_DELAY_9ADCCLK (0x4 << 8) |

| #define | ADC_CCR_DELAY_10ADCCLK (0x5 << 8) |

| #define | ADC_CCR_DELAY_11ADCCLK (0x6 << 8) |

| #define | ADC_CCR_DELAY_12ADCCLK (0x7 << 8) |

| #define | ADC_CCR_DELAY_13ADCCLK (0x8 << 8) |

| #define | ADC_CCR_DELAY_14ADCCLK (0x9 << 8) |

| #define | ADC_CCR_DELAY_15ADCCLK (0xa << 8) |

| #define | ADC_CCR_DELAY_16ADCCLK (0xb << 8) |

| #define | ADC_CCR_DELAY_17ADCCLK (0xc << 8) |

| #define | ADC_CCR_DELAY_18ADCCLK (0xd << 8) |

| #define | ADC_CCR_DELAY_19ADCCLK (0xe << 8) |

| #define | ADC_CCR_DELAY_20ADCCLK (0xf << 8) |

| #define | ADC_CCR_DELAY_MASK (0xf << 8) |

| #define | ADC_CCR_DELAY_SHIFT 8 |

| #define | ADC_CCR_MULTI_INDEPENDENT (0x00 << 0) |

| All ADCs independent. More... | |

| #define | ADC_CCR_MULTI_DUAL_REG_SIMUL_AND_INJECTED_SIMUL (0x01 << 0) |

| Dual modes (ADC1 + ADC2) Combined regular simultaneous + injected simultaneous mode. More... | |

| #define | ADC_CCR_MULTI_DUAL_REG_SIMUL_AND_ALTERNATE_TRIG (0x02 << 0) |

| Dual modes (ADC1 + ADC2) Combined regular simultaneous + alternate trigger mode. More... | |

| #define | ADC_CCR_MULTI_DUAL_INJECTED_SIMUL (0x05 << 0) |

| Dual modes (ADC1 + ADC2) Injected simultaneous mode only. More... | |

| #define | ADC_CCR_MULTI_DUAL_REGULAR_SIMUL (0x06 << 0) |

| Dual modes (ADC1 + ADC2) Regular simultaneous mode only. More... | |

| #define | ADC_CCR_MULTI_DUAL_INTERLEAVED (0x07 << 0) |

| Dual modes (ADC1 + ADC2) Interleaved mode only. More... | |

| #define | ADC_CCR_MULTI_DUAL_ALTERNATE_TRIG (0x09 << 0) |

| Dual modes (ADC1 + ADC2) Alternate trigger mode only. More... | |

| #define | ADC_CCR_MULTI_TRIPLE_REG_SIMUL_AND_INJECTED_SIMUL (0x11 << 0) |

| Triple modes (ADC1 + ADC2 + ADC3) Combined regular simultaneous + injected simultaneous mode. More... | |

| #define | ADC_CCR_MULTI_TRIPLE_REG_SIMUL_AND_ALTERNATE_TRIG (0x12 << 0) |

| Triple modes (ADC1 + ADC2 + ADC3) Combined regular simultaneous + alternate trigger mode. More... | |

| #define | ADC_CCR_MULTI_TRIPLE_INJECTED_SIMUL (0x15 << 0) |

| Triple modes (ADC1 + ADC2 + ADC3) Injected simultaneous mode only. More... | |

| #define | ADC_CCR_MULTI_TRIPLE_REGULAR_SIMUL (0x16 << 0) |

| Triple modes (ADC1 + ADC2 + ADC3) Regular simultaneous mode only. More... | |

| #define | ADC_CCR_MULTI_TRIPLE_INTERLEAVED (0x17 << 0) |

| Triple modes (ADC1 + ADC2 + ADC3) Interleaved mode only. More... | |

| #define | ADC_CCR_MULTI_TRIPLE_ALTERNATE_TRIG (0x19 << 0) |

| Triple modes (ADC1 + ADC2 + ADC3) Alternate trigger mode only. More... | |

| #define | ADC_CCR_MULTI_MASK (0x1f << 0) |

| #define | ADC_CCR_MULTI_SHIFT 0 |

| #define | ADC_CDR_DATA2_MASK (0xffff << 16) |

| #define | ADC_CDR_DATA2_SHIFT 16 |

| #define | ADC_CDR_DATA1_MASK (0xffff << 0) |

| #define | ADC_CDR_DATA1_SHIFT 0 |

Functions | |

| void | adc_set_clk_prescale (uint32_t prescaler) |

| ADC Set Clock Prescale The ADC clock can be prescaled. More... | |

| void | adc_enable_external_trigger_regular (uint32_t adc, uint32_t trigger, uint32_t polarity) |

| ADC Enable an External Trigger for Regular Channels. More... | |

| void | adc_enable_external_trigger_injected (uint32_t adc, uint32_t trigger, uint32_t polarity) |

| ADC Enable an External Trigger for Injected Channels. More... | |

| void | adc_set_resolution (uint32_t adc, uint32_t resolution) |

| ADC Set Resolution. More... | |

| void | adc_enable_overrun_interrupt (uint32_t adc) |

| ADC Enable the Overrun Interrupt. More... | |

| void | adc_disable_overrun_interrupt (uint32_t adc) |

| ADC Disable the Overrun Interrupt. More... | |

| bool | adc_get_overrun_flag (uint32_t adc) |

| ADC Read the Overrun Flag. More... | |

| void | adc_clear_overrun_flag (uint32_t adc) |

| ADC Clear Overrun Flags. More... | |

| bool | adc_awd (uint32_t adc) |

| ADC Read the Analog Watchdog Flag. More... | |

| void | adc_eoc_after_each (uint32_t adc) |

| ADC Enable an EOC for Each Conversion. More... | |

| void | adc_eoc_after_group (uint32_t adc) |

| ADC Disable the EOC for Each Conversion. More... | |

| void | adc_set_dma_continue (uint32_t adc) |

| ADC Set DMA to Continue. More... | |

| void | adc_set_dma_terminate (uint32_t adc) |

| ADC Set DMA to Terminate. More... | |

| void | adc_enable_temperature_sensor (void) |

| ADC Enable The Temperature Sensor. More... | |

| void | adc_disable_temperature_sensor (void) |

| ADC Disable The Temperature Sensor. More... | |