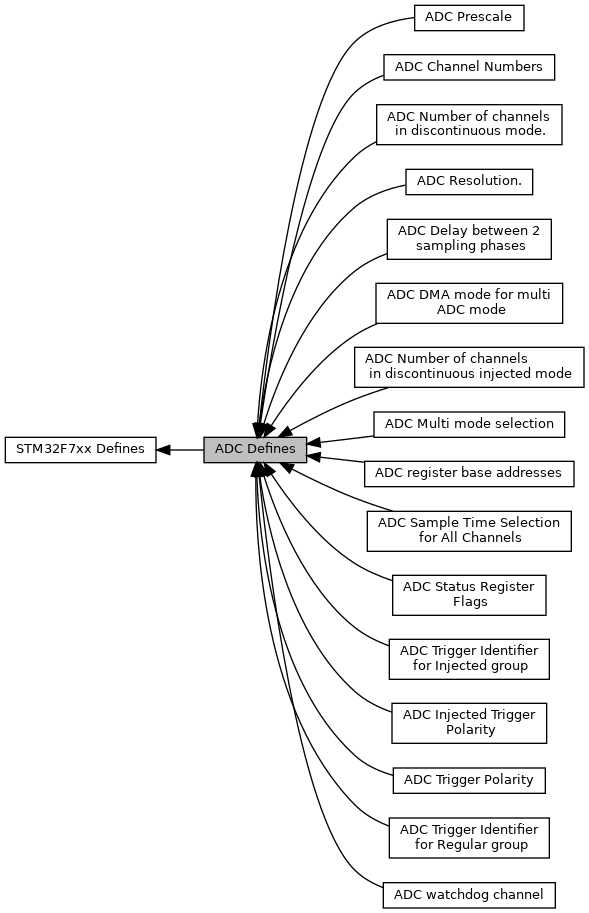

Defined Constants and Types for the STM32F7xx Analog to Digital Converters More...

Macros | |

| #define | ADC_SR(block) MMIO32((block) + 0x00) |

| #define | ADC_CR1(block) MMIO32((block) + 0x04) |

| #define | ADC_CR2(block) MMIO32((block) + 0x08) |

| #define | ADC_SMPR1(block) MMIO32((block) + 0x0c) |

| #define | ADC_SMPR2(block) MMIO32((block) + 0x10) |

| #define | ADC1_SR ADC_SR(ADC1) |

| #define | ADC1_CR1 ADC_CR1(ADC1) |

| #define | ADC1_CR2 ADC_CR2(ADC1) |

| #define | ADC1_SMPR1 ADC_SMPR1(ADC1) |

| #define | ADC1_SMPR2 ADC_SMPR2(ADC1) |

| #define | ADC1_JOFR1 ADC_JOFR1(ADC1) |

| #define | ADC1_JOFR2 ADC_JOFR2(ADC1) |

| #define | ADC1_JOFR3 ADC_JOFR3(ADC1) |

| #define | ADC1_JOFR4 ADC_JOFR4(ADC1) |

| #define | ADC1_HTR ADC_HTR(ADC1) |

| #define | ADC1_LTR ADC_LTR(ADC1) |

| #define | ADC1_SQR1 ADC_SQR1(ADC1) |

| #define | ADC1_SQR2 ADC_SQR2(ADC1) |

| #define | ADC1_SQR3 ADC_SQR3(ADC1) |

| #define | ADC1_JSQR ADC_JSQR(ADC1) |

| #define | ADC1_JDR1 ADC_JDR1(ADC1) |

| #define | ADC1_JDR2 ADC_JDR2(ADC1) |

| #define | ADC1_JDR3 ADC_JDR3(ADC1) |

| #define | ADC1_JDR4 ADC_JDR4(ADC1) |

| #define | ADC1_DR ADC_DR(ADC1) |

| #define | ADC_CHANNEL_MASK 0x1F |

| #define | ADC_CR1_AWDEN (1 << 23) |

| #define | ADC_CR1_JAWDEN (1 << 22) |

| #define | ADC_CR1_DISCNUM_MASK (0x7 << 13) |

| #define | ADC_CR1_DISCNUM_SHIFT 13 |

| #define | ADC_CR1_JDISCEN (1 << 12) |

| Discontinuous mode on injected channels. More... | |

| #define | ADC_CR1_DISCEN (1 << 11) |

| Discontinuous mode on regular channels. More... | |

| #define | ADC_CR1_JAUTO (1 << 10) |

| Automatic Injection Group conversion. More... | |

| #define | ADC_CR1_AWDSGL (1 << 9) |

| Enable the watchdog on a single channel in scan mode. More... | |

| #define | ADC_CR1_SCAN (1 << 8) |

| Scan mode. More... | |

| #define | ADC_CR1_JEOCIE (1 << 7) |

| Interrupt enable for injected channels. More... | |

| #define | ADC_CR1_AWDIE (1 << 6) |

| Analog watchdog interrupt enable. More... | |

| #define | ADC_CR1_EOCIE (1 << 5) |

| Interrupt enable EOC. More... | |

| #define | ADC_CR1_AWDCH_MASK (0x1F << 0) |

| #define | ADC_CR1_AWDCH_SHIFT 0 |

| #define | ADC_CR2_ALIGN_RIGHT (0 << 11) |

| #define | ADC_CR2_ALIGN_LEFT (1 << 11) |

| #define | ADC_CR2_ALIGN (1 << 11) |

| #define | ADC_CR2_DMA (1 << 8) |

| #define | ADC_CR2_CONT (1 << 1) |

| #define | ADC_CR2_ADON (1 << 0) |

| #define | ADC_JOFFSET_LSB 0 |

| #define | ADC_JOFFSET_MSK 0xfff |

| #define | ADC_HT_LSB 0 |

| #define | ADC_HT_MSK 0xfff |

| #define | ADC_LT_LSB 0 |

| #define | ADC_LT_MSK 0xfff |

| #define | ADC_SQR1_L_LSB 20 |

| #define | ADC_JSQR_JL_LSB 20 |

| #define | ADC_JSQR_JSQ4_LSB 15 |

| #define | ADC_JSQR_JSQ3_LSB 10 |

| #define | ADC_JSQR_JSQ2_LSB 5 |

| #define | ADC_JSQR_JSQ1_LSB 0 |

| #define | ADC_JSQR_JL_MSK (0x2 << ADC_JSQR_JL_LSB) |

| #define | ADC_JSQR_JSQ4_MSK (0x1f << ADC_JSQR_JSQ4_LSB) |

| #define | ADC_JSQR_JSQ3_MSK (0x1f << ADC_JSQR_JSQ3_LSB) |

| #define | ADC_JSQR_JSQ2_MSK (0x1f << ADC_JSQR_JSQ2_LSB) |

| #define | ADC_JSQR_JSQ1_MSK (0x1f << ADC_JSQR_JSQ1_LSB) |

| #define | ADC_JSQR_JSQ_VAL(n, val) ((val) << (((n) - 1) * 5)) |

| #define | ADC_JSQR_JL_VAL(val) (((val) - 1) << ADC_JSQR_JL_LSB) |

| #define | ADC_COMMON_REGISTERS_BASE (ADC1_BASE+0x300) |

| #define | ADC_CSR MMIO32(ADC_COMMON_REGISTERS_BASE + 0x0) |

| #define | ADC_CCR MMIO32(ADC_COMMON_REGISTERS_BASE + 0x4) |

| #define | ADC_CDR MMIO32(ADC_COMMON_REGISTERS_BASE + 0x8) |

| #define | ADC_CR1_OVRIE (1 << 26) |

| #define | ADC_CR1_RES_MASK (0x3 << 24) |

| #define | ADC_CR1_RES_SHIFT 24 |

| #define | ADC_CR2_SWSTART (1 << 30) |

| #define | ADC_CR2_EXTEN_SHIFT 28 |

| #define | ADC_CR2_EXTEN_MASK (0x3 << ADC_CR2_EXTEN_SHIFT) |

| #define | ADC_CR2_EXTSEL_MASK (0xF << 24) |

| #define | ADC_CR2_EXTSEL_SHIFT 24 |

| #define | ADC_CR2_JSWSTART (1 << 22) |

| #define | ADC_CR2_JEXTEN_SHIFT 20 |

| #define | ADC_CR2_JEXTEN_MASK (0x3 << ADC_CR2_JEXTEN_SHIFT) |

| #define | ADC_CR2_JEXTSEL_SHIFT 16 |

| #define | ADC_CR2_JEXTSEL_MASK (0xF << ADC_CR2_JEXTSEL_SHIFT) |

| #define | ADC_CR2_ALIGN_RIGHT (0 << 11) |

| #define | ADC_CR2_ALIGN_LEFT (1 << 11) |

| #define | ADC_CR2_ALIGN (1 << 11) |

| #define | ADC_CR2_EOCS (1 << 10) |

| #define | ADC_CR2_DDS (1 << 9) |

| #define | ADC_CR2_DMA (1 << 8) |

| #define | ADC_CR2_CONT (1 << 1) |

| #define | ADC_CR2_ADON (1 << 0) |

| #define | ADC_SQRx_MASK 0x1f |

| #define | ADC_JDATA_LSB 0 |

| #define | ADC_DATA_LSB 0 |

| #define | ADC_JDATA_MSK (0xffff << ADC_JDATA_LSB) |

| #define | ADC_DATA_MSK (0xffff << ADC_DA) |

| #define | ADC_CSR_OVR3 (1 << 21) |

| #define | ADC_CSR_STRT3 (1 << 20) |

| #define | ADC_CSR_JSTRT3 (1 << 19) |

| #define | ADC_CSR_JEOC3 (1 << 18) |

| #define | ADC_CSR_EOC3 (1 << 17) |

| #define | ADC_CSR_AWD3 (1 << 16) |

| #define | ADC_CSR_OVR2 (1 << 13) |

| #define | ADC_CSR_STRT2 (1 << 12) |

| #define | ADC_CSR_JSTRT2 (1 << 11) |

| #define | ADC_CSR_JEOC2 (1 << 10) |

| #define | ADC_CSR_EOC2 (1 << 9) |

| #define | ADC_CSR_AWD2 (1 << 8) |

| #define | ADC_CSR_OVR1 (1 << 5) |

| #define | ADC_CSR_STRT1 (1 << 4) |

| #define | ADC_CSR_JSTRT1 (1 << 3) |

| #define | ADC_CSR_JEOC1 (1 << 2) |

| #define | ADC_CSR_EOC1 (1 << 1) |

| #define | ADC_CSR_AWD1 (1 << 0) |

| #define | ADC_CCR_TSVREFE (1 << 23) |

| #define | ADC_CCR_VBATE (1 << 22) |

| #define | ADC_CCR_DMA_MASK (0x3 << 14) |

| #define | ADC_CCR_DMA_SHIFT 14 |

| #define | ADC_CCR_DDS (1 << 13) |

| #define | ADC_CCR_DELAY_MASK (0xf << 8) |

| #define | ADC_CCR_DELAY_SHIFT 8 |

| #define | ADC_CCR_MULTI_MASK (0x1f << 0) |

| #define | ADC_CCR_MULTI_SHIFT 0 |

| #define | ADC_CDR_DATA2_MASK (0xffff << 16) |

| #define | ADC_CDR_DATA2_SHIFT 16 |

| #define | ADC_CDR_DATA1_MASK (0xffff << 0) |

| #define | ADC_CDR_DATA1_SHIFT 0 |

Functions | |

| void | adc_power_on (uint32_t adc) |

| ADC Power On. More... | |

| void | adc_power_off (uint32_t adc) |

| ADC Off. More... | |

| void | adc_enable_analog_watchdog_regular (uint32_t adc) |

| ADC Enable Analog Watchdog for Regular Conversions. More... | |

| void | adc_disable_analog_watchdog_regular (uint32_t adc) |

| ADC Disable Analog Watchdog for Regular Conversions. More... | |

| void | adc_enable_analog_watchdog_injected (uint32_t adc) |

| ADC Enable Analog Watchdog for Injected Conversions. More... | |

| void | adc_disable_analog_watchdog_injected (uint32_t adc) |

| ADC Disable Analog Watchdog for Injected Conversions. More... | |

| void | adc_enable_discontinuous_mode_regular (uint32_t adc, uint8_t length) |

| ADC Enable Discontinuous Mode for Regular Conversions. More... | |

| void | adc_disable_discontinuous_mode_regular (uint32_t adc) |

| ADC Disable Discontinuous Mode for Regular Conversions. More... | |

| void | adc_enable_discontinuous_mode_injected (uint32_t adc) |

| ADC Enable Discontinuous Mode for Injected Conversions. More... | |

| void | adc_disable_discontinuous_mode_injected (uint32_t adc) |

| ADC Disable Discontinuous Mode for Injected Conversions. More... | |

| void | adc_enable_automatic_injected_group_conversion (uint32_t adc) |

| ADC Enable Automatic Injected Conversions. More... | |

| void | adc_disable_automatic_injected_group_conversion (uint32_t adc) |

| ADC Disable Automatic Injected Conversions. More... | |

| void | adc_enable_analog_watchdog_on_all_channels (uint32_t adc) |

| ADC Enable Analog Watchdog for All Regular and/or Injected Channels. More... | |

| void | adc_enable_analog_watchdog_on_selected_channel (uint32_t adc, uint8_t channel) |

| ADC Enable Analog Watchdog for a Selected Channel. More... | |

| void | adc_enable_scan_mode (uint32_t adc) |

| ADC Set Scan Mode. More... | |

| void | adc_disable_scan_mode (uint32_t adc) |

| ADC Disable Scan Mode. More... | |

| void | adc_enable_eoc_interrupt_injected (uint32_t adc) |

| ADC Enable Injected End-Of-Conversion Interrupt. More... | |

| void | adc_disable_eoc_interrupt_injected (uint32_t adc) |

| ADC Disable Injected End-Of-Conversion Interrupt. More... | |

| void | adc_enable_awd_interrupt (uint32_t adc) |

| ADC Enable Analog Watchdog Interrupt. More... | |

| void | adc_disable_awd_interrupt (uint32_t adc) |

| ADC Disable Analog Watchdog Interrupt. More... | |

| void | adc_enable_eoc_interrupt (uint32_t adc) |

| ADC Enable Regular End-Of-Conversion Interrupt. More... | |

| void | adc_disable_eoc_interrupt (uint32_t adc) |

| ADC Disable Regular End-Of-Conversion Interrupt. More... | |

| void | adc_set_left_aligned (uint32_t adc) |

| ADC Set the Data as Left Aligned. More... | |

| void | adc_set_right_aligned (uint32_t adc) |

| ADC Set the Data as Right Aligned. More... | |

| bool | adc_eoc (uint32_t adc) |

| ADC Read the End-of-Conversion Flag. More... | |

| bool | adc_eoc_injected (uint32_t adc) |

| ADC Read the End-of-Conversion Flag for Injected Conversion. More... | |

| uint32_t | adc_read_regular (uint32_t adc) |

| ADC Read from the Regular Conversion Result Register. More... | |

| uint32_t | adc_read_injected (uint32_t adc, uint8_t reg) |

| ADC Read from an Injected Conversion Result Register. More... | |

| void | adc_set_continuous_conversion_mode (uint32_t adc) |

| ADC Enable Continuous Conversion Mode. More... | |

| void | adc_set_single_conversion_mode (uint32_t adc) |

| ADC Enable Single Conversion Mode. More... | |

| void | adc_set_regular_sequence (uint32_t adc, uint8_t length, uint8_t channel[]) |

| ADC Set a Regular Channel Conversion Sequence. More... | |

| void | adc_set_injected_sequence (uint32_t adc, uint8_t length, uint8_t channel[]) |

| ADC Set an Injected Channel Conversion Sequence. More... | |

| void | adc_set_injected_offset (uint32_t adc, uint8_t reg, uint32_t offset) |

| ADC Set the Injected Channel Data Offset. More... | |

| void | adc_set_watchdog_high_threshold (uint32_t adc, uint16_t threshold) |

| ADC Set Analog Watchdog Upper Threshold. More... | |

| void | adc_set_watchdog_low_threshold (uint32_t adc, uint16_t threshold) |

| ADC Set Analog Watchdog Lower Threshold. More... | |

| void | adc_start_conversion_regular (uint32_t adc) |

| ADC Software Triggered Conversion on Regular Channels. More... | |

| void | adc_start_conversion_injected (uint32_t adc) |

| ADC Software Triggered Conversion on Injected Channels. More... | |

| void | adc_enable_dma (uint32_t adc) |

| ADC Enable DMA Transfers. More... | |

| void | adc_disable_dma (uint32_t adc) |

| ADC Disable DMA Transfers. More... | |

| bool | adc_get_flag (uint32_t adc, uint32_t flag) |

| Read a Status Flag. More... | |

| void | adc_clear_flag (uint32_t adc, uint32_t flag) |

| Clear a Status Flag. More... | |

| void | adc_set_sample_time (uint32_t adc, uint8_t channel, uint8_t time) |

| ADC Set the Sample Time for a Single Channel. More... | |

| void | adc_set_sample_time_on_all_channels (uint32_t adc, uint8_t time) |

| ADC Set the Sample Time for All Channels. More... | |

| void | adc_disable_external_trigger_regular (uint32_t adc) |

| ADC Disable an External Trigger for Regular Channels. More... | |

| void | adc_disable_external_trigger_injected (uint32_t adc) |

| ADC Disable an External Trigger for Injected Channels. More... | |

| void | adc_set_clk_prescale (uint32_t prescaler) |

| ADC Set Clock Prescale The ADC clock can be prescaled. More... | |

| void | adc_enable_external_trigger_regular (uint32_t adc, uint32_t trigger, uint32_t polarity) |

| ADC Enable an External Trigger for Regular Channels. More... | |

| void | adc_enable_external_trigger_injected (uint32_t adc, uint32_t trigger, uint32_t polarity) |

| ADC Enable an External Trigger for Injected Channels. More... | |

| void | adc_set_resolution (uint32_t adc, uint32_t resolution) |

| ADC Set Resolution. More... | |

| void | adc_enable_overrun_interrupt (uint32_t adc) |

| ADC Enable the Overrun Interrupt. More... | |

| void | adc_disable_overrun_interrupt (uint32_t adc) |

| ADC Disable the Overrun Interrupt. More... | |

| bool | adc_get_overrun_flag (uint32_t adc) |

| ADC Read the Overrun Flag. More... | |

| void | adc_clear_overrun_flag (uint32_t adc) |

| ADC Clear Overrun Flags. More... | |

| bool | adc_awd (uint32_t adc) |

| ADC Read the Analog Watchdog Flag. More... | |

| void | adc_eoc_after_each (uint32_t adc) |

| ADC Enable an EOC for Each Conversion. More... | |

| void | adc_eoc_after_group (uint32_t adc) |

| ADC Disable the EOC for Each Conversion. More... | |

| void | adc_set_dma_continue (uint32_t adc) |

| ADC Set DMA to Continue. More... | |

| void | adc_set_dma_terminate (uint32_t adc) |

| ADC Set DMA to Terminate. More... | |

| void | adc_enable_temperature_sensor (void) |

| ADC Enable The Temperature Sensor. More... | |

| void | adc_disable_temperature_sensor (void) |

| ADC Disable The Temperature Sensor. More... | |

Detailed Description

Defined Constants and Types for the STM32F7xx Analog to Digital Converters

- Version

- 1.0.0

- Date

- 31 August 2012

LGPL License Terms libopencm3 License

Macro Definition Documentation

◆ ADC1_CR1

Definition at line 67 of file adc_common_v1.h.

◆ ADC1_CR2

Definition at line 68 of file adc_common_v1.h.

◆ ADC1_DR

Definition at line 89 of file adc_common_v1.h.

◆ ADC1_HTR

Definition at line 77 of file adc_common_v1.h.

◆ ADC1_JDR1

Definition at line 85 of file adc_common_v1.h.

◆ ADC1_JDR2

Definition at line 86 of file adc_common_v1.h.

◆ ADC1_JDR3

Definition at line 87 of file adc_common_v1.h.

◆ ADC1_JDR4

Definition at line 88 of file adc_common_v1.h.

◆ ADC1_JOFR1

Definition at line 72 of file adc_common_v1.h.

◆ ADC1_JOFR2

Definition at line 73 of file adc_common_v1.h.

◆ ADC1_JOFR3

Definition at line 74 of file adc_common_v1.h.

◆ ADC1_JOFR4

Definition at line 75 of file adc_common_v1.h.

◆ ADC1_JSQR

Definition at line 83 of file adc_common_v1.h.

◆ ADC1_LTR

Definition at line 78 of file adc_common_v1.h.

◆ ADC1_SMPR1

Definition at line 69 of file adc_common_v1.h.

◆ ADC1_SMPR2

Definition at line 70 of file adc_common_v1.h.

◆ ADC1_SQR1

Definition at line 80 of file adc_common_v1.h.

◆ ADC1_SQR2

Definition at line 81 of file adc_common_v1.h.

◆ ADC1_SQR3

Definition at line 82 of file adc_common_v1.h.

◆ ADC1_SR

Definition at line 66 of file adc_common_v1.h.

◆ ADC_CCR

| #define ADC_CCR MMIO32(ADC_COMMON_REGISTERS_BASE + 0x4) |

Definition at line 47 of file adc_common_v1_multi.h.

◆ ADC_CCR_DDS

| #define ADC_CCR_DDS (1 << 13) |

Definition at line 259 of file adc_common_v1_multi.h.

◆ ADC_CCR_DELAY_MASK

| #define ADC_CCR_DELAY_MASK (0xf << 8) |

Definition at line 286 of file adc_common_v1_multi.h.

◆ ADC_CCR_DELAY_SHIFT

| #define ADC_CCR_DELAY_SHIFT 8 |

Definition at line 287 of file adc_common_v1_multi.h.

◆ ADC_CCR_DMA_MASK

| #define ADC_CCR_DMA_MASK (0x3 << 14) |

Definition at line 255 of file adc_common_v1_multi.h.

◆ ADC_CCR_DMA_SHIFT

| #define ADC_CCR_DMA_SHIFT 14 |

Definition at line 256 of file adc_common_v1_multi.h.

◆ ADC_CCR_MULTI_MASK

| #define ADC_CCR_MULTI_MASK (0x1f << 0) |

Definition at line 342 of file adc_common_v1_multi.h.

◆ ADC_CCR_MULTI_SHIFT

| #define ADC_CCR_MULTI_SHIFT 0 |

Definition at line 343 of file adc_common_v1_multi.h.

◆ ADC_CCR_TSVREFE

| #define ADC_CCR_TSVREFE (1 << 23) |

Definition at line 237 of file adc_common_v1_multi.h.

◆ ADC_CCR_VBATE

| #define ADC_CCR_VBATE (1 << 22) |

Definition at line 240 of file adc_common_v1_multi.h.

◆ ADC_CDR

| #define ADC_CDR MMIO32(ADC_COMMON_REGISTERS_BASE + 0x8) |

Definition at line 48 of file adc_common_v1_multi.h.

◆ ADC_CDR_DATA1_MASK

| #define ADC_CDR_DATA1_MASK (0xffff << 0) |

Definition at line 350 of file adc_common_v1_multi.h.

◆ ADC_CDR_DATA1_SHIFT

| #define ADC_CDR_DATA1_SHIFT 0 |

Definition at line 351 of file adc_common_v1_multi.h.

◆ ADC_CDR_DATA2_MASK

| #define ADC_CDR_DATA2_MASK (0xffff << 16) |

Definition at line 347 of file adc_common_v1_multi.h.

◆ ADC_CDR_DATA2_SHIFT

| #define ADC_CDR_DATA2_SHIFT 16 |

Definition at line 348 of file adc_common_v1_multi.h.

◆ ADC_CHANNEL_MASK

| #define ADC_CHANNEL_MASK 0x1F |

Definition at line 184 of file adc_common_v1.h.

◆ ADC_COMMON_REGISTERS_BASE

| #define ADC_COMMON_REGISTERS_BASE (ADC1_BASE+0x300) |

Definition at line 45 of file adc_common_v1_multi.h.

◆ ADC_CR1

| #define ADC_CR1 | ( | block | ) | MMIO32((block) + 0x04) |

Definition at line 55 of file adc_common_v1.h.

◆ ADC_CR1_AWDCH_MASK

| #define ADC_CR1_AWDCH_MASK (0x1F << 0) |

Definition at line 292 of file adc_common_v1.h.

◆ ADC_CR1_AWDCH_SHIFT

| #define ADC_CR1_AWDCH_SHIFT 0 |

Definition at line 293 of file adc_common_v1.h.

◆ ADC_CR1_AWDEN

| #define ADC_CR1_AWDEN (1 << 23) |

Definition at line 213 of file adc_common_v1.h.

◆ ADC_CR1_AWDIE

| #define ADC_CR1_AWDIE (1 << 6) |

Analog watchdog interrupt enable.

Definition at line 258 of file adc_common_v1.h.

◆ ADC_CR1_AWDSGL

| #define ADC_CR1_AWDSGL (1 << 9) |

Enable the watchdog on a single channel in scan mode.

Definition at line 249 of file adc_common_v1.h.

◆ ADC_CR1_DISCEN

| #define ADC_CR1_DISCEN (1 << 11) |

Discontinuous mode on regular channels.

Definition at line 243 of file adc_common_v1.h.

◆ ADC_CR1_DISCNUM_MASK

| #define ADC_CR1_DISCNUM_MASK (0x7 << 13) |

Definition at line 236 of file adc_common_v1.h.

◆ ADC_CR1_DISCNUM_SHIFT

| #define ADC_CR1_DISCNUM_SHIFT 13 |

Definition at line 237 of file adc_common_v1.h.

◆ ADC_CR1_EOCIE

| #define ADC_CR1_EOCIE (1 << 5) |

Interrupt enable EOC.

Definition at line 261 of file adc_common_v1.h.

◆ ADC_CR1_JAUTO

| #define ADC_CR1_JAUTO (1 << 10) |

Automatic Injection Group conversion.

Definition at line 246 of file adc_common_v1.h.

◆ ADC_CR1_JAWDEN

| #define ADC_CR1_JAWDEN (1 << 22) |

Definition at line 216 of file adc_common_v1.h.

◆ ADC_CR1_JDISCEN

| #define ADC_CR1_JDISCEN (1 << 12) |

Discontinuous mode on injected channels.

Definition at line 240 of file adc_common_v1.h.

◆ ADC_CR1_JEOCIE

| #define ADC_CR1_JEOCIE (1 << 7) |

Interrupt enable for injected channels.

Definition at line 255 of file adc_common_v1.h.

◆ ADC_CR1_OVRIE

| #define ADC_CR1_OVRIE (1 << 26) |

Definition at line 64 of file adc_common_v1_multi.h.

◆ ADC_CR1_RES_MASK

| #define ADC_CR1_RES_MASK (0x3 << 24) |

Definition at line 77 of file adc_common_v1_multi.h.

◆ ADC_CR1_RES_SHIFT

| #define ADC_CR1_RES_SHIFT 24 |

Definition at line 78 of file adc_common_v1_multi.h.

◆ ADC_CR1_SCAN

| #define ADC_CR1_SCAN (1 << 8) |

Scan mode.

Definition at line 252 of file adc_common_v1.h.

◆ ADC_CR2

| #define ADC_CR2 | ( | block | ) | MMIO32((block) + 0x08) |

Definition at line 58 of file adc_common_v1.h.

◆ ADC_CR2_ADON [1/2]

| #define ADC_CR2_ADON (1 << 0) |

Definition at line 314 of file adc_common_v1.h.

◆ ADC_CR2_ADON [2/2]

| #define ADC_CR2_ADON (1 << 0) |

Definition at line 157 of file adc_common_v1_multi.h.

◆ ADC_CR2_ALIGN [1/2]

| #define ADC_CR2_ALIGN (1 << 11) |

Definition at line 300 of file adc_common_v1.h.

◆ ADC_CR2_ALIGN [2/2]

| #define ADC_CR2_ALIGN (1 << 11) |

Definition at line 135 of file adc_common_v1_multi.h.

◆ ADC_CR2_ALIGN_LEFT [1/2]

| #define ADC_CR2_ALIGN_LEFT (1 << 11) |

Definition at line 299 of file adc_common_v1.h.

◆ ADC_CR2_ALIGN_LEFT [2/2]

| #define ADC_CR2_ALIGN_LEFT (1 << 11) |

Definition at line 134 of file adc_common_v1_multi.h.

◆ ADC_CR2_ALIGN_RIGHT [1/2]

| #define ADC_CR2_ALIGN_RIGHT (0 << 11) |

Definition at line 298 of file adc_common_v1.h.

◆ ADC_CR2_ALIGN_RIGHT [2/2]

| #define ADC_CR2_ALIGN_RIGHT (0 << 11) |

Definition at line 133 of file adc_common_v1_multi.h.

◆ ADC_CR2_CONT [1/2]

| #define ADC_CR2_CONT (1 << 1) |

Definition at line 306 of file adc_common_v1.h.

◆ ADC_CR2_CONT [2/2]

| #define ADC_CR2_CONT (1 << 1) |

Definition at line 149 of file adc_common_v1_multi.h.

◆ ADC_CR2_DDS

| #define ADC_CR2_DDS (1 << 9) |

Definition at line 141 of file adc_common_v1_multi.h.

◆ ADC_CR2_DMA [1/2]

| #define ADC_CR2_DMA (1 << 8) |

Definition at line 303 of file adc_common_v1.h.

◆ ADC_CR2_DMA [2/2]

| #define ADC_CR2_DMA (1 << 8) |

Definition at line 144 of file adc_common_v1_multi.h.

◆ ADC_CR2_EOCS

| #define ADC_CR2_EOCS (1 << 10) |

Definition at line 138 of file adc_common_v1_multi.h.

◆ ADC_CR2_EXTEN_MASK

| #define ADC_CR2_EXTEN_MASK (0x3 << ADC_CR2_EXTEN_SHIFT) |

Definition at line 92 of file adc_common_v1_multi.h.

◆ ADC_CR2_EXTEN_SHIFT

| #define ADC_CR2_EXTEN_SHIFT 28 |

Definition at line 91 of file adc_common_v1_multi.h.

◆ ADC_CR2_EXTSEL_MASK

| #define ADC_CR2_EXTSEL_MASK (0xF << 24) |

Definition at line 105 of file adc_common_v1_multi.h.

◆ ADC_CR2_EXTSEL_SHIFT

| #define ADC_CR2_EXTSEL_SHIFT 24 |

Definition at line 106 of file adc_common_v1_multi.h.

◆ ADC_CR2_JEXTEN_MASK

| #define ADC_CR2_JEXTEN_MASK (0x3 << ADC_CR2_JEXTEN_SHIFT) |

Definition at line 116 of file adc_common_v1_multi.h.

◆ ADC_CR2_JEXTEN_SHIFT

| #define ADC_CR2_JEXTEN_SHIFT 20 |

Definition at line 115 of file adc_common_v1_multi.h.

◆ ADC_CR2_JEXTSEL_MASK

| #define ADC_CR2_JEXTSEL_MASK (0xF << ADC_CR2_JEXTSEL_SHIFT) |

Definition at line 130 of file adc_common_v1_multi.h.

◆ ADC_CR2_JEXTSEL_SHIFT

| #define ADC_CR2_JEXTSEL_SHIFT 16 |

Definition at line 129 of file adc_common_v1_multi.h.

◆ ADC_CR2_JSWSTART

| #define ADC_CR2_JSWSTART (1 << 22) |

Definition at line 111 of file adc_common_v1_multi.h.

◆ ADC_CR2_SWSTART

| #define ADC_CR2_SWSTART (1 << 30) |

Definition at line 87 of file adc_common_v1_multi.h.

◆ ADC_CSR

| #define ADC_CSR MMIO32(ADC_COMMON_REGISTERS_BASE + 0x0) |

Definition at line 46 of file adc_common_v1_multi.h.

◆ ADC_CSR_AWD1

| #define ADC_CSR_AWD1 (1 << 0) |

Definition at line 232 of file adc_common_v1_multi.h.

◆ ADC_CSR_AWD2

| #define ADC_CSR_AWD2 (1 << 8) |

Definition at line 212 of file adc_common_v1_multi.h.

◆ ADC_CSR_AWD3

| #define ADC_CSR_AWD3 (1 << 16) |

Definition at line 192 of file adc_common_v1_multi.h.

◆ ADC_CSR_EOC1

| #define ADC_CSR_EOC1 (1 << 1) |

Definition at line 229 of file adc_common_v1_multi.h.

◆ ADC_CSR_EOC2

| #define ADC_CSR_EOC2 (1 << 9) |

Definition at line 209 of file adc_common_v1_multi.h.

◆ ADC_CSR_EOC3

| #define ADC_CSR_EOC3 (1 << 17) |

Definition at line 189 of file adc_common_v1_multi.h.

◆ ADC_CSR_JEOC1

| #define ADC_CSR_JEOC1 (1 << 2) |

Definition at line 226 of file adc_common_v1_multi.h.

◆ ADC_CSR_JEOC2

| #define ADC_CSR_JEOC2 (1 << 10) |

Definition at line 206 of file adc_common_v1_multi.h.

◆ ADC_CSR_JEOC3

| #define ADC_CSR_JEOC3 (1 << 18) |

Definition at line 186 of file adc_common_v1_multi.h.

◆ ADC_CSR_JSTRT1

| #define ADC_CSR_JSTRT1 (1 << 3) |

Definition at line 223 of file adc_common_v1_multi.h.

◆ ADC_CSR_JSTRT2

| #define ADC_CSR_JSTRT2 (1 << 11) |

Definition at line 203 of file adc_common_v1_multi.h.

◆ ADC_CSR_JSTRT3

| #define ADC_CSR_JSTRT3 (1 << 19) |

Definition at line 183 of file adc_common_v1_multi.h.

◆ ADC_CSR_OVR1

| #define ADC_CSR_OVR1 (1 << 5) |

Definition at line 217 of file adc_common_v1_multi.h.

◆ ADC_CSR_OVR2

| #define ADC_CSR_OVR2 (1 << 13) |

Definition at line 197 of file adc_common_v1_multi.h.

◆ ADC_CSR_OVR3

| #define ADC_CSR_OVR3 (1 << 21) |

Definition at line 177 of file adc_common_v1_multi.h.

◆ ADC_CSR_STRT1

| #define ADC_CSR_STRT1 (1 << 4) |

Definition at line 220 of file adc_common_v1_multi.h.

◆ ADC_CSR_STRT2

| #define ADC_CSR_STRT2 (1 << 12) |

Definition at line 200 of file adc_common_v1_multi.h.

◆ ADC_CSR_STRT3

| #define ADC_CSR_STRT3 (1 << 20) |

Definition at line 180 of file adc_common_v1_multi.h.

◆ ADC_DATA_LSB

| #define ADC_DATA_LSB 0 |

Definition at line 168 of file adc_common_v1_multi.h.

◆ ADC_DATA_MSK

| #define ADC_DATA_MSK (0xffff << ADC_DA) |

Definition at line 170 of file adc_common_v1_multi.h.

◆ ADC_HT_LSB

| #define ADC_HT_LSB 0 |

Definition at line 320 of file adc_common_v1.h.

◆ ADC_HT_MSK

| #define ADC_HT_MSK 0xfff |

Definition at line 321 of file adc_common_v1.h.

◆ ADC_JDATA_LSB

| #define ADC_JDATA_LSB 0 |

Definition at line 167 of file adc_common_v1_multi.h.

◆ ADC_JDATA_MSK

| #define ADC_JDATA_MSK (0xffff << ADC_JDATA_LSB) |

Definition at line 169 of file adc_common_v1_multi.h.

◆ ADC_JOFFSET_LSB

| #define ADC_JOFFSET_LSB 0 |

Definition at line 318 of file adc_common_v1.h.

◆ ADC_JOFFSET_MSK

| #define ADC_JOFFSET_MSK 0xfff |

Definition at line 319 of file adc_common_v1.h.

◆ ADC_JSQR_JL_LSB

| #define ADC_JSQR_JL_LSB 20 |

Definition at line 331 of file adc_common_v1.h.

◆ ADC_JSQR_JL_MSK

| #define ADC_JSQR_JL_MSK (0x2 << ADC_JSQR_JL_LSB) |

Definition at line 348 of file adc_common_v1.h.

◆ ADC_JSQR_JL_VAL

| #define ADC_JSQR_JL_VAL | ( | val | ) | (((val) - 1) << ADC_JSQR_JL_LSB) |

Definition at line 355 of file adc_common_v1.h.

◆ ADC_JSQR_JSQ1_LSB

| #define ADC_JSQR_JSQ1_LSB 0 |

Definition at line 335 of file adc_common_v1.h.

◆ ADC_JSQR_JSQ1_MSK

| #define ADC_JSQR_JSQ1_MSK (0x1f << ADC_JSQR_JSQ1_LSB) |

Definition at line 352 of file adc_common_v1.h.

◆ ADC_JSQR_JSQ2_LSB

| #define ADC_JSQR_JSQ2_LSB 5 |

Definition at line 334 of file adc_common_v1.h.

◆ ADC_JSQR_JSQ2_MSK

| #define ADC_JSQR_JSQ2_MSK (0x1f << ADC_JSQR_JSQ2_LSB) |

Definition at line 351 of file adc_common_v1.h.

◆ ADC_JSQR_JSQ3_LSB

| #define ADC_JSQR_JSQ3_LSB 10 |

Definition at line 333 of file adc_common_v1.h.

◆ ADC_JSQR_JSQ3_MSK

| #define ADC_JSQR_JSQ3_MSK (0x1f << ADC_JSQR_JSQ3_LSB) |

Definition at line 350 of file adc_common_v1.h.

◆ ADC_JSQR_JSQ4_LSB

| #define ADC_JSQR_JSQ4_LSB 15 |

Definition at line 332 of file adc_common_v1.h.

◆ ADC_JSQR_JSQ4_MSK

| #define ADC_JSQR_JSQ4_MSK (0x1f << ADC_JSQR_JSQ4_LSB) |

Definition at line 349 of file adc_common_v1.h.

◆ ADC_JSQR_JSQ_VAL

| #define ADC_JSQR_JSQ_VAL | ( | n, | |

| val | |||

| ) | ((val) << (((n) - 1) * 5)) |

Definition at line 354 of file adc_common_v1.h.

◆ ADC_LT_LSB

| #define ADC_LT_LSB 0 |

Definition at line 322 of file adc_common_v1.h.

◆ ADC_LT_MSK

| #define ADC_LT_MSK 0xfff |

Definition at line 323 of file adc_common_v1.h.

◆ ADC_SMPR1

| #define ADC_SMPR1 | ( | block | ) | MMIO32((block) + 0x0c) |

Definition at line 61 of file adc_common_v1.h.

◆ ADC_SMPR2

| #define ADC_SMPR2 | ( | block | ) | MMIO32((block) + 0x10) |

Definition at line 64 of file adc_common_v1.h.

◆ ADC_SQR1_L_LSB

| #define ADC_SQR1_L_LSB 20 |

Definition at line 328 of file adc_common_v1.h.

◆ ADC_SQRx_MASK

| #define ADC_SQRx_MASK 0x1f |

Definition at line 163 of file adc_common_v1_multi.h.

◆ ADC_SR

| #define ADC_SR | ( | block | ) | MMIO32((block) + 0x00) |

Definition at line 52 of file adc_common_v1.h.

Function Documentation

◆ adc_awd()

| bool adc_awd | ( | uint32_t | adc | ) |

ADC Read the Analog Watchdog Flag.

This flag is set when the converted voltage crosses the high or low thresholds.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

- Returns

- bool. AWD flag.

Definition at line 329 of file adc_common_v1_multi.c.

References ADC_SR, and ADC_SR_AWD.

◆ adc_clear_flag()

| void adc_clear_flag | ( | uint32_t | adc, |

| uint32_t | flag | ||

| ) |

Clear a Status Flag.

- Parameters

-

[in] adc Unsigned int32. ADC register address base ADC register base addresses [in] flag Unsigned int32. Status register flag ADC Status Register Flags.

Definition at line 771 of file adc_common_v1.c.

References ADC_SR.

◆ adc_clear_overrun_flag()

| void adc_clear_overrun_flag | ( | uint32_t | adc | ) |

ADC Clear Overrun Flags.

The overrun flag is cleared. Note that if an overrun occurs, DMA is terminated. The flag must be cleared and the DMA stream and ADC reinitialised to resume conversions (see the reference manual).

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

- Returns

- Unsigned int32 conversion result.

Definition at line 259 of file adc_common_v1_multi.c.

References ADC_SR.

◆ adc_disable_analog_watchdog_injected()

| void adc_disable_analog_watchdog_injected | ( | uint32_t | adc | ) |

ADC Disable Analog Watchdog for Injected Conversions.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 161 of file adc_common_v1.c.

References ADC_CR1.

◆ adc_disable_analog_watchdog_regular()

| void adc_disable_analog_watchdog_regular | ( | uint32_t | adc | ) |

ADC Disable Analog Watchdog for Regular Conversions.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses.

Definition at line 135 of file adc_common_v1.c.

References ADC_CR1.

◆ adc_disable_automatic_injected_group_conversion()

| void adc_disable_automatic_injected_group_conversion | ( | uint32_t | adc | ) |

ADC Disable Automatic Injected Conversions.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 251 of file adc_common_v1.c.

References ADC_CR1.

◆ adc_disable_awd_interrupt()

| void adc_disable_awd_interrupt | ( | uint32_t | adc | ) |

ADC Disable Analog Watchdog Interrupt.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 372 of file adc_common_v1.c.

References ADC_CR1.

◆ adc_disable_discontinuous_mode_injected()

| void adc_disable_discontinuous_mode_injected | ( | uint32_t | adc | ) |

ADC Disable Discontinuous Mode for Injected Conversions.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 223 of file adc_common_v1.c.

References ADC_CR1.

◆ adc_disable_discontinuous_mode_regular()

| void adc_disable_discontinuous_mode_regular | ( | uint32_t | adc | ) |

ADC Disable Discontinuous Mode for Regular Conversions.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 197 of file adc_common_v1.c.

References ADC_CR1.

◆ adc_disable_dma()

| void adc_disable_dma | ( | uint32_t | adc | ) |

ADC Disable DMA Transfers.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 746 of file adc_common_v1.c.

References ADC_CR2.

◆ adc_disable_eoc_interrupt()

| void adc_disable_eoc_interrupt | ( | uint32_t | adc | ) |

ADC Disable Regular End-Of-Conversion Interrupt.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 395 of file adc_common_v1.c.

References ADC_CR1.

◆ adc_disable_eoc_interrupt_injected()

| void adc_disable_eoc_interrupt_injected | ( | uint32_t | adc | ) |

ADC Disable Injected End-Of-Conversion Interrupt.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 350 of file adc_common_v1.c.

References ADC_CR1.

◆ adc_disable_external_trigger_injected()

| void adc_disable_external_trigger_injected | ( | uint32_t | adc | ) |

ADC Disable an External Trigger for Injected Channels.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 182 of file adc_common_v1_multi.c.

References ADC_CR2.

Referenced by adc_enable_automatic_injected_group_conversion().

◆ adc_disable_external_trigger_regular()

| void adc_disable_external_trigger_regular | ( | uint32_t | adc | ) |

ADC Disable an External Trigger for Regular Channels.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 149 of file adc_common_v1_multi.c.

References ADC_CR2.

◆ adc_disable_overrun_interrupt()

| void adc_disable_overrun_interrupt | ( | uint32_t | adc | ) |

ADC Disable the Overrun Interrupt.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 227 of file adc_common_v1_multi.c.

References ADC_CR1.

◆ adc_disable_scan_mode()

| void adc_disable_scan_mode | ( | uint32_t | adc | ) |

ADC Disable Scan Mode.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 328 of file adc_common_v1.c.

References ADC_CR1.

◆ adc_disable_temperature_sensor()

| void adc_disable_temperature_sensor | ( | void | ) |

ADC Disable The Temperature Sensor.

Disabling this will reduce power consumption from the sensor and the reference voltage measurements.

Definition at line 355 of file adc_common_v1_multi.c.

References ADC_CCR.

◆ adc_enable_analog_watchdog_injected()

| void adc_enable_analog_watchdog_injected | ( | uint32_t | adc | ) |

ADC Enable Analog Watchdog for Injected Conversions.

The analog watchdog allows the monitoring of an analog signal between two threshold levels. The thresholds must be preset. Comparison is done before data alignment takes place, so the thresholds are left-aligned.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 150 of file adc_common_v1.c.

References ADC_CR1, and ADC_CR1_JAWDEN.

◆ adc_enable_analog_watchdog_on_all_channels()

| void adc_enable_analog_watchdog_on_all_channels | ( | uint32_t | adc | ) |

ADC Enable Analog Watchdog for All Regular and/or Injected Channels.

The analog watchdog allows the monitoring of an analog signal between two threshold levels. The thresholds must be preset. Comparison is done before data alignment takes place, so the thresholds are left-aligned.

- Note

- The analog watchdog must be enabled for either or both of the regular or injected channels. If neither are enabled, the analog watchdog feature will be disabled. adc_enable_analog_watchdog_injected, adc_enable_analog_watchdog_regular.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 272 of file adc_common_v1.c.

References ADC_CR1.

◆ adc_enable_analog_watchdog_on_selected_channel()

| void adc_enable_analog_watchdog_on_selected_channel | ( | uint32_t | adc, |

| uint8_t | channel | ||

| ) |

ADC Enable Analog Watchdog for a Selected Channel.

The analog watchdog allows the monitoring of an analog signal between two threshold levels. The thresholds must be preset. Comparison is done before data alignment takes place, so the thresholds are left-aligned.

- Note

- The analog watchdog must be enabled for either or both of the regular or injected channels. If neither are enabled, the analog watchdog feature will be disabled. If both are enabled, the same channel number is monitored. adc_enable_analog_watchdog_injected, adc_enable_analog_watchdog_regular.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses [in] channel Unsigned int8. ADC channel number ADC watchdog channel

Definition at line 294 of file adc_common_v1.c.

References ADC_CR1, ADC_CR1_AWDCH_MAX, and ADC_CR1_AWDSGL.

◆ adc_enable_analog_watchdog_regular()

| void adc_enable_analog_watchdog_regular | ( | uint32_t | adc | ) |

ADC Enable Analog Watchdog for Regular Conversions.

The analog watchdog allows the monitoring of an analog signal between two threshold levels. The thresholds must be preset.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses.

Definition at line 123 of file adc_common_v1.c.

References ADC_CR1, and ADC_CR1_AWDEN.

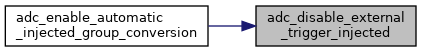

◆ adc_enable_automatic_injected_group_conversion()

| void adc_enable_automatic_injected_group_conversion | ( | uint32_t | adc | ) |

ADC Enable Automatic Injected Conversions.

The ADC converts a defined injected group of channels immediately after the regular channels have been converted. The external trigger on the injected channels is disabled as required.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 239 of file adc_common_v1.c.

References ADC_CR1, ADC_CR1_JAUTO, and adc_disable_external_trigger_injected().

◆ adc_enable_awd_interrupt()

| void adc_enable_awd_interrupt | ( | uint32_t | adc | ) |

ADC Enable Analog Watchdog Interrupt.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 361 of file adc_common_v1.c.

References ADC_CR1, and ADC_CR1_AWDIE.

◆ adc_enable_discontinuous_mode_injected()

| void adc_enable_discontinuous_mode_injected | ( | uint32_t | adc | ) |

ADC Enable Discontinuous Mode for Injected Conversions.

In this mode the ADC converts sequentially one channel of the defined group of injected channels, cycling back to the first channel in the group once the entire group has been converted.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 212 of file adc_common_v1.c.

References ADC_CR1, and ADC_CR1_JDISCEN.

◆ adc_enable_discontinuous_mode_regular()

| void adc_enable_discontinuous_mode_regular | ( | uint32_t | adc, |

| uint8_t | length | ||

| ) |

ADC Enable Discontinuous Mode for Regular Conversions.

In this mode the ADC converts, on each trigger, a subgroup of up to 8 of the defined regular channel group. The subgroup is defined by the number of consecutive channels to be converted. After a subgroup has been converted the next trigger will start conversion of the immediately following subgroup of the same length or until the whole group has all been converted. When the the whole group has been converted, the next trigger will restart conversion of the subgroup at the beginning of the whole group.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses [in] length Unsigned int8. Number of channels in the group ADC Number of channels in discontinuous mode.

Definition at line 182 of file adc_common_v1.c.

References ADC_CR1, ADC_CR1_DISCEN, and ADC_CR1_DISCNUM_SHIFT.

◆ adc_enable_dma()

| void adc_enable_dma | ( | uint32_t | adc | ) |

ADC Enable DMA Transfers.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 735 of file adc_common_v1.c.

References ADC_CR2, and ADC_CR2_DMA.

◆ adc_enable_eoc_interrupt()

| void adc_enable_eoc_interrupt | ( | uint32_t | adc | ) |

ADC Enable Regular End-Of-Conversion Interrupt.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 384 of file adc_common_v1.c.

References ADC_CR1, and ADC_CR1_EOCIE.

◆ adc_enable_eoc_interrupt_injected()

| void adc_enable_eoc_interrupt_injected | ( | uint32_t | adc | ) |

ADC Enable Injected End-Of-Conversion Interrupt.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 339 of file adc_common_v1.c.

References ADC_CR1, and ADC_CR1_JEOCIE.

◆ adc_enable_external_trigger_injected()

| void adc_enable_external_trigger_injected | ( | uint32_t | adc, |

| uint32_t | trigger, | ||

| uint32_t | polarity | ||

| ) |

ADC Enable an External Trigger for Injected Channels.

This enables an external trigger for set of defined injected channels, and sets the polarity of the trigger event: rising or falling edge or both.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses [in] trigger Unsigned int8. Trigger identifier ADC Trigger Identifier for Injected group [in] polarity Unsigned int32. Trigger polarity ADC Injected Trigger Polarity

Definition at line 166 of file adc_common_v1_multi.c.

References ADC_CR2, ADC_CR2_JEXTEN_MASK, and ADC_CR2_JEXTSEL_MASK.

◆ adc_enable_external_trigger_regular()

| void adc_enable_external_trigger_regular | ( | uint32_t | adc, |

| uint32_t | trigger, | ||

| uint32_t | polarity | ||

| ) |

ADC Enable an External Trigger for Regular Channels.

This enables an external trigger for set of defined regular channels, and sets the polarity of the trigger event: rising or falling edge or both. Note that if the trigger polarity is zero, triggering is disabled.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses [in] trigger Unsigned int32. Trigger identifier ADC Trigger Identifier for Regular group [in] polarity Unsigned int32. Trigger polarity ADC Trigger Polarity

Definition at line 133 of file adc_common_v1_multi.c.

References ADC_CR2, ADC_CR2_EXTEN_MASK, and ADC_CR2_EXTSEL_MASK.

◆ adc_enable_overrun_interrupt()

| void adc_enable_overrun_interrupt | ( | uint32_t | adc | ) |

ADC Enable the Overrun Interrupt.

The overrun interrupt is generated when data is not read from a result register before the next conversion is written. If DMA is enabled, all transfers are terminated and any conversion sequence is aborted.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 216 of file adc_common_v1_multi.c.

References ADC_CR1, and ADC_CR1_OVRIE.

◆ adc_enable_scan_mode()

| void adc_enable_scan_mode | ( | uint32_t | adc | ) |

ADC Set Scan Mode.

In this mode a conversion consists of a scan of the predefined set of channels, regular and injected, each channel conversion immediately following the previous one. It can use single, continuous or discontinuous mode.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 317 of file adc_common_v1.c.

References ADC_CR1, and ADC_CR1_SCAN.

◆ adc_enable_temperature_sensor()

| void adc_enable_temperature_sensor | ( | void | ) |

ADC Enable The Temperature Sensor.

This enables both the sensor and the reference voltage measurements on ADC1. On STM32F42x and STM32F43x, the temperature sensor is connected to ADC1 channel 18, the same as VBat. If both are enabled, only the VBat conversion is performed.

Definition at line 343 of file adc_common_v1_multi.c.

References ADC_CCR, and ADC_CCR_TSVREFE.

◆ adc_eoc()

| bool adc_eoc | ( | uint32_t | adc | ) |

ADC Read the End-of-Conversion Flag.

This flag is set after all channels of a regular or injected group have been converted.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

- Returns

- bool. End of conversion flag.

Definition at line 435 of file adc_common_v1.c.

References ADC_SR, and ADC_SR_EOC.

◆ adc_eoc_after_each()

| void adc_eoc_after_each | ( | uint32_t | adc | ) |

ADC Enable an EOC for Each Conversion.

The EOC is set after each conversion in a sequence rather than at the end of the sequence. Overrun detection is enabled only if DMA is enabled.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 274 of file adc_common_v1_multi.c.

References ADC_CR2, and ADC_CR2_EOCS.

◆ adc_eoc_after_group()

| void adc_eoc_after_group | ( | uint32_t | adc | ) |

ADC Disable the EOC for Each Conversion.

The EOC is set at the end of each sequence rather than after each conversion in the sequence. Overrun detection is enabled always.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 288 of file adc_common_v1_multi.c.

References ADC_CR2.

◆ adc_eoc_injected()

| bool adc_eoc_injected | ( | uint32_t | adc | ) |

ADC Read the End-of-Conversion Flag for Injected Conversion.

This flag is set after all channels of an injected group have been converted.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

- Returns

- bool. End of conversion flag.

Definition at line 449 of file adc_common_v1.c.

References ADC_SR, and ADC_SR_JEOC.

◆ adc_get_flag()

| bool adc_get_flag | ( | uint32_t | adc, |

| uint32_t | flag | ||

| ) |

Read a Status Flag.

- Parameters

-

[in] adc Unsigned int32. ADC register address base ADC register base addresses [in] flag Unsigned int32. Status register flag ADC Status Register Flags.

- Returns

- boolean: flag set.

Definition at line 759 of file adc_common_v1.c.

References ADC_SR.

◆ adc_get_overrun_flag()

| bool adc_get_overrun_flag | ( | uint32_t | adc | ) |

ADC Read the Overrun Flag.

The overrun flag is set when data is not read from a result register before the next conversion is written. If DMA is enabled, all transfers are terminated and any conversion sequence is aborted.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

- Returns

- Unsigned int32 conversion result.

Definition at line 243 of file adc_common_v1_multi.c.

References ADC_SR, and ADC_SR_OVR.

◆ adc_power_off()

| void adc_power_off | ( | uint32_t | adc | ) |

ADC Off.

Turn off the ADC to reduce power consumption to a few microamps.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses.

Definition at line 108 of file adc_common_v1.c.

References ADC_CR2.

◆ adc_power_on()

| void adc_power_on | ( | uint32_t | adc | ) |

ADC Power On.

If the ADC is in power-down mode then it is powered up. The application needs to wait a time of about 3 microseconds for stabilization before using the ADC. If the ADC is already on this function call will have no effect. NOTE Common with L1 and F2

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 102 of file adc_common_v1_multi.c.

References ADC_CR2, and ADC_CR2_ADON.

◆ adc_read_injected()

| uint32_t adc_read_injected | ( | uint32_t | adc, |

| uint8_t | reg | ||

| ) |

ADC Read from an Injected Conversion Result Register.

The result read back from the selected injected result register (one of four) is 12 bits, right or left aligned within the first 16 bits. The result can have a negative value if the injected channel offset has been set

- See also

- adc_set_injected_offset.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses [in] reg Unsigned int8. Register number (1 ... 4).

- Returns

- Unsigned int32 conversion result.

Definition at line 483 of file adc_common_v1.c.

◆ adc_read_regular()

| uint32_t adc_read_regular | ( | uint32_t | adc | ) |

ADC Read from the Regular Conversion Result Register.

The result read back is 12 bits, right or left aligned within the first 16 bits. For ADC1 only, the higher 16 bits will hold the result from ADC2 if an appropriate dual mode has been set

- See also

- adc_set_dual_mode.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

- Returns

- Unsigned int32 conversion result.

Definition at line 465 of file adc_common_v1.c.

References ADC_DR.

◆ adc_set_clk_prescale()

| void adc_set_clk_prescale | ( | uint32_t | prescale | ) |

ADC Set Clock Prescale The ADC clock can be prescaled.

The Clock sources and scaler values are part specific.

- Parameters

-

[in] prescale Prescale value for ADC Clock ADC Prescale

Definition at line 114 of file adc_common_v1_multi.c.

References ADC_CCR.

◆ adc_set_continuous_conversion_mode()

| void adc_set_continuous_conversion_mode | ( | uint32_t | adc | ) |

ADC Enable Continuous Conversion Mode.

In this mode the ADC starts a new conversion of a single channel or a channel group immediately following completion of the previous channel group conversion.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 507 of file adc_common_v1.c.

References ADC_CR2, and ADC_CR2_CONT.

◆ adc_set_dma_continue()

| void adc_set_dma_continue | ( | uint32_t | adc | ) |

ADC Set DMA to Continue.

This must be set to allow DMA to continue to operate after the last conversion in the DMA sequence. This allows DMA to be used in continuous circular mode.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 302 of file adc_common_v1_multi.c.

References ADC_CR2, and ADC_CR2_DDS.

◆ adc_set_dma_terminate()

| void adc_set_dma_terminate | ( | uint32_t | adc | ) |

ADC Set DMA to Terminate.

This must be set to allow DMA to terminate after the last conversion in the DMA sequence. This can avoid overrun errors.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses

Definition at line 316 of file adc_common_v1_multi.c.

References ADC_CR2.

◆ adc_set_injected_offset()

| void adc_set_injected_offset | ( | uint32_t | adc, |

| uint8_t | reg, | ||

| uint32_t | offset | ||

| ) |

ADC Set the Injected Channel Data Offset.

This value is subtracted from the injected channel results after conversion is complete, and can result in negative results. A separate value can be specified for each injected data register.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses [in] reg Unsigned int8. Register number (1 ... 4). [in] offset Unsigned int32.

Definition at line 662 of file adc_common_v1.c.

◆ adc_set_injected_sequence()

| void adc_set_injected_sequence | ( | uint32_t | adc, |

| uint8_t | length, | ||

| uint8_t | channel[] | ||

| ) |

ADC Set an Injected Channel Conversion Sequence.

Defines a sequence of channels to be converted as an injected group with a length from 1 to 4 channels. If this is called during conversion, the current conversion is reset and conversion begins again with the newly defined group.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses [in] length Unsigned int8. Number of channels in the group. [in] channel Unsigned int8[]. Set of channels in sequence, integers 0..18

Definition at line 630 of file adc_common_v1.c.

References ADC_JSQR, ADC_JSQR_JL_VAL, and ADC_JSQR_JSQ_VAL.

◆ adc_set_left_aligned()

| void adc_set_left_aligned | ( | uint32_t | adc | ) |

ADC Set the Data as Left Aligned.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses.

Definition at line 408 of file adc_common_v1.c.

References ADC_CR2, and ADC_CR2_ALIGN.

◆ adc_set_regular_sequence()

| void adc_set_regular_sequence | ( | uint32_t | adc, |

| uint8_t | length, | ||

| uint8_t | channel[] | ||

| ) |

ADC Set a Regular Channel Conversion Sequence.

Define a sequence of channels to be converted as a regular group with a length from 1 to ADC_REGULAR_SEQUENCE_MAX channels. If this is called during conversion, the current conversion is reset and conversion begins again with the newly defined group.

- Parameters

-

[in] adc Unsigned int32. ADC block base address ADC register base addresses. [in] length Unsigned int8. Number of channels in the group. [in] channel Unsigned int8[]. Set of channels in sequence, integers 0..31.

Definition at line 574 of file adc_common_v1.c.

References ADC_SQR1, ADC_SQR1_L_LSB, ADC_SQR2, ADC_SQR3, and ADC_SQR_MAX_CHANNELS_REGULAR.

◆ adc_set_resolution()

| void adc_set_resolution | ( | uint32_t | adc, |

| uint32_t | resolution | ||

| ) |

ADC Set Resolution.

ADC Resolution can be reduced from 12 bits to 10, 8 or 6 bits for a corresponding reduction in conversion time (resolution + 3 ADC clock cycles).

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses [in] resolution Unsigned int32. Resolution value ADC Resolution.

Definition at line 197 of file adc_common_v1_multi.c.

References ADC_CR1.

◆ adc_set_right_aligned()

| void adc_set_right_aligned | ( | uint32_t | adc | ) |

ADC Set the Data as Right Aligned.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses.

Definition at line 420 of file adc_common_v1.c.

References ADC_CR2.

◆ adc_set_sample_time()

| void adc_set_sample_time | ( | uint32_t | adc, |

| uint8_t | channel, | ||

| uint8_t | time | ||

| ) |

ADC Set the Sample Time for a Single Channel.

The sampling time can be selected in ADC clock cycles from 1.5 to 239.5.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses [in] channel Unsigned int8. ADC Channel integer 0..18 or from ADC Channel Numbers [in] time Unsigned int8. Sampling time selection from ADC Sample Time Selection for All Channels NOTE Common with f1, f2 and f37x

Definition at line 45 of file adc_common_f47.c.

◆ adc_set_sample_time_on_all_channels()

| void adc_set_sample_time_on_all_channels | ( | uint32_t | adc, |

| uint8_t | time | ||

| ) |

ADC Set the Sample Time for All Channels.

The sampling time can be selected in ADC clock cycles from 1.5 to 239.5, same for all channels.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses [in] time Unsigned int8. Sampling time selection from ADC Sample Time Selection for All Channels NOTE Common with f1, f2 and f37x

Definition at line 72 of file adc_common_f47.c.

◆ adc_set_single_conversion_mode()

| void adc_set_single_conversion_mode | ( | uint32_t | adc | ) |

ADC Enable Single Conversion Mode.

In this mode the ADC performs a conversion of one channel or a channel group and stops.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses.

Definition at line 523 of file adc_common_v1.c.

References ADC_CR2.

◆ adc_set_watchdog_high_threshold()

| void adc_set_watchdog_high_threshold | ( | uint32_t | adc, |

| uint16_t | threshold | ||

| ) |

ADC Set Analog Watchdog Upper Threshold.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses [in] threshold Upper threshold value, 12bit right aligned.

Definition at line 535 of file adc_common_v1.c.

References ADC_HT_MSK, and ADC_HTR.

◆ adc_set_watchdog_low_threshold()

| void adc_set_watchdog_low_threshold | ( | uint32_t | adc, |

| uint16_t | threshold | ||

| ) |

ADC Set Analog Watchdog Lower Threshold.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses [in] threshold Lower threshold value, 12bit right aligned.

Definition at line 551 of file adc_common_v1.c.

References ADC_LT_MSK, and ADC_LTR.

◆ adc_start_conversion_injected()

| void adc_start_conversion_injected | ( | uint32_t | adc | ) |

ADC Software Triggered Conversion on Injected Channels.

This starts conversion on a set of defined injected channels if the ADC trigger is set to be a software trigger. It is cleared by hardware once conversion starts.

Special F1 Note this is a software trigger and requires triggering to be enabled and the trigger source to be set appropriately otherwise conversion will not start. This is not the same as the ADC start conversion operation.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses.

Definition at line 719 of file adc_common_v1.c.

References ADC_CR2, and ADC_CR2_JSWSTART.

◆ adc_start_conversion_regular()

| void adc_start_conversion_regular | ( | uint32_t | adc | ) |

ADC Software Triggered Conversion on Regular Channels.

This starts conversion on a set of defined regular channels if the ADC trigger is set to be a software trigger. It is cleared by hardware once conversion starts.

Special F1 Note this is a software trigger and requires triggering to be enabled and the trigger source to be set appropriately otherwise conversion will not start. This is not the same as the ADC start conversion operation.

- Parameters

-

[in] adc Unsigned int32. ADC block register address base ADC register base addresses.

Definition at line 695 of file adc_common_v1.c.

References ADC_CR2, and ADC_CR2_SWSTART.