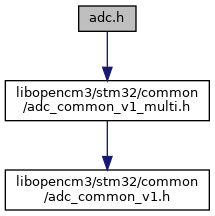

Include dependency graph for f7/adc.h:

Go to the source code of this file.

Macros | |

| #define | ADC_JOFR1(block) MMIO32((block) + 0x14) |

| #define | ADC_JOFR2(block) MMIO32((block) + 0x18) |

| #define | ADC_JOFR3(block) MMIO32((block) + 0x1c) |

| #define | ADC_JOFR4(block) MMIO32((block) + 0x20) |

| #define | ADC_HTR(block) MMIO32((block) + 0x24) |

| #define | ADC_LTR(block) MMIO32((block) + 0x28) |

| #define | ADC_SQR1(block) MMIO32((block) + 0x2c) |

| #define | ADC_SQR2(block) MMIO32((block) + 0x30) |

| #define | ADC_SQR3(block) MMIO32((block) + 0x34) |

| #define | ADC_JSQR(block) MMIO32((block) + 0x38) |

| #define | ADC_JDR1(block) MMIO32((block) + 0x3c) |

| #define | ADC_JDR2(block) MMIO32((block) + 0x40) |

| #define | ADC_JDR3(block) MMIO32((block) + 0x44) |

| #define | ADC_JDR4(block) MMIO32((block) + 0x48) |

| #define | ADC_DR(block) MMIO32((block) + 0x4c) |

| #define | ADC_CHANNEL_TEMP 18 |

| #define | ADC_CHANNEL_VREF 17 |

| #define | ADC_CHANNEL_VBAT 18 |

| #define | ADC_CR1_AWDCH_MAX 18 |

| #define | ADC_CR2_EXTSEL_TIM1_CC1 (0x0 << 24) |

| Timer 1 Compare Output 1. More... | |

| #define | ADC_CR2_EXTSEL_TIM1_CC2 (0x1 << 24) |

| Timer 1 Compare Output 2. More... | |

| #define | ADC_CR2_EXTSEL_TIM1_CC3 (0x2 << 24) |

| Timer 1 Compare Output 3. More... | |

| #define | ADC_CR2_EXTSEL_TIM2_CC2 (0x3 << 24) |

| Timer 2 Compare Output 2. More... | |

| #define | ADC_CR2_EXTSEL_TIM5_TRGO (0x4 << 24) |

| Timer 5 TRGO Event. More... | |

| #define | ADC_CR2_EXTSEL_TIM4_CC4 (0x5 << 24) |

| Timer 4 Compare Output 4. More... | |

| #define | ADC_CR2_EXTSEL_TIM3_CC4 (0x6 << 24) |

| Timer 3 Compare Output 4. More... | |

| #define | ADC_CR2_EXTSEL_TIM8_TRGO (0x7 << 24) |

| Timer 8 TRGO Event. More... | |

| #define | ADC_CR2_EXTSEL_TIM8_TRGO2 (0x8 << 24) |

| Timer 8 TRGO2 Event. More... | |

| #define | ADC_CR2_EXTSEL_TIM1_TRGO (0x9 << 24) |

| Timer 1 TRGO Event. More... | |

| #define | ADC_CR2_EXTSEL_TIM1_TRGO2 (0xA << 24) |

| Timer 1 TRGO2 Event. More... | |

| #define | ADC_CR2_EXTSEL_TIM2_TRGO (0xB << 24) |

| Timer 2 TRGO Event. More... | |

| #define | ADC_CR2_EXTSEL_TIM4_TRGO (0xC << 24) |

| Timer 4 TRGO Event. More... | |

| #define | ADC_CR2_EXTSEL_TIM6_TRGO (0xD << 24) |

| Timer 6 TRGO Event. More... | |

| #define | ADC_CR2_EXTSEL_EXTI_LINE_11 (0xF << 24) |

| EXTI Line 11 Event. More... | |

| #define | ADC_CR2_JEXTSEL_TIM1_TRGO (0x0 << 16) |

| #define | ADC_CR2_JEXTSEL_TIM1_CC4 (0x1 << 16) |

| #define | ADC_CR2_JEXTSEL_TIM2_TRGO (0x2 << 16) |

| #define | ADC_CR2_JEXTSEL_TIM2_CC1 (0x3 << 16) |

| #define | ADC_CR2_JEXTSEL_TIM3_CC4 (0x4 << 16) |

| #define | ADC_CR2_JEXTSEL_TIM4_TRGO (0x5 << 16) |

| #define | ADC_CR2_JEXTSEL_TIM8_CC4 (0x7 << 16) |

| #define | ADC_CR2_JEXTSEL_TIM1_TRGO2 (0x8 << 16) |

| #define | ADC_CR2_JEXTSEL_TIM8_TRGO (0x9 << 16) |

| #define | ADC_CR2_JEXTSEL_TIM8_TRGO2 (0xA << 16) |

| #define | ADC_CR2_JEXTSEL_TIM3_cc3 (0xB << 16) |

| #define | ADC_CR2_JEXTSEL_TIM5_TRGO (0xC << 16) |

| #define | ADC_CR2_JEXTSEL_TIM3_CC1 (0xD << 16) |

| #define | ADC_CR2_JEXTSEL_TIM6_TRGO (0xE << 16) |

| #define | ADC_SMPR_SMP_3CYC 0x0 |

| #define | ADC_SMPR_SMP_15CYC 0x1 |

| #define | ADC_SMPR_SMP_28CYC 0x2 |

| #define | ADC_SMPR_SMP_56CYC 0x3 |

| #define | ADC_SMPR_SMP_84CYC 0x4 |

| #define | ADC_SMPR_SMP_112CYC 0x5 |

| #define | ADC_SMPR_SMP_144CYC 0x6 |

| #define | ADC_SMPR_SMP_480CYC 0x7 |

| #define | ADC_SQR1_L_MSK (0xf << ADC_SQR1_L_LSB) |

| #define | ADC_SQR_MAX_CHANNELS_REGULAR 16 |

| #define | ADC_CCR_ADCPRE_BY2 (0x0 << 16) |

| #define | ADC_CCR_ADCPRE_BY4 (0x1 << 16) |

| #define | ADC_CCR_ADCPRE_BY6 (0x2 << 16) |

| #define | ADC_CCR_ADCPRE_BY8 (0x3 << 16) |

| #define | ADC_CCR_ADCPRE_MASK (0x3 << 16) |

| #define | ADC_CCR_ADCPRE_SHIFT 16 |

Functions | |

| void | adc_set_multi_mode (uint32_t mode) |

| ADC Set Dual/Triple Mode. More... | |

| void | adc_enable_vbat_sensor (void) |

| Enable The VBat Sensor. More... | |

| void | adc_disable_vbat_sensor (void) |

| Disable The VBat Sensor. More... | |

Macro Definition Documentation

◆ ADC_CCR_ADCPRE_MASK

◆ ADC_CCR_ADCPRE_SHIFT

◆ ADC_CR1_AWDCH_MAX

◆ ADC_DR

◆ ADC_HTR

◆ ADC_JDR1

◆ ADC_JDR2

◆ ADC_JDR3

◆ ADC_JDR4

◆ ADC_JOFR1

◆ ADC_JOFR2

◆ ADC_JOFR3

◆ ADC_JOFR4

◆ ADC_JSQR

◆ ADC_LTR

◆ ADC_SQR1

◆ ADC_SQR1_L_MSK

| #define ADC_SQR1_L_MSK (0xf << ADC_SQR1_L_LSB) |