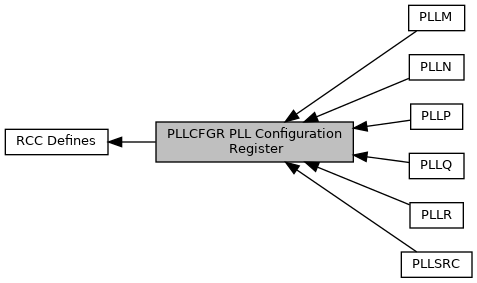

PLLCFGR PLL Configuration Register

Collaboration diagram for PLLCFGR PLL Configuration Register:

Modules | |

| PLLR | |

| VCO Division factor R for PLLRCLK clock output [2..8]. | |

| PLLQ | |

| VCO Division factor Q for PLLQCLK clock output [2..8]. | |

| PLLP | |

| VCO Division factor P for PLLPCLK clock output [2..32]. | |

| PLLN | |

| Multiplication factor N [8..86] for PLL VCO output frequency. | |

| PLLM | |

| Division factor M [1..8] for PLL input clock. | |

| PLLSRC | |

| PLL input clock source. | |

Macros | |

| #define | RCC_PLLCFGR_PLLR_SHIFT 29 |

| #define | RCC_PLLCFGR_PLLR_MASK 0x7 |

| #define | RCC_PLLCFGR_PLLREN (1<<28) |

| #define | RCC_PLLCFGR_PLLQ_SHIFT 25 |

| #define | RCC_PLLCFGR_PLLQ_MASK 0x7 |

| #define | RCC_PLLCFGR_PLLQEN (1 << 24) |

| #define | RCC_PLLCFGR_PLLP_SHIFT 17 |

| #define | RCC_PLLCFGR_PLLP_MASK 0x1f |

| #define | RCC_PLLCFGR_PLLPEN (1 << 16) |

| #define | RCC_PLLCFGR_PLLN_SHIFT 0x8 |

| #define | RCC_PLLCFGR_PLLN_MASK 0x7f |

| #define | RCC_PLLCFGR_PLLM_SHIFT 0x4 |

| #define | RCC_PLLCFGR_PLLM_MASK 0x7 |

| #define | RCC_PLLCFGR_PLLSRC_SHIFT 0 |

| #define | RCC_PLLCFGR_PLLSRC_MASK 0x3 |