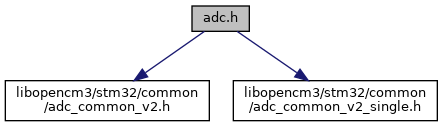

#include <libopencm3/stm32/common/adc_common_v2.h>#include <libopencm3/stm32/common/adc_common_v2_single.h>

Include dependency graph for g0/adc.h:

Go to the source code of this file.

Macros | |

| #define | ADC1 ADC1_BASE |

| #define | ADC_CHANNEL_TEMP 12 |

| #define | ADC_CHANNEL_VREF 13 |

| #define | ADC_CHANNEL_VBAT 14 |

| #define | ADC_AWD1TR(adc) MMIO32((adc) + 0x20) |

| ADC_AWD1TR Watchdog 1 Threshold register. More... | |

| #define | ADC_AWD2TR(adc) MMIO32((adc) + 0x22) |

| ADC_AWD2TR Watchdog 2 Threshold register. More... | |

| #define | ADC_AWD3TR(adc) MMIO32((adc) + 0x2c) |

| ADC_AWD3TR Watchdog 3 Threshold register. More... | |

| #define | ADC_AWD2CR(adc) MMIO32((adc) + 0xA0) |

| ADC_AWD2CR Watchdog 2 Configuration register. More... | |

| #define | ADC_AWD3CR(adc) MMIO32((adc) + 0xA4) |

| ADC_AWD3CR Watchdog 3 Configuration register. More... | |

| #define | ADC_CALFACT(adc) MMIO32((adc) + 0xB4) |

| ADC_CALFACT Calibration factor register. More... | |

| #define | ADC_ISR_CCRDY (1 << 13) |

| CCRDY: Channel Configuration Ready flag. More... | |

| #define | ADC_IER_CCRDYIE (1 << 13) |

| CCRDYIE: Channel Configuration Ready Interrupt enable bit. More... | |

| #define | ADC_CCR_PRESC_MASK (0xf) |

| #define | ADC_CCR_PRESC_SHIFT (18) |

| #define | ADC_CCR_PRESC_NODIV (0x0) |

| #define | ADC_CCR_PRESC_DIV2 (0x1) |

| #define | ADC_CCR_PRESC_DIV4 (0x2) |

| #define | ADC_CCR_PRESC_DIV6 (0x3) |

| #define | ADC_CCR_PRESC_DIV8 (0x4) |

| #define | ADC_CCR_PRESC_DIV10 (0x5) |

| #define | ADC_CCR_PRESC_DIV12 (0x6) |

| #define | ADC_CCR_PRESC_DIV16 (0x7) |

| #define | ADC_CCR_PRESC_DIV32 (0x8) |

| #define | ADC_CCR_PRESC_DIV64 (0x9) |

| #define | ADC_CCR_PRESC_DIV128 (0xa) |

| #define | ADC_CCR_PRESC_DIV256 (0xb) |

| #define | ADC_CR_ADVREGEN (1 << 28) |

| ADVREGEN: Voltage regulator enable bit. More... | |

| #define | ADC_CFGR1_ALIGN (1 << 5) |

| ALIGN: Data alignment. More... | |

| #define | ADC_CFGR1_EXTSEL_SHIFT 6 |

| #define | ADC_CFGR1_EXTSEL (0x7 << ADC_CFGR1_EXTSEL_SHIFT) |

| #define | ADC_CFGR1_EXTSEL_VAL(x) ((x) << ADC_CFGR1_EXTSEL_SHIFT) |

| #define | ADC_CFGR1_EXTSEL_TIM1_TRGO2 0x0 |

| #define | ADC_CFGR1_EXTSEL_TIM1_CC4 0x1 |

| #define | ADC_CFGR1_EXTSEL_TIM2_TRGO 0x2 |

| #define | ADC_CFGR1_EXTSEL_TIM3_TRGO 0x3 |

| #define | ADC_CFGR1_EXTSEL_TIM15_TRGO 0x4 |

| #define | ADC_CFGR1_EXTSEL_TIM6_TRGO 0x5 |

| #define | ADC_CFGR1_EXTSEL_TIM4_TRGO 0x6 |

| #define | ADC_CFGR1_EXTSEL_EXTI11 0x7 |

| #define | ADC_CFGR1_CHSELRMOD (1 << 21) |

| CHSELRMOD: Mode Selection of the ADC_CHSELR register. More... | |

| #define | ADC_CFGR2_CKMODE_SHIFT (30) |

| #define | ADC_CFGR2_CKMODE_MASK (0x3) |

| #define | ADC_CFGR2_CKMODE_ADCCLK (0x0) |

| #define | ADC_CFGR2_CKMODE_PCLK_DIV2 (0x1) |

| #define | ADC_CFGR2_CKMODE_PCLK_DIV4 (0x2) |

| #define | ADC_CFGR2_CKMODE_PCLK (0x3) |

| #define | ADC_CFGR2_LFTRIG (1 << 29) |

| LFTRIG: Low Frequency Trigger Mode enable bit. More... | |

| #define | ADC_CFGR2_TOVS (1 << 9) |

| TOVS: Triggered Oversampling. More... | |

| #define | ADC_CFGR2_OVSS_SHIFT (5) |

| #define | ADC_CFGR2_OVSS_MASK (0xf) |

| #define | ADC_CFGR2_OVSS_BITS(bits) (bits) |

| #define | ADC_CFGR2_OVSR_SHIFT (2) |

| #define | ADC_CFGR2_OVSR_MASK (0x7) |

| #define | ADC_CFGR2_OVSR_2x (0x0) |

| #define | ADC_CFGR2_OVSR_4x (0x1) |

| #define | ADC_CFGR2_OVSR_8x (0x2) |

| #define | ADC_CFGR2_OVSR_16x (0x3) |

| #define | ADC_CFGR2_OVSR_32x (0x4) |

| #define | ADC_CFGR2_OVSR_64x (0x5) |

| #define | ADC_CFGR2_OVSR_128x (0x6) |

| #define | ADC_CFGR2_OVSR_256x (0x7) |

| #define | ADC_CFGR2_OVSE (1 << 0) |

| OVSE: Oversampler mode enable bit. More... | |

| #define | ADC_SMPR_SMPSEL_SHIFT 0x8 |

| #define | ADC_SMPR_SMPSEL_MASK 0x7ffff |

| #define | ADC_SMPR_SMPSEL_CHANNEL_SHIFT(channel) ((channel) + ADC_SMPR_SMPSEL_SHIFT) |

| #define | ADC_SMPR_SMPSEL_CHANNEL_MASK (1) |

| #define | ADC_SMPR_SMPSEL_SMP1 0x0 |

| #define | ADC_SMPR_SMPSEL_SMP2 0x1 |

| #define | ADC_SMPR_SMP1_SHIFT 0x0 |

| SMP1 ADC Sample Time #1 selection. More... | |

| #define | ADC_SMPR_SMP1_MASK 0x7 |

| #define | ADC_SMPR_SMP2_SHIFT 0x4 |

| SMP1 ADC Sample Time #2 selection. More... | |

| #define | ADC_SMPR_SMP2_MASK 0x7 |

| #define | ADC_SMPR_SMPx_001DOT5CYC 0x0 |

| #define | ADC_SMPR_SMPx_003DOT5CYC 0x1 |

| #define | ADC_SMPR_SMPx_007DOT5CYC 0x2 |

| #define | ADC_SMPR_SMPx_012DOT5CYC 0x3 |

| #define | ADC_SMPR_SMPx_019DOT5CYC 0x4 |

| #define | ADC_SMPR_SMPx_039DOT5CYC 0x5 |

| #define | ADC_SMPR_SMPx_079DOT5CYC 0x6 |

| #define | ADC_SMPR_SMPx_160DOT5CYC 0x7 |

| #define | ADC_AWDTR1_LT_SHIFT 0 |

| #define | ADC_AWDTR1_LT (0xFFF << ADC_TR1_LT_SHIFT) |

| #define | ADC_AWDTR1_LT_VAL(x) ((x) << ADC_TR1_LT_SHIFT) |

| #define | ADC_AWDTR1_HT_SHIFT 16 |

| #define | ADC_AWDTR1_HT (0xFFF << ADC_TR1_HT_SHIFT) |

| #define | ADC_AWDTR1_HT_VAL(x) ((x) << ADC_TR1_HT_SHIFT) |

| #define | ADC_AWDTR2_LT_SHIFT 0 |

| #define | ADC_AWDTR2_LT (0xFFF << ADC_TR2_LT_SHIFT) |

| #define | ADC_AWDTR2_LT_VAL(x) ((x) << ADC_TR2_LT_SHIFT) |

| #define | ADC_AWDTR2_HT_SHIFT 16 |

| #define | ADC_AWDTR2_HT (0xFFF << ADC_TR2_HT_SHIFT) |

| #define | ADC_AWDTR2_HT_VAL(x) ((x) << ADC_TR2_HT_SHIFT) |

| #define | ADC_CHSELR_MAX_CHANNELS 18 |

| ADC_CHSELR_MAX_CHANNELS Maximum number of channel in regular sequence. More... | |

| #define | ADC_CHSELR_MAX_SQS 8 |

| ADC_CHSELR_MAX_SQ_CHANNELS Maximum number of sequences in fully configurable mode. More... | |

| #define | ADC_CHSELR_SQS_MAX_CHANNEL 14 |

| ADC_CHSELR_SQS_MAX_CHANNEL Maximum channel number in a fully configuralbe sequence. More... | |

| #define | ADC_CHSELR_SQx_MASK 0xf |

| #define | ADC_CHSELR_SQx_SHIFT(seqnum) (4 * ((seqnum)-1)) |

| #define | ADC_CHSELR_SQx(seqnum, value) ((value) << ADC_CHSELR_SQx_SHIFT(seqnum)) |

| ADC_CHSELR_SQx Xth conversion of ADC sequence channel number value. More... | |

| #define | ADC_CHSELR_SQx_EOS 0xf |

| ADC_CHSELR_SQx_EOS End of Sequence. More... | |

| #define | ADC_AWDTR3_LT_SHIFT 0 |

| #define | ADC_AWDTR3_LT (0xFFF << ADC_TR3_LT_SHIFT) |

| #define | ADC_AWDTR3_LT_VAL(x) ((x) << ADC_TR3_LT_SHIFT) |

| #define | ADC_AWDTR3_HT_SHIFT 16 |

| #define | ADC_AWDTR3_HT (0xFFF << ADC_TR3_HT_SHIFT) |

| #define | ADC_AWDTR3_HT_VAL(x) ((x) << ADC_TR3_HT_SHIFT) |

| #define | ADC_AW2CR_AWD2CHx_EN(x) (1 << x) |

| AWD2CR Analog watchdog channel selection. More... | |

| #define | ADC_AW3CR_AWD3CHx_EN(x) (1 << x) |

| AWD3CR Analog watchdog channel selection. More... | |

| #define | ADC_CLKSOURCE_ADC ADC_CFGR2_CKMODE_ADCCLK |

| #define | ADC_CLKSOURCE_PCLK ADC_CFGR2_CKMODE_PCLK |

| #define | ADC_CLKSOURCE_PCLK_DIV2 ADC_CFGR2_CKMODE_PCLK_DIV2 |

| #define | ADC_CLKSOURCE_PCLK_DIV4 ADC_CFGR2_CKMODE_PCLK_DIV4 |

| #define | ADC_SMPTIME_001DOT5 ADC_SMPR_SMPx_001DOT5CYC |

| #define | ADC_SMPTIME_003DOT5 ADC_SMPR_SMPx_003DOT5CYC |

| #define | ADC_SMPTIME_007DOT5 ADC_SMPR_SMPx_007DOT5CYC |

| #define | ADC_SMPTIME_012DOT5 ADC_SMPR_SMPx_012DOT5CYC |

| #define | ADC_SMPTIME_019DOT5 ADC_SMPR_SMPx_019DOT5CYC |

| #define | ADC_SMPTIME_039DOT5 ADC_SMPR_SMPx_039DOT5CYC |

| #define | ADC_SMPTIME_079DOT5 ADC_SMPR_SMPx_079DOT5CYC |

| #define | ADC_SMPTIME_160DOT5 ADC_SMPR_SMPx_160DOT5CYC |

Functions | |

| void | adc_set_clk_source (uint32_t adc, uint32_t source) |

| ADC Set Clock Source. More... | |

| void | adc_set_clk_prescale (uint32_t adc, uint32_t prescale) |

| ADC Set Clock Prescale. More... | |

| void | adc_set_channel_sample_time_selection (uint32_t adc, uint8_t channel, uint8_t selection) |

| ADC Set the Sample Time Selection for a Single Channel. More... | |

| void | adc_set_selection_sample_time (uint32_t adc, uint8_t selection, uint8_t time) |

| ADC Set the Sample Time for Given Selection. More... | |

| void | adc_enable_regulator (uint32_t adc) |

| Enable the ADC Voltage regulator. More... | |

| void | adc_disable_regulator (uint32_t adc) |

| Disable the ADC Voltage regulator. More... | |