CAN definitions for the Qorvo PAC55xx series of microcontrollers. More...

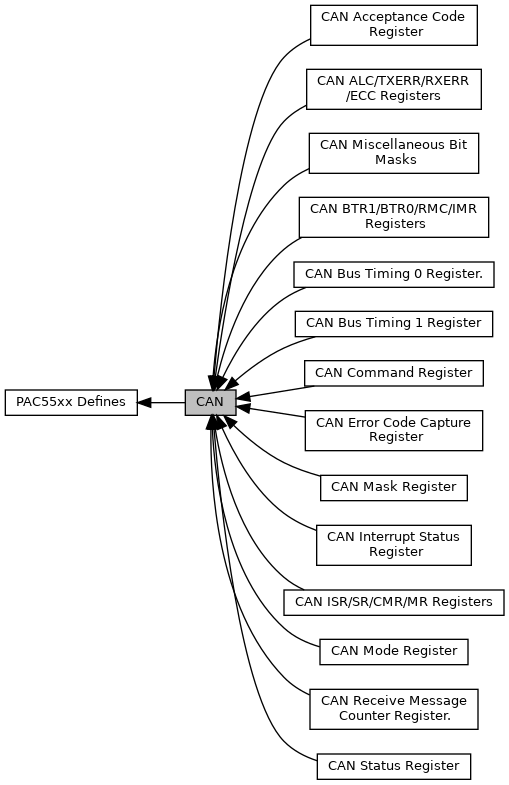

Collaboration diagram for CAN:

Modules | |

| CAN ISR/SR/CMR/MR Registers | |

| CAN BTR1/BTR0/RMC/IMR Registers | |

| CAN ALC/TXERR/RXERR/ECC Registers | |

| CAN Mode Register | |

| CAN Mode Register bit definitions. | |

| CAN Command Register | |

| CAN Command Register. | |

| CAN Status Register | |

| CAN Status Register. | |

| CAN Interrupt Status Register | |

| CAN Interrupt Status Register bit definitions. | |

| CAN Mask Register | |

| CAN Interrupt Mask Register bit definitions. | |

| CAN Receive Message Counter Register. | |

| CAN Receive Message Counter Register bit definitions. | |

| CAN Bus Timing 0 Register. | |

| CAN Bus Timing 0 Register bit definitions. | |

| CAN Bus Timing 1 Register | |

| CAN Bus Timing 1 Register bit definitions. | |

| CAN Error Code Capture Register | |

| CAN Error Code Capture Register bit definitions. | |

| CAN Acceptance Code Register | |

| CAN Acceptance Code/Mask Register. | |

| CAN Miscellaneous Bit Masks | |

Macros | |

| #define | CAN_TXBUF(can_base) MMIO32((can_base) + 0x0008) |

| CAN Transmit Buffer Register RW, default 00000000h. More... | |

| #define | CAN_RXBUF(can_base) MMIO32((can_base) + 0x000C) |

| CAN Receive Buffer Register RO, default 00000000h. More... | |

| #define | CAN_ACR(can_base) MMIO32((can_base) + 0x0010) |

| CAN Acceptance Code Register RW, default 00000000h. More... | |

| #define | CAN_AMR(can_base) MMIO32((can_base) + 0x0014) |

| CAN Acceptance Mask Register RW, default 00000000h. More... | |

Detailed Description

CAN definitions for the Qorvo PAC55xx series of microcontrollers.

- Date

- February 13, 2020

Definitions in this file come from the PAC55XX Family User Guide Rev 1.23 by Active-Semi dated November 19, 2019.

Note: all memory-mapped writes must be performed using 32-bit registers. Any 8-bit memory-mapped registers below may only be used to read.

Macro Definition Documentation

◆ CAN_ACR

| #define CAN_ACR | ( | can_base | ) | MMIO32((can_base) + 0x0010) |

◆ CAN_AMR

| #define CAN_AMR | ( | can_base | ) | MMIO32((can_base) + 0x0014) |

◆ CAN_RXBUF

| #define CAN_RXBUF | ( | can_base | ) | MMIO32((can_base) + 0x000C) |