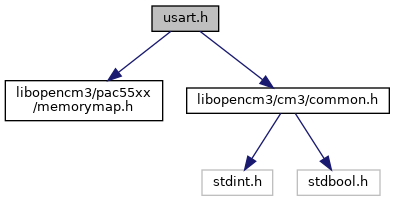

Include dependency graph for usart.h:

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Macros | |

| #define | USART_RBR(usart_base) MMIO32((usart_base) + 0x0000) |

| Receive Buffer Register RO, only bits 7:0 used. More... | |

| #define | USART_THR(usart_base) MMIO32((usart_base) + 0x0004) |

| Transmit Holding Register WO, only bits 7:0 used. More... | |

| #define | USART_DLR(usart_base) MMIO32((usart_base) + 0x0008) |

| Divisor Latch Register RW, default 0000 0001h, only bits 15:0 used. More... | |

| #define | USART_IER(usart_base) MMIO32((usart_base) + 0x000C) |

| Interrupt Enable Register RW, default 0000 0000h. More... | |

| #define | USART_IIR(usart_base) MMIO32((usart_base) + 0x0010) |

| Interrupt Identification Register RO, default 0000 0001h. More... | |

| #define | USART_FCR(usart_base) MMIO32((usart_base) + 0x0014) |

| FIFO Control Register RW, default 0000 0000h. More... | |

| #define | USART_LCR(usart_base) MMIO32((usart_base) + 0x0018) |

| Line control Register RW, default 0000 0000h. More... | |

| #define | USART_LSR(usart_base) MMIO32((usart_base) + 0x0020) |

| Line Status Register RO, default 0000 0060h. More... | |

| #define | USART_SCR(usart_base) MMIO32((usart_base) + 0x0028) |

| Scratch Pad Register RW, only bits 7:0 used. More... | |

| #define | USART_EFR(usart_base) MMIO32((usart_base) + 0x002C) |

| Enhanced Mode Register RW, default 0000 000h. More... | |

| #define | USART_IER_RLSIE BIT2 |

| Enable RX line status interrupt. More... | |

| #define | USART_IER_THRIE BIT1 |

| Enable the TX Holding Empty interrupt. More... | |

| #define | USART_IER_RBRIE BIT0 |

| Enable the RX Buffer Register Interrupt. More... | |

| #define | USART_IIR_INTSTATUS BIT0 |

| This bit is active low to indicate an interrupt is pending. More... | |

| #define | USART_IIR_TXEMPTY (0x02) |

| TX Holding Register Empty. More... | |

| #define | USART_IIR_RXAVAIL (0x04) |

| Receive Data Available. More... | |

| #define | USART_IIR_RXLINESTAT (0x06) |

| Receive Line Status. More... | |

| #define | USART_IIR_RXTIMEOUT (0x0C) |

| Receive FIFO Character Time-out. More... | |

| #define | USART_FCR_FIFOEN BIT0 |

| Enable both UART RX and TX FIFOs, must be set before writing rest of FCR. More... | |

| #define | USART_FCR_RXFIFORST BIT1 |

| RX FIFO Reset. More... | |

| #define | USART_FCR_TXFIFORST BIT2 |

| TX FIFO Reset. More... | |

| #define | USART_FCR_TXTL_MASK (3) |

| #define | USART_FCR_TXTL_SHIFT 4 |

| #define | USART_FCR_TXTL(txtl) (((txtl) & USART_FCR_TXTL_MASK) << USART_FCR_TXTL_SHIFT) |

| TX Trigger Level. More... | |

| #define | USART_FCR_RXTL_MASK (3) |

| #define | USART_FCR_RXTL_SHIFT 6 |

| #define | USART_FCR_RXTL(rxtl) (((rxtl) & USART_FCR_RXTL_MASK) << USART_FCR_RXTL_SHIFT) |

| RX Trigger Level. More... | |

| #define | USART_FIFO_TRIG_1CHAR (0) |

| #define | USART_FIFO_TRIG_4CHAR (1) |

| #define | USART_FIFO_TRIG_8CHAR (2) |

| #define | USART_FIFO_TRIG_14CHAR (3) |

| #define | USART_DATABITS_5 (0) |

| LCR:WLS 5-bit character length. More... | |

| #define | USART_DATABITS_6 (0x01) |

| LCR:WLS 6-bit character length. More... | |

| #define | USART_DATABITS_7 (0x02) |

| LCR:WLS 7-bit character length. More... | |

| #define | USART_DATABITS_8 (0x03) |

| LCR:WLS 8-bit character length. More... | |

| #define | USART_PSELPEN_ODD (0x01) |

| LCR:PSEL & LCR:PEN Odd parity. More... | |

| #define | USART_PSELPEN_EVEN (0x03) |

| LCR:PSEL & LCR:PEN Even parity. More... | |

| #define | USART_PSELPEN_FORCE1 (0x05) |

| LCR:PSEL & LCR:PEN Force 1 stick parity. More... | |

| #define | USART_PSELPEN_FORCE0 (0x07) |

| LCR:PSEL & LCR:PEN Force 0 stick parity. More... | |

| #define | USART_PARITY_DISABLE (0) |

| LCR:PSEL & LCR:PEN Disable parity. More... | |

| #define | USART_PARITY_ODD USART_PSELPEN_ODD |

| LCR:PSEL & LCR:PEN Odd parity. More... | |

| #define | USART_PARITY_EVEN USART_PSELPEN_EVEN |

| LCR:PSEL & LCR:PEN Even parity. More... | |

| #define | USART_PARITY_FORCE1 USART_PSELPEN_FORCE1 |

| LCR:PSEL & LCR:PEN Force 1 stick parity. More... | |

| #define | USART_PARITY_FORCE0 USART_PSELPEN_FORCE0 |

| LCR:PSEL & LCR:PEN Force 0 stick parity. More... | |

| #define | USART_STOPBITS_1 (0) |

| LCR:SBS Use 1 stop bit. More... | |

| #define | USART_STOPBITS_1P5 USART_LCR_SBS |

| LCR:SBS Use 1.5 stop bit when databits is 5. More... | |

| #define | USART_STOPBITS_2 USART_LCR_SBS |

| LCR:SBS Use 2 stop bits. More... | |

| #define | USART_LCR_WLS_MASK (3) |

| #define | USART_LCR_WLS(wls) ((wls) & USART_LCR_WLS_MASK) |

| Word length select: 5-8 databits. More... | |

| #define | USART_LCR_SBS BIT2 |

| Set LCR:SBS for 1.5 or 2 stop bits, Clear for 1 stop bit. More... | |

| #define | USART_LCR_PEN BIT3 |

| Enable parity checking. More... | |

| #define | USART_LCR_PSELPEN_MASK (7) |

| #define | USART_LCR_PSELPEN_SHIFT 3 |

| #define | USART_LCR_PSELPEN(psel) (((psel) & USART_LCR_PSELPEN_MASK) << USART_LCR_PSELPEN_SHIFT) |

| LCR:PSEL and LCR:PEN control parity. More... | |

| #define | USART_LCR_BCON BIT6 |

| Break Control: Enabling this bit forces TX to logic 0. More... | |

| #define | USART_LSR_RDR BIT0 |

| Receiver Data Ready. More... | |

| #define | USART_LSR_OE BIT1 |

| Overrun Error. More... | |

| #define | USART_LSR_PE BIT2 |

| Parity Error. More... | |

| #define | USART_LSR_FE BIT3 |

| Framing Error. More... | |

| #define | USART_LSR_BI BIT4 |

| Break Interrupt. More... | |

| #define | USART_LSR_THRE BIT5 |

| Transmitter Holding Register Empty. More... | |

| #define | USART_LSR_TEMT BIT6 |

| Transmitter Empty. More... | |

| #define | USART_LSR_RXFE BIT7 |

| Error in RX FIFO. More... | |

| #define | USART_TX_FIFO_DEPTH (16) |

| TX FIFO depth. More... | |

| #define | USART_RX_FIFO_DETPH (16) |

| RX FIFO depth. More... | |

| #define | USART_EFR_ENMODE BIT4 |

| Enable Enhanced Mode to use TX and RX FIFO trigger level interrupts. More... | |

Functions | |

| uint32_t | usart_set_baudrate (uint32_t usart, uint32_t baud) |

| USART Set Baudrate The baud rate is computed assuming a peripheral clock of 150MHz. More... | |

| void | usart_configure_lcr (uint32_t usart, uint8_t data_bits, uint8_t stop_bits, uint8_t parity) |

| USART Configure Line Control Register This register sets the data bits, stop bits, and parity. More... | |

| void | usart_break_enable (uint32_t usart) |

| Enable Break Control Enables break control bit that forces TX pin to logic low. More... | |

| void | usart_break_disable (uint32_t usart) |

| Disable Break Control Disables break control bit that forces TX pin to logic low. More... | |

| void | usart_enhanced_enable (uint32_t usart) |

| Enable Enhanced Mode Enable enhanced mode to generate interrupts when FIFO thresholds in FCR are reached. More... | |

| void | usart_enhanced_disable (uint32_t usart) |

| Disable Enhanced Mode Disable enhanced mode to generate interrupts when FIFO thresholds in FCR are reached. More... | |

| void | usart_set_fifo_depth (uint32_t usart, uint8_t tx_depth, uint8_t rx_depth) |

| Set the TX and RX FIFO depth. More... | |

| void | usart_send (uint32_t usart, uint8_t data) |

| Write byte to TX FIFO. More... | |

| uint8_t | usart_recv (uint32_t usart) |

| Read byte from the RX FIFO. More... | |

| void | usart_enable_rx_interrupt (uint32_t usart) |

| Enable RX Interrupts Enable both the Receive Data Available and Character Timeout interrupts. More... | |

| void | usart_disable_rx_interrupt (uint32_t usart) |

| Disable RX Interrupts Disable both the Receive Data Available and Character Timeout interrupts. More... | |

| void | usart_enable_tx_interrupt (uint32_t usart) |

| Enable TX Interrupt Enable the TX Holding Register Empty interrupt. More... | |

| void | usart_disable_tx_interrupt (uint32_t usart) |

| Disable TX Interrupt Disable the TX Holding Register Empty interrupt. More... | |

| void | usart_enable_rls_interrupt (uint32_t usart) |

| Enable RX Line Status Interrupt Enable the RX Line Status interrupt. More... | |

| void | usart_disable_rls_interrupt (uint32_t usart) |

| Disable RX Line Status Interrupt Disable the RX Line Status interrupt. More... | |

| void | usart_fifo_enable (uint32_t usart) |

| Enable FIFOs Enable both TX and RX FIFOs. More... | |

| void | usart_fifo_disable (uint32_t usart) |

| Disable FIFOs Disable both TX and RX FIFOs. More... | |

| void | usart_clear_tx_fifo (uint32_t usart) |

| Clear the TX FIFO Clears the TX FIFO. More... | |

| void | usart_clear_rx_fifo (uint32_t usart) |

| Clear the RX FIFO Clears the RX FIFO. More... | |