f4/rcc.h File Reference

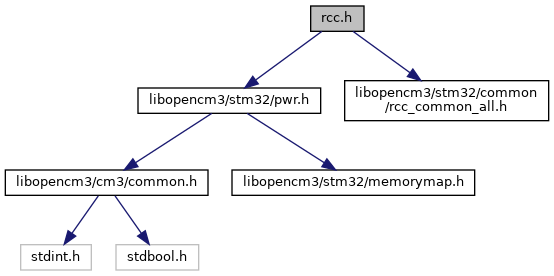

Include dependency graph for f4/rcc.h:

Go to the source code of this file.

Data Structures | |

| struct | rcc_clock_scale |

Enumerations | |

| enum | rcc_clock_3v3 { RCC_CLOCK_3V3_84MHZ , RCC_CLOCK_3V3_96MHZ , RCC_CLOCK_3V3_168MHZ , RCC_CLOCK_3V3_180MHZ , RCC_CLOCK_3V3_END } |

| enum | rcc_osc { RCC_PLL , RCC_PLLSAI , RCC_PLLI2S , RCC_HSE , RCC_HSI , RCC_LSE , RCC_LSI } |

| enum | rcc_periph_clken { RCC_GPIOA = _REG_BIT(0x30, 0) , RCC_GPIOB = _REG_BIT(0x30, 1) , RCC_GPIOC = _REG_BIT(0x30, 2) , RCC_GPIOD = _REG_BIT(0x30, 3) , RCC_GPIOE = _REG_BIT(0x30, 4) , RCC_GPIOF = _REG_BIT(0x30, 5) , RCC_GPIOG = _REG_BIT(0x30, 6) , RCC_GPIOH = _REG_BIT(0x30, 7) , RCC_GPIOI = _REG_BIT(0x30, 8) , RCC_GPIOJ = _REG_BIT(0x30, 9) , RCC_GPIOK = _REG_BIT(0x30, 10) , RCC_CRC = _REG_BIT(0x30, 12) , RCC_BKPSRAM = _REG_BIT(0x30, 18) , RCC_CCMDATARAM = _REG_BIT(0x30, 20) , RCC_DMA1 = _REG_BIT(0x30, 21) , RCC_DMA2 = _REG_BIT(0x30, 22) , RCC_DMA2D = _REG_BIT(0x30, 23) , RCC_ETHMAC = _REG_BIT(0x30, 25) , RCC_ETHMACTX = _REG_BIT(0x30, 26) , RCC_ETHMACRX = _REG_BIT(0x30, 27) , RCC_ETHMACPTP = _REG_BIT(0x30, 28) , RCC_OTGHS = _REG_BIT(0x30, 29) , RCC_OTGHSULPI = _REG_BIT(0x30, 30) , RCC_DCMI = _REG_BIT(0x34, 0) , RCC_CRYP = _REG_BIT(0x34, 4) , RCC_HASH = _REG_BIT(0x34, 5) , RCC_RNG = _REG_BIT(0x34, 6) , RCC_OTGFS = _REG_BIT(0x34, 7) , RCC_FSMC = _REG_BIT(0x38, 0) , RCC_FMC = _REG_BIT(0x38, 0) , RCC_QUADSPI = _REG_BIT(0x38, 1) , RCC_TIM2 = _REG_BIT(0x40, 0) , RCC_TIM3 = _REG_BIT(0x40, 1) , RCC_TIM4 = _REG_BIT(0x40, 2) , RCC_TIM5 = _REG_BIT(0x40, 3) , RCC_TIM6 = _REG_BIT(0x40, 4) , RCC_TIM7 = _REG_BIT(0x40, 5) , RCC_TIM12 = _REG_BIT(0x40, 6) , RCC_TIM13 = _REG_BIT(0x40, 7) , RCC_TIM14 = _REG_BIT(0x40, 8) , RCC_WWDG = _REG_BIT(0x40, 11) , RCC_SPI2 = _REG_BIT(0x40, 14) , RCC_SPI3 = _REG_BIT(0x40, 15) , RCC_USART2 = _REG_BIT(0x40, 17) , RCC_USART3 = _REG_BIT(0x40, 18) , RCC_UART4 = _REG_BIT(0x40, 19) , RCC_UART5 = _REG_BIT(0x40, 20) , RCC_I2C1 = _REG_BIT(0x40, 21) , RCC_I2C2 = _REG_BIT(0x40, 22) , RCC_I2C3 = _REG_BIT(0x40, 23) , RCC_CAN1 = _REG_BIT(0x40, 25) , RCC_CAN2 = _REG_BIT(0x40, 26) , RCC_PWR = _REG_BIT(0x40, 28) , RCC_DAC = _REG_BIT(0x40, 29) , RCC_UART7 = _REG_BIT(0x40, 30) , RCC_UART8 = _REG_BIT(0x40, 31) , RCC_TIM1 = _REG_BIT(0x44, 0) , RCC_TIM8 = _REG_BIT(0x44, 1) , RCC_USART1 = _REG_BIT(0x44, 4) , RCC_USART6 = _REG_BIT(0x44, 5) , RCC_ADC1 = _REG_BIT(0x44, 8) , RCC_ADC2 = _REG_BIT(0x44, 9) , RCC_ADC3 = _REG_BIT(0x44, 10) , RCC_SDIO = _REG_BIT(0x44, 11) , RCC_SPI1 = _REG_BIT(0x44, 12) , RCC_SPI4 = _REG_BIT(0x44, 13) , RCC_SYSCFG = _REG_BIT(0x44, 14) , RCC_TIM9 = _REG_BIT(0x44, 16) , RCC_TIM10 = _REG_BIT(0x44, 17) , RCC_TIM11 = _REG_BIT(0x44, 18) , RCC_SPI5 = _REG_BIT(0x44, 20) , RCC_SPI6 = _REG_BIT(0x44, 21) , RCC_SAI1EN = _REG_BIT(0x44, 22) , RCC_LTDC = _REG_BIT(0x44, 26) , RCC_DSI = _REG_BIT(0x44, 27) , RCC_RTC = _REG_BIT(0x70, 15) , SCC_GPIOA = _REG_BIT(0x50, 0) , SCC_GPIOB = _REG_BIT(0x50, 1) , SCC_GPIOC = _REG_BIT(0x50, 2) , SCC_GPIOD = _REG_BIT(0x50, 3) , SCC_GPIOE = _REG_BIT(0x50, 4) , SCC_GPIOF = _REG_BIT(0x50, 5) , SCC_GPIOG = _REG_BIT(0x50, 6) , SCC_GPIOH = _REG_BIT(0x50, 7) , SCC_GPIOI = _REG_BIT(0x50, 8) , SCC_GPIOJ = _REG_BIT(0x50, 9) , SCC_GPIOK = _REG_BIT(0x50, 10) , SCC_CRC = _REG_BIT(0x50, 12) , SCC_FLTIF = _REG_BIT(0x50, 15) , SCC_SRAM1 = _REG_BIT(0x50, 16) , SCC_SRAM2 = _REG_BIT(0x50, 17) , SCC_BKPSRAM = _REG_BIT(0x50, 18) , SCC_SRAM3 = _REG_BIT(0x50, 19) , SCC_DMA1 = _REG_BIT(0x50, 21) , SCC_DMA2 = _REG_BIT(0x50, 22) , SCC_DMA2D = _REG_BIT(0x50, 23) , SCC_ETHMAC = _REG_BIT(0x50, 25) , SCC_ETHMACTX = _REG_BIT(0x50, 26) , SCC_ETHMACRX = _REG_BIT(0x50, 27) , SCC_ETHMACPTP = _REG_BIT(0x50, 28) , SCC_OTGHS = _REG_BIT(0x50, 29) , SCC_OTGHSULPI = _REG_BIT(0x50, 30) , SCC_DCMI = _REG_BIT(0x54, 0) , SCC_CRYP = _REG_BIT(0x54, 4) , SCC_HASH = _REG_BIT(0x54, 5) , SCC_RNG = _REG_BIT(0x54, 6) , SCC_OTGFS = _REG_BIT(0x54, 7) , SCC_QSPIC = _REG_BIT(0x58, 1) , SCC_FMC = _REG_BIT(0x58, 0) , SCC_FSMC = _REG_BIT(0x58, 0) , SCC_TIM2 = _REG_BIT(0x60, 0) , SCC_TIM3 = _REG_BIT(0x60, 1) , SCC_TIM4 = _REG_BIT(0x60, 2) , SCC_TIM5 = _REG_BIT(0x60, 3) , SCC_TIM6 = _REG_BIT(0x60, 4) , SCC_TIM7 = _REG_BIT(0x60, 5) , SCC_TIM12 = _REG_BIT(0x60, 6) , SCC_TIM13 = _REG_BIT(0x60, 7) , SCC_TIM14 = _REG_BIT(0x60, 8) , SCC_WWDG = _REG_BIT(0x60, 11) , SCC_SPI2 = _REG_BIT(0x60, 14) , SCC_SPI3 = _REG_BIT(0x60, 15) , SCC_USART2 = _REG_BIT(0x60, 17) , SCC_USART3 = _REG_BIT(0x60, 18) , SCC_UART4 = _REG_BIT(0x60, 19) , SCC_UART5 = _REG_BIT(0x60, 20) , SCC_I2C1 = _REG_BIT(0x60, 21) , SCC_I2C2 = _REG_BIT(0x60, 22) , SCC_I2C3 = _REG_BIT(0x60, 23) , SCC_CAN1 = _REG_BIT(0x60, 25) , SCC_CAN2 = _REG_BIT(0x60, 26) , SCC_PWR = _REG_BIT(0x60, 28) , SCC_DAC = _REG_BIT(0x60, 29) , SCC_UART7 = _REG_BIT(0x60, 30) , SCC_UART8 = _REG_BIT(0x60, 31) , SCC_TIM1 = _REG_BIT(0x64, 0) , SCC_TIM8 = _REG_BIT(0x64, 1) , SCC_USART1 = _REG_BIT(0x64, 4) , SCC_USART6 = _REG_BIT(0x64, 5) , SCC_ADC1 = _REG_BIT(0x64, 8) , SCC_ADC2 = _REG_BIT(0x64, 9) , SCC_ADC3 = _REG_BIT(0x64, 10) , SCC_SDIO = _REG_BIT(0x64, 11) , SCC_SPI1 = _REG_BIT(0x64, 12) , SCC_SPI4 = _REG_BIT(0x64, 13) , SCC_SYSCFG = _REG_BIT(0x64, 14) , SCC_TIM9 = _REG_BIT(0x64, 16) , SCC_TIM10 = _REG_BIT(0x64, 17) , SCC_TIM11 = _REG_BIT(0x64, 18) , SCC_SPI5 = _REG_BIT(0x64, 20) , SCC_SPI6 = _REG_BIT(0x64, 21) , SCC_SAI1 = _REG_BIT(0x64, 22) , SCC_LTDC = _REG_BIT(0x64, 26) , SCC_DSI = _REG_BIT(0x64, 27) } |

| enum | rcc_periph_rst { RST_GPIOA = _REG_BIT(0x10, 0) , RST_GPIOB = _REG_BIT(0x10, 1) , RST_GPIOC = _REG_BIT(0x10, 2) , RST_GPIOD = _REG_BIT(0x10, 3) , RST_GPIOE = _REG_BIT(0x10, 4) , RST_GPIOF = _REG_BIT(0x10, 5) , RST_GPIOG = _REG_BIT(0x10, 6) , RST_GPIOH = _REG_BIT(0x10, 7) , RST_GPIOI = _REG_BIT(0x10, 8) , RST_GPIOJ = _REG_BIT(0x10, 9) , RST_GPIOK = _REG_BIT(0x10, 10) , RST_CRC = _REG_BIT(0x10, 12) , RST_DMA1 = _REG_BIT(0x10, 21) , RST_DMA2 = _REG_BIT(0x10, 22) , RST_DMA2D = _REG_BIT(0x10, 23) , RST_ETHMAC = _REG_BIT(0x10, 25) , RST_OTGHS = _REG_BIT(0x10, 29) , RST_DCMI = _REG_BIT(0x14, 0) , RST_CRYP = _REG_BIT(0x14, 4) , RST_HASH = _REG_BIT(0x14, 5) , RST_RNG = _REG_BIT(0x14, 6) , RST_OTGFS = _REG_BIT(0x14, 7) , RST_QSPI = _REG_BIT(0x18, 1) , RST_FSMC = _REG_BIT(0x18, 0) , RST_FMC = _REG_BIT(0x18, 0) , RST_TIM2 = _REG_BIT(0x20, 0) , RST_TIM3 = _REG_BIT(0x20, 1) , RST_TIM4 = _REG_BIT(0x20, 2) , RST_TIM5 = _REG_BIT(0x20, 3) , RST_TIM6 = _REG_BIT(0x20, 4) , RST_TIM7 = _REG_BIT(0x20, 5) , RST_TIM12 = _REG_BIT(0x20, 6) , RST_TIM13 = _REG_BIT(0x20, 7) , RST_TIM14 = _REG_BIT(0x20, 8) , RST_WWDG = _REG_BIT(0x20, 11) , RST_SPI2 = _REG_BIT(0x20, 14) , RST_SPI3 = _REG_BIT(0x20, 15) , RST_USART2 = _REG_BIT(0x20, 17) , RST_USART3 = _REG_BIT(0x20, 18) , RST_UART4 = _REG_BIT(0x20, 19) , RST_UART5 = _REG_BIT(0x20, 20) , RST_I2C1 = _REG_BIT(0x20, 21) , RST_I2C2 = _REG_BIT(0x20, 22) , RST_I2C3 = _REG_BIT(0x20, 23) , RST_CAN1 = _REG_BIT(0x20, 25) , RST_CAN2 = _REG_BIT(0x20, 26) , RST_PWR = _REG_BIT(0x20, 28) , RST_DAC = _REG_BIT(0x20, 29) , RST_UART7 = _REG_BIT(0x20, 30) , RST_UART8 = _REG_BIT(0x20, 31) , RST_TIM1 = _REG_BIT(0x24, 0) , RST_TIM8 = _REG_BIT(0x24, 1) , RST_USART1 = _REG_BIT(0x24, 4) , RST_USART6 = _REG_BIT(0x24, 5) , RST_ADC = _REG_BIT(0x24, 8) , RST_SDIO = _REG_BIT(0x24, 11) , RST_SPI1 = _REG_BIT(0x24, 12) , RST_SPI4 = _REG_BIT(0x24, 13) , RST_SYSCFG = _REG_BIT(0x24, 14) , RST_TIM9 = _REG_BIT(0x24, 16) , RST_TIM10 = _REG_BIT(0x24, 17) , RST_TIM11 = _REG_BIT(0x24, 18) , RST_SPI5 = _REG_BIT(0x24, 20) , RST_SPI6 = _REG_BIT(0x24, 21) , RST_SAI1RST = _REG_BIT(0x24, 22) , RST_LTDC = _REG_BIT(0x24, 26) , RST_DSI = _REG_BIT(0x24, 27) , RST_BDCR = _REG_BIT(0x70, 16) } |

Functions | |

| void | rcc_osc_ready_int_clear (enum rcc_osc osc) |

| void | rcc_osc_ready_int_enable (enum rcc_osc osc) |

| void | rcc_osc_ready_int_disable (enum rcc_osc osc) |

| int | rcc_osc_ready_int_flag (enum rcc_osc osc) |

| void | rcc_css_int_clear (void) |

| int | rcc_css_int_flag (void) |

| void | rcc_wait_for_sysclk_status (enum rcc_osc osc) |

| void | rcc_osc_on (enum rcc_osc osc) |

| void | rcc_osc_off (enum rcc_osc osc) |

| void | rcc_css_enable (void) |

| void | rcc_css_disable (void) |

| void | rcc_plli2s_config (uint16_t n, uint8_t r) |

| Set the dividers for the PLLI2S clock outputs. More... | |

| void | rcc_pllsai_config (uint16_t n, uint16_t p, uint16_t q, uint16_t r) |

| Set the dividers for the PLLSAI clock outputs divider p is only available on F4x9 parts, pass 0 for other parts. More... | |

| void | rcc_pllsai_postscalers (uint8_t q, uint8_t r) |

| Set the dedicated dividers after the PLLSAI configuration. More... | |

| void | rcc_set_sysclk_source (uint32_t clk) |

| void | rcc_set_pll_source (uint32_t pllsrc) |

| void | rcc_set_ppre2 (uint32_t ppre2) |

| void | rcc_set_ppre1 (uint32_t ppre1) |

| void | rcc_set_hpre (uint32_t hpre) |

| void | rcc_set_rtcpre (uint32_t rtcpre) |

| void | rcc_set_main_pll_hsi (uint32_t pllm, uint32_t plln, uint32_t pllp, uint32_t pllq, uint32_t pllr) |

| Reconfigures the main PLL for a HSI source. More... | |

| void | rcc_set_main_pll_hse (uint32_t pllm, uint32_t plln, uint32_t pllp, uint32_t pllq, uint32_t pllr) |

| Reconfigures the main PLL for a HSE source. More... | |

| uint32_t | rcc_system_clock_source (void) |

| void | rcc_clock_setup_pll (const struct rcc_clock_scale *clock) |

| Setup clocks to run from PLL. More... | |

| void | rcc_clock_setup_hse_3v3 (const struct rcc_clock_scale *clock) |

| Setup clocks with the HSE. More... | |

| uint32_t | rcc_get_usart_clk_freq (uint32_t usart) |

| Get the peripheral clock speed for the USART at base specified. More... | |

| uint32_t | rcc_get_timer_clk_freq (uint32_t timer) |

| Get the peripheral clock speed for the Timer at base specified. More... | |

| uint32_t | rcc_get_i2c_clk_freq (uint32_t i2c) |

| Get the peripheral clock speed for the I2C device at base specified. More... | |

| uint32_t | rcc_get_spi_clk_freq (uint32_t spi) |

| Get the peripheral clock speed for the SPI device at base specified. More... | |

Variables | |

| uint32_t | rcc_ahb_frequency |

| uint32_t | rcc_apb1_frequency |

| uint32_t | rcc_apb2_frequency |

| const struct rcc_clock_scale | rcc_hsi_configs [RCC_CLOCK_3V3_END] |

| const struct rcc_clock_scale | rcc_hse_8mhz_3v3 [RCC_CLOCK_3V3_END] |

| const struct rcc_clock_scale | rcc_hse_12mhz_3v3 [RCC_CLOCK_3V3_END] |

| const struct rcc_clock_scale | rcc_hse_16mhz_3v3 [RCC_CLOCK_3V3_END] |

| const struct rcc_clock_scale | rcc_hse_25mhz_3v3 [RCC_CLOCK_3V3_END] |