systemcontrol.h File Reference

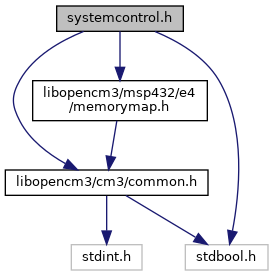

Include dependency graph for systemcontrol.h:

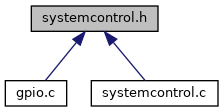

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Macros | |

| #define | SYSCTL_DID0 MMIO32(SYSCTL_BASE + 0x000) |

| Device Identification 0. More... | |

| #define | SYSCTL_DID1 MMIO32(SYSCTL_BASE + 0x004) |

| Device Identification 1. More... | |

| #define | SYSCTL_PTBOCTL MMIO32(SYSCTL_BASE + 0x038) |

| Power-Temp Brownout Control. More... | |

| #define | SYSCTL_RIS MMIO32(SYSCTL_BASE + 0x050) |

| Raw Interrupt Status. More... | |

| #define | SYSCTL_IMC MMIO32(SYSCTL_BASE + 0x054) |

| Interrupt Mask Control. More... | |

| #define | SYSCTL_MISC MMIO32(SYSCTL_BASE + 0x058) |

| RW1C Masked Interrupt Status and Clear. More... | |

| #define | SYSCTL_RESC MMIO32(SYSCTL_BASE + 0x05C) |

| Reset Cause. More... | |

| #define | SYSCTL_PWRTC MMIO32(SYSCTL_BASE + 0x060) |

| RW1C Power-Temperature Cause. More... | |

| #define | SYSCTL_NMIC MMIO32(SYSCTL_BASE + 0x064) |

| NMI Cause Register. More... | |

| #define | SYSCTL_MOSCCTL MMIO32(SYSCTL_BASE + 0x07C) |

| Main Oscillator Control. More... | |

| #define | SYSCTL_RSCLKCFG MMIO32(SYSCTL_BASE + 0x0B0) |

| Run and Sleep Mode Configuration Register. More... | |

| #define | SYSCTL_MEMTIM0 MMIO32(SYSCTL_BASE + 0x0C0) |

| Memory Timing Parameter Register 0 for Main Flash and EEPROM. More... | |

| #define | SYSCTL_ALTCLKCFG MMIO32(SYSCTL_BASE + 0x138) |

| Alternate Clock Configuration. More... | |

| #define | SYSCTL_DSCLKCFG MMIO32(SYSCTL_BASE + 0x144) |

| Deep Sleep Clock Configuration Register. More... | |

| #define | SYSCTL_DIVSCLK MMIO32(SYSCTL_BASE + 0x148) |

| Divisor and Source Clock Configuration. More... | |

| #define | SYSCTL_SYSPROP MMIO32(SYSCTL_BASE + 0x14C) |

| System Properties. More... | |

| #define | SYSCTL_PIOSCCAL MMIO32(SYSCTL_BASE + 0x150) |

| Precision Internal Oscillator Calibration. More... | |

| #define | SYSCTL_PIOSCSTAT MMIO32(SYSCTL_BASE + 0x154) |

| Precision Internal Oscillator Statistics. More... | |

| #define | SYSCTL_PLLFREQ0 MMIO32(SYSCTL_BASE + 0x160) |

| PLL Frequency 0. More... | |

| #define | SYSCTL_PLLFREQ1 MMIO32(SYSCTL_BASE + 0x164) |

| PLL Frequency 1. More... | |

| #define | SYSCTL_PLLSTAT MMIO32(SYSCTL_BASE + 0x168) |

| PLL Status. More... | |

| #define | SYSCTL_SLPPWRCFG MMIO32(SYSCTL_BASE + 0x188) |

| Sleep Power Configuration. More... | |

| #define | SYSCTL_DSLPPWRCFG MMIO32(SYSCTL_BASE + 0x18C) |

| Deep-Sleep Power Configuration. More... | |

| #define | SYSCTL_NVMSTAT MMIO32(SYSCTL_BASE + 0x1A0) |

| Non-Volatile Memory Information. More... | |

| #define | SYSCTL_LDOSPCTL MMIO32(SYSCTL_BASE + 0x1B4) |

| LDO Sleep Power Control. More... | |

| #define | SYSCTL_LDOSPCAL MMIO32(SYSCTL_BASE + 0x1B8) |

| LDO Sleep Power Calibration. More... | |

| #define | SYSCTL_LDODPCTL MMIO32(SYSCTL_BASE + 0x1BC) |

| LDO Deep-Sleep Power Control. More... | |

| #define | SYSCTL_LDODPCAL MMIO32(SYSCTL_BASE + 0x1C0) |

| LDO Deep-Sleep Power Calibration. More... | |

| #define | SYSCTL_SDPMST MMIO32(SYSCTL_BASE + 0x1CC) |

| Sleep / Deep-Sleep Power Mode Status. More... | |

| #define | SYSCTL_RESBEHAVCTL MMIO32(SYSCTL_BASE + 0x1D8) |

| Reset Behavior Control Register. More... | |

| #define | SYSCTL_HSSR MMIO32(SYSCTL_BASE + 0x1F4) |

| Hardware System Service Request. More... | |

| #define | SYSCTL_USBPDS MMIO32(SYSCTL_BASE + 0x280) |

| USB Power Domain Status. More... | |

| #define | SYSCTL_USBMPC MMIO32(SYSCTL_BASE + 0x284) |

| USB Memory Power Control. More... | |

| #define | SYSCTL_EMACPDS MMIO32(SYSCTL_BASE + 0x288) |

| Ethernet MAC Power Domain Status. More... | |

| #define | SYSCTL_EMACMPC MMIO32(SYSCTL_BASE + 0x28C) |

| Ethernet MAC Memory Power Control. More... | |

| #define | SYSCTL_LCDPDS MMIO32(SYSCTL_BASE + 0x290) |

| LCD Power Domain Status. More... | |

| #define | SYSCTL_LCDMPC MMIO32(SYSCTL_BASE + 0x294) |

| LCD Memory Power Control. More... | |

| #define | SYSCTL_CAN0PDS MMIO32(SYSCTL_BASE + 0x298) |

| CAN 0 Power Domain Status. More... | |

| #define | SYSCTL_CAN0MPC MMIO32(SYSCTL_BASE + 0x29C) |

| CAN 0 Memory Power Control. More... | |

| #define | SYSCTL_CAN1PDS MMIO32(SYSCTL_BASE + 0x2A0) |

| CAN 1 Power Domain Status. More... | |

| #define | SYSCTL_CAN1MPC MMIO32(SYSCTL_BASE + 0x2A4) |

| CAN 1 Memory Power Control. More... | |

| #define | SYSCTL_PPWD MMIO32(SYSCTL_BASE + 0x300) |

| Watchdog Timer Peripheral Present. More... | |

| #define | SYSCTL_PPTIMER MMIO32(SYSCTL_BASE + 0x304) |

| 16/32-Bit General-Purpose Timer Peripheral Present More... | |

| #define | SYSCTL_PPGPIO MMIO32(SYSCTL_BASE + 0x308) |

| General-Purpose Input/Output Peripheral Present. More... | |

| #define | SYSCTL_PPDMA MMIO32(SYSCTL_BASE + 0x30C) |

| Micro Direct Memory Access Peripheral Present. More... | |

| #define | SYSCTL_PPEPI MMIO32(SYSCTL_BASE + 0x310) |

| EPI Peripheral Present. More... | |

| #define | SYSCTL_PPHIB MMIO32(SYSCTL_BASE + 0x314) |

| Hibernation Peripheral Present. More... | |

| #define | SYSCTL_PPUART MMIO32(SYSCTL_BASE + 0x318) |

| Universal Asynchronous Receiver/Transmitter Peripheral Present. More... | |

| #define | SYSCTL_PPSSI MMIO32(SYSCTL_BASE + 0x31C) |

| Synchronous Serial Interface Peripheral Present. More... | |

| #define | SYSCTL_PPI2C MMIO32(SYSCTL_BASE + 0x320) |

| Inter-Integrated Circuit Peripheral Present. More... | |

| #define | SYSCTL_PPUSB MMIO32(SYSCTL_BASE + 0x328) |

| Universal Serial Bus Peripheral Present. More... | |

| #define | SYSCTL_PPEPHY MMIO32(SYSCTL_BASE + 0x330) |

| Ethernet PHY Peripheral Present. More... | |

| #define | SYSCTL_PPCAN MMIO32(SYSCTL_BASE + 0x334) |

| Controller Area Network Peripheral Present. More... | |

| #define | SYSCTL_PPADC MMIO32(SYSCTL_BASE + 0x338) |

| Analog-to-Digital Converter Peripheral Present. More... | |

| #define | SYSCTL_PPACMP MMIO32(SYSCTL_BASE + 0x33C) |

| Analog Comparator Peripheral Present. More... | |

| #define | SYSCTL_PPPWM MMIO32(SYSCTL_BASE + 0x340) |

| Pulse Width Modulator Peripheral Present. More... | |

| #define | SYSCTL_PPQEI MMIO32(SYSCTL_BASE + 0x344) |

| Quadrature Encoder Interface Peripheral Present. More... | |

| #define | SYSCTL_PPEEPROM MMIO32(SYSCTL_BASE + 0x358) |

| EEPROM Peripheral Present. More... | |

| #define | SYSCTL_PPCCM MMIO32(SYSCTL_BASE + 0x374) |

| CRC and Cryptographic Modules Peripheral Present. More... | |

| #define | SYSCTL_PPLCD MMIO32(SYSCTL_BASE + 0x390) |

| LCD Peripheral Present. More... | |

| #define | SYSCTL_PPOWIRE MMIO32(SYSCTL_BASE + 0x398) |

| 1-Wire Peripheral Present More... | |

| #define | SYSCTL_PPEMAC MMIO32(SYSCTL_BASE + 0x39C) |

| Ethernet MAC Peripheral Present. More... | |

| #define | SYSCTL_PPPRB MMIO32(SYSCTL_BASE + 0x3A0) |

| Power Regulator Bus Peripheral Present. More... | |

| #define | SYSCTL_SRWD MMIO32(SYSCTL_BASE + 0x500) |

| Watchdog Timer Software Reset. More... | |

| #define | SYSCTL_SRTIMER MMIO32(SYSCTL_BASE + 0x504) |

| 16/32-Bit General-Purpose Timer Software Reset More... | |

| #define | SYSCTL_SRGPIO MMIO32(SYSCTL_BASE + 0x508) |

| General-Purpose Input/Output Software Reset. More... | |

| #define | SYSCTL_SRDMA MMIO32(SYSCTL_BASE + 0x50C) |

| Micro Direct Memory Access Software Reset. More... | |

| #define | SYSCTL_SREPI MMIO32(SYSCTL_BASE + 0x510) |

| EPI Software Reset. More... | |

| #define | SYSCTL_SRHIB MMIO32(SYSCTL_BASE + 0x514) |

| Hibernation Software Reset. More... | |

| #define | SYSCTL_SRUART MMIO32(SYSCTL_BASE + 0x518) |

| Universal Asynchronous Receiver/Transmitter Software Reset. More... | |

| #define | SYSCTL_SRSSI MMIO32(SYSCTL_BASE + 0x51C) |

| Synchronous Serial Interface Software Reset. More... | |

| #define | SYSCTL_SRI2C MMIO32(SYSCTL_BASE + 0x520) |

| Inter-Integrated Circuit Software Reset. More... | |

| #define | SYSCTL_SRUSB MMIO32(SYSCTL_BASE + 0x528) |

| Universal Serial Bus Software Reset. More... | |

| #define | SYSCTL_SREPHY MMIO32(SYSCTL_BASE + 0x530) |

| Ethernet PHY Software Reset. More... | |

| #define | SYSCTL_SRCAN MMIO32(SYSCTL_BASE + 0x534) |

| Controller Area Network Software Reset. More... | |

| #define | SYSCTL_SRADC MMIO32(SYSCTL_BASE + 0x538) |

| Analog-to-Digital Converter Software Reset. More... | |

| #define | SYSCTL_SRACMP MMIO32(SYSCTL_BASE + 0x53C) |

| Analog Comparator Software Reset. More... | |

| #define | SYSCTL_SRPWM MMIO32(SYSCTL_BASE + 0x540) |

| Pulse Width Modulator Software Reset. More... | |

| #define | SYSCTL_SRQEI MMIO32(SYSCTL_BASE + 0x544) |

| Quadrature Encoder Interface Software Reset. More... | |

| #define | SYSCTL_SREEPROM MMIO32(SYSCTL_BASE + 0x558) |

| EEPROM Software Reset. More... | |

| #define | SYSCTL_SRCCM MMIO32(SYSCTL_BASE + 0x574) |

| CRC and Cryptographic Modules Software Reset. More... | |

| #define | SYSCTL_SRLCD MMIO32(SYSCTL_BASE + 0x590) |

| LCD Controller Software Reset. More... | |

| #define | SYSCTL_SROWIRE MMIO32(SYSCTL_BASE + 0x598) |

| 1-Wire Software Reset More... | |

| #define | SYSCTL_SREMAC MMIO32(SYSCTL_BASE + 0x59C) |

| Ethernet MAC Software Reset. More... | |

| #define | SYSCTL_RCGCWD MMIO32(SYSCTL_BASE + 0x600) |

| Watchdog Timer Run Mode Clock Gating Control. More... | |

| #define | SYSCTL_RCGCTIMER MMIO32(SYSCTL_BASE + 0x604) |

| 16/32-BitGeneral-Purpose Timer RunMode Clock Gating Control More... | |

| #define | SYSCTL_RCGCGPIO MMIO32(SYSCTL_BASE + 0x608) |

| General-Purpose Input/Output Run Mode Clock Gating Control. More... | |

| #define | SYSCTL_RCGCDMA MMIO32(SYSCTL_BASE + 0x60C) |

| Micro Direct Memory Access Run Mode Clock Gating Control. More... | |

| #define | SYSCTL_RCGCEPI MMIO32(SYSCTL_BASE + 0x610) |

| EPI Run Mode Clock Gating Control. More... | |

| #define | SYSCTL_RCGCHIB MMIO32(SYSCTL_BASE + 0x614) |

| Hibernation Run Mode Clock Gating Control. More... | |

| #define | SYSCTL_RCGCUART MMIO32(SYSCTL_BASE + 0x618) |

| Universal Asynchronous Receiver/Transmitter RunMode Clock Gating Control. More... | |

| #define | SYSCTL_RCGCSSI MMIO32(SYSCTL_BASE + 0x61C) |

| Synchronous Serial Interface Run Mode Clock Gating Control. More... | |

| #define | SYSCTL_RCGCI2C MMIO32(SYSCTL_BASE + 0x620) |

| Inter-Integrated Circuit Run Mode Clock Gating Control. More... | |

| #define | SYSCTL_RCGCUSB MMIO32(SYSCTL_BASE + 0x628) |

| Universal Serial Bus Run Mode Clock Gating Control. More... | |

| #define | SYSCTL_RCGCEPHY MMIO32(SYSCTL_BASE + 0x630) |

| Ethernet PHY Run Mode Clock Gating Control. More... | |

| #define | SYSCTL_RCGCCAN MMIO32(SYSCTL_BASE + 0x634) |

| Controller Area Network RunMode Clock Gating Control. More... | |

| #define | SYSCTL_RCGCADC MMIO32(SYSCTL_BASE + 0x638) |

| Analog-to-Digital Converter Run Mode Clock Gating Control. More... | |

| #define | SYSCTL_RCGCACMP MMIO32(SYSCTL_BASE + 0x63C) |

| Analog Comparator Run Mode Clock Gating Control. More... | |

| #define | SYSCTL_RCGCPWM MMIO32(SYSCTL_BASE + 0x640) |

| Pulse Width Modulator Run Mode Clock Gating Control. More... | |

| #define | SYSCTL_RCGCQEI MMIO32(SYSCTL_BASE + 0x644) |

| Quadrature Encoder Interface Run Mode Clock Gating Control. More... | |

| #define | SYSCTL_RCGCEEPROM MMIO32(SYSCTL_BASE + 0x658) |

| EEPROM Run Mode Clock Gating Control. More... | |

| #define | SYSCTL_RCGCCCM MMIO32(SYSCTL_BASE + 0x674) |

| CRC and CryptographicModules RunMode ClockGating Control. More... | |

| #define | SYSCTL_RCGCLCD MMIO32(SYSCTL_BASE + 0x690) |

| LCD Controller Run Mode Clock Gating Control. More... | |

| #define | SYSCTL_RCGCOWIRE MMIO32(SYSCTL_BASE + 0x698) |

| 1-Wire Run Mode Clock Gating Control More... | |

| #define | SYSCTL_RCGCEMAC MMIO32(SYSCTL_BASE + 0x69C) |

| Ethernet MAC Run Mode Clock Gating Control. More... | |

| #define | SYSCTL_SCGCWD MMIO32(SYSCTL_BASE + 0x700) |

| Watchdog Timer Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_SCGCTIMER MMIO32(SYSCTL_BASE + 0x704) |

| 16/32-Bit General-Purpose Timer Sleep Mode Clock Gating Control More... | |

| #define | SYSCTL_SCGCGPIO MMIO32(SYSCTL_BASE + 0x708) |

| General-Purpose Input/Output Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_SCGCDMA MMIO32(SYSCTL_BASE + 0x70C) |

| Micro Direct Memory Access Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_SCGCEPI MMIO32(SYSCTL_BASE + 0x710) |

| EPI Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_SCGCHIB MMIO32(SYSCTL_BASE + 0x714) |

| Hibernation Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_SCGCUART MMIO32(SYSCTL_BASE + 0x718) |

| Universal Asynchronous Receiver/Transmitter S Mode Clock Gating Control. More... | |

| #define | SYSCTL_SCGCSSI MMIO32(SYSCTL_BASE + 0x71C) |

| Synchronous Serial Interface Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_SCGCI2C MMIO32(SYSCTL_BASE + 0x720) |

| Inter-Integrated Circuit Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_SCGCUSB MMIO32(SYSCTL_BASE + 0x728) |

| Universal Serial Bus Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_SCGCEPHY MMIO32(SYSCTL_BASE + 0x730) |

| Ethernet PHY Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_SCGCCAN MMIO32(SYSCTL_BASE + 0x734) |

| Controller Area Network Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_SCGCADC MMIO32(SYSCTL_BASE + 0x738) |

| Analog-to-Digital Converter Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_SCGCACMP MMIO32(SYSCTL_BASE + 0x73C) |

| Analog Comparator Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_SCGCPWM MMIO32(SYSCTL_BASE + 0x740) |

| PulseWidthModulator Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_SCGCQEI MMIO32(SYSCTL_BASE + 0x744) |

| Quadrature Encoder Interface Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_SCGCEEPROM MMIO32(SYSCTL_BASE + 0x758) |

| EEPROM Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_SCGCCCM MMIO32(SYSCTL_BASE + 0x774) |

| CRC and Cryptographic Modules Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_SCGCLCD MMIO32(SYSCTL_BASE + 0x790) |

| LCD Controller Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_SCGCOWIRE MMIO32(SYSCTL_BASE + 0x798) |

| 1-Wire Sleep Mode Clock Gating Control More... | |

| #define | SYSCTL_SCGCEMAC MMIO32(SYSCTL_BASE + 0x79C) |

| Ethernet MAC Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_DCGCWD MMIO32(SYSCTL_BASE + 0x800) |

| Watchdog Timer Deep-SleepMode Clock Gating Control. More... | |

| #define | SYSCTL_DCGCTIMER MMIO32(SYSCTL_BASE + 0x804) |

| Clock 16/32-Bit General-Purpose Timer Deep-Sleep Mode Gating Control. More... | |

| #define | SYSCTL_DCGCGPIO MMIO32(SYSCTL_BASE + 0x808) |

| General-Purpose Input/Output Deep-Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_DCGCDMA MMIO32(SYSCTL_BASE + 0x80C) |

| Micro Direct Memory Access Deep-Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_DCGCEPI MMIO32(SYSCTL_BASE + 0x810) |

| EPI Deep-Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_DCGCHIB MMIO32(SYSCTL_BASE + 0x814) |

| Hibernation Deep-Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_DCGCUART MMIO32(SYSCTL_BASE + 0x818) |

| Universal Asynchronous Receiver/Transmitter D-S Mode Clock Gating Control. More... | |

| #define | SYSCTL_DCGCSSI MMIO32(SYSCTL_BASE + 0x81C) |

| Synchronous Serial Interface Deep-Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_DCGCI2C MMIO32(SYSCTL_BASE + 0x820) |

| Inter-Integrated Circuit Deep-Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_DCGCUSB MMIO32(SYSCTL_BASE + 0x828) |

| Universal Serial Bus Deep-Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_DCGCEPHY MMIO32(SYSCTL_BASE + 0x830) |

| Ethernet PHY Deep-Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_DCGCCAN MMIO32(SYSCTL_BASE + 0x834) |

| Controller Area Network Deep-SleepMode Clock Gating Control. More... | |

| #define | SYSCTL_DCGCADC MMIO32(SYSCTL_BASE + 0x838) |

| Analog-to-Digital Converter Deep-Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_DCGCACMP MMIO32(SYSCTL_BASE + 0x83C) |

| Analog Comparator Deep-Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_DCGCPWM MMIO32(SYSCTL_BASE + 0x840) |

| Pulse Width Modulator Deep-Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_DCGCQEI MMIO32(SYSCTL_BASE + 0x844) |

| Quadrature Encoder Interface Deep-Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_DCGCEEPROM MMIO32(SYSCTL_BASE + 0x858) |

| EEPROM Deep-Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_DCGCCCM MMIO32(SYSCTL_BASE + 0x874) |

| CRC and Cryptographic Modules Deep-Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_DCGCLCD MMIO32(SYSCTL_BASE + 0x890) |

| LCD Controller Deep-Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_DCGCOWIRE MMIO32(SYSCTL_BASE + 0x898) |

| 1-Wire Deep-Sleep Mode Clock Gating Control More... | |

| #define | SYSCTL_DCGCEMAC MMIO32(SYSCTL_BASE + 0x89C) |

| Ethernet MAC Deep-Sleep Mode Clock Gating Control. More... | |

| #define | SYSCTL_PCWD MMIO32(SYSCTL_BASE + 0x900) |

| Watchdog Timer Power Control. More... | |

| #define | SYSCTL_PCTIMER MMIO32(SYSCTL_BASE + 0x904) |

| 16/32-Bit General-Purpose Timer Power Control More... | |

| #define | SYSCTL_PCGPIO MMIO32(SYSCTL_BASE + 0x908) |

| General-Purpose Input/Output Power Control. More... | |

| #define | SYSCTL_PCDMA MMIO32(SYSCTL_BASE + 0x90C) |

| Micro Direct Memory Access Power Control. More... | |

| #define | SYSCTL_PCEPI MMIO32(SYSCTL_BASE + 0x910) |

| External Peripheral Interface Power Control. More... | |

| #define | SYSCTL_PCHIB MMIO32(SYSCTL_BASE + 0x914) |

| Hibernation Power Control. More... | |

| #define | SYSCTL_PCUART MMIO32(SYSCTL_BASE + 0x918) |

| Universal Asynchronous Receiver/Transmitter Power Control. More... | |

| #define | SYSCTL_PCSSI MMIO32(SYSCTL_BASE + 0x91C) |

| Synchronous Serial Interface Power Control. More... | |

| #define | SYSCTL_PCI2C MMIO32(SYSCTL_BASE + 0x920) |

| Inter-Integrated Circuit Power Control. More... | |

| #define | SYSCTL_PCUSB MMIO32(SYSCTL_BASE + 0x928) |

| Universal Serial Bus Power Control. More... | |

| #define | SYSCTL_PCEPHY MMIO32(SYSCTL_BASE + 0x930) |

| Ethernet PHY Power Control. More... | |

| #define | SYSCTL_PCCAN MMIO32(SYSCTL_BASE + 0x934) |

| Controller Area Network Power Control. More... | |

| #define | SYSCTL_PCADC MMIO32(SYSCTL_BASE + 0x938) |

| Analog-to-Digital Converter Power Control. More... | |

| #define | SYSCTL_PCACMP MMIO32(SYSCTL_BASE + 0x93C) |

| Analog Comparator Power Control. More... | |

| #define | SYSCTL_PCPWM MMIO32(SYSCTL_BASE + 0x940) |

| Pulse Width Modulator Power Control. More... | |

| #define | SYSCTL_PCQEI MMIO32(SYSCTL_BASE + 0x944) |

| Quadrature Encoder Interface Power Control. More... | |

| #define | SYSCTL_PCEEPROM MMIO32(SYSCTL_BASE + 0x958) |

| EEPROM Power Control. More... | |

| #define | SYSCTL_PCCCM MMIO32(SYSCTL_BASE + 0x974) |

| CRC and Cryptographic Modules Power Control. More... | |

| #define | SYSCTL_PCLCD MMIO32(SYSCTL_BASE + 0x990) |

| LCD Controller Power Control. More... | |

| #define | SYSCTL_PCOWIRE MMIO32(SYSCTL_BASE + 0x998) |

| 1-Wire Power Control More... | |

| #define | SYSCTL_PCEMAC MMIO32(SYSCTL_BASE + 0x99C) |

| Ethernet MAC Power Control. More... | |

| #define | SYSCTL_PRWD MMIO32(SYSCTL_BASE + 0xA00) |

| Watchdog Timer Peripheral Ready. More... | |

| #define | SYSCTL_PRTIMER MMIO32(SYSCTL_BASE + 0xA04) |

| 16/32-Bit General-Purpose Timer Peripheral Ready More... | |

| #define | SYSCTL_PRGPIO MMIO32(SYSCTL_BASE + 0xA08) |

| General-Purpose Input/Output Peripheral Ready. More... | |

| #define | SYSCTL_PRDMA MMIO32(SYSCTL_BASE + 0xA0C) |

| Micro Direct Memory Access Peripheral Ready. More... | |

| #define | SYSCTL_PREPI MMIO32(SYSCTL_BASE + 0xA10) |

| EPI Peripheral Ready. More... | |

| #define | SYSCTL_PRHIB MMIO32(SYSCTL_BASE + 0xA14) |

| Hibernation Peripheral Ready. More... | |

| #define | SYSCTL_PRUART MMIO32(SYSCTL_BASE + 0xA18) |

| Universal Asynchronous Receiver/Transmitter Peripheral Ready. More... | |

| #define | SYSCTL_PRSSI MMIO32(SYSCTL_BASE + 0xA1C) |

| Synchronous Serial Interface Peripheral Ready. More... | |

| #define | SYSCTL_PRI2C MMIO32(SYSCTL_BASE + 0xA20) |

| Inter-Integrated Circuit Peripheral Ready. More... | |

| #define | SYSCTL_PRUSB MMIO32(SYSCTL_BASE + 0xA28) |

| Universal Serial Bus Peripheral Ready. More... | |

| #define | SYSCTL_PREPHY MMIO32(SYSCTL_BASE + 0xA30) |

| Ethernet PHY Peripheral Ready. More... | |

| #define | SYSCTL_PRCAN MMIO32(SYSCTL_BASE + 0xA34) |

| Controller Area Network Peripheral Ready. More... | |

| #define | SYSCTL_PRADC MMIO32(SYSCTL_BASE + 0xA38) |

| Analog-to-Digital Converter Peripheral Ready. More... | |

| #define | SYSCTL_PRACMP MMIO32(SYSCTL_BASE + 0xA3C) |

| Analog Comparator Peripheral Ready. More... | |

| #define | SYSCTL_PRPWM MMIO32(SYSCTL_BASE + 0xA40) |

| Pulse Width Modulator Peripheral Ready. More... | |

| #define | SYSCTL_PRQEI MMIO32(SYSCTL_BASE + 0xA44) |

| Quadrature Encoder Interface Peripheral Ready. More... | |

| #define | SYSCTL_PREEPROM MMIO32(SYSCTL_BASE + 0xA58) |

| EEPROM Peripheral Ready. More... | |

| #define | SYSCTL_PRCCM MMIO32(SYSCTL_BASE + 0xA74) |

| CRC and Cryptographic Modules Peripheral Ready. More... | |

| #define | SYSCTL_PRLCD MMIO32(SYSCTL_BASE + 0xA90) |

| LCD Controller Peripheral Ready. More... | |

| #define | SYSCTL_PROWIRE MMIO32(SYSCTL_BASE + 0xA98) |

| 1-Wire Peripheral Ready More... | |

| #define | SYSCTL_PREMAC MMIO32(SYSCTL_BASE + 0xA9C) |

| Ethernet MAC Peripheral Ready. More... | |

| #define | SYSCTL_UNIQUEID0 MMIO32(SYSCTL_BASE + 0xF20) |

| Unique ID 0. More... | |

| #define | SYSCTL_UNIQUEID1 MMIO32(SYSCTL_BASE + 0xF24) |

| Unique ID 1. More... | |

| #define | SYSCTL_UNIQUEID2 MMIO32(SYSCTL_BASE + 0xF28) |

| Unique ID 2. More... | |

| #define | SYSCTL_UNIQUEID3 MMIO32(SYSCTL_BASE + 0xF2C) |

| Unique ID 3. More... | |

| #define | SYSCTL_DID0_VER_SHIFT (28) |

| DID0 Version Shift. More... | |

| #define | SYSCTL_DID0_VER_MASK (0x7) |

| DID0 Version Mask. More... | |

| #define | SYSCTL_DID0_CLASS_SHIFT (16) |

| Device Class Shift. More... | |

| #define | SYSCTL_DID0_CLASS_MASK (0xFF) |

| Device Class Mask. More... | |

| #define | SYSCTL_DID0_MAJOR_SHIFT (8) |

| Major Revision Shift. More... | |

| #define | SYSCTL_DID0_MAJOR_MASK (0xFF) |

| Major Revision Mask. More... | |

| #define | SYSCTL_DID0_MINOR_SHIFT (0) |

| Minor Revision Shift. More... | |

| #define | SYSCTL_DID0_MINOR_MASK (0xFF) |

| Minor Revision Mask. More... | |

| #define | SYSCTL_DID1_VER_SHIFT (28) |

| DID1 Version Shift. More... | |

| #define | SYSCTL_DID1_VER_MASK (0xF) |

| DID1 Version Mask. More... | |

| #define | SYSCTL_DID1_FAM_SHIFT (24) |

| Family Shift. More... | |

| #define | SYSCTL_DID1_FAM_MASK (0xF) |

| Family Mask. More... | |

| #define | SYSCTL_DID1_PARTNO_SHIFT (16) |

| Part Number Shift. More... | |

| #define | SYSCTL_DID1_PARTNO_MASK (0xFF) |

| Part Number Mask. More... | |

| #define | SYSCTL_DID1_PINCOUNT_SHIFT (13) |

| Package Pin Count Shift. More... | |

| #define | SYSCTL_DID1_PINCOUNT_MASK (0x7) |

| Package Pin Count Mask. More... | |

| #define | SYSCTL_DID1_PINCOUNT_128P (0x6) |

| 128-pin package More... | |

| #define | SYSCTL_DID1_PINCOUNT_212P (0x7) |

| 212-pin package More... | |

| #define | SYSCTL_DID1_TEMP_SHIFT (5) |

| Temperature Range Shift. More... | |

| #define | SYSCTL_DID1_TEMP_MASK (0x7) |

| Temperature Range Mask. More... | |

| #define | SYSCTL_DID1_TEMP_COMMERCIAL (0x0) |

| 0°C to +70°C More... | |

| #define | SYSCTL_DID1_TEMP_INDUSTRIAL (0x1) |

| -40°C to +85°C More... | |

| #define | SYSCTL_DID1_TEMP_EXTENDED (0x2) |

| -40°C to +105°C More... | |

| #define | SYSCTL_DID1_PKG_SHIFT (3) |

| Package Type Shift. More... | |

| #define | SYSCTL_DID1_PKG_MASK (0x3) |

| Package Type Mask. More... | |

| #define | SYSCTL_DID1_PKG_QFP (0x1) |

| QFP package. More... | |

| #define | SYSCTL_DID1_PKG_BGA (0x2) |

| BGA package. More... | |

| #define | SYSCTL_DID1_ROHS (1 << 2) |

| RoHS-compliance. More... | |

| #define | SYSCTL_DID1_QUAL_SHIFT (0) |

| Qualification Status Shift. More... | |

| #define | SYSCTL_DID1_QUAL_MASK (0x3) |

| Qualification Status Mask. More... | |

| #define | SYSCTL_DID1_QUAL_SAMPLE (0x0) |

| Engineering Sample. More... | |

| #define | SYSCTL_DID1_QUAL_PILOT (0x1) |

| Pilot Production. More... | |

| #define | SYSCTL_DID1_QUAL_QUALIFIED (0x2) |

| Fully Qualified. More... | |

| #define | SYSCTL_PTBOCTL_VDDA_UBOR_SHIFT (8) |

| VDDA Under BOR Event Action Shift. More... | |

| #define | SYSCTL_PTBOCTL_VDDA_UBOR_MASK (0x3) |

| VDDA Under BOR Event Action Mask. More... | |

| #define | SYSCTL_PTBOCTL_VDDA_UBOR_NO (0x0) |

| VDDA Under BOR Event Action - No action. More... | |

| #define | SYSCTL_PTBOCTL_VDDA_UBOR_INT (0x1) |

| VDDA Under BOR Event Action - System Control Interrupt. More... | |

| #define | SYSCTL_PTBOCTL_VDDA_UBOR_NMI (0x2) |

| VDDA Under BOR Event Action - Non-maskable interrupt. More... | |

| #define | SYSCTL_PTBOCTL_VDDA_UBOR_RESET (0x3) |

| VDDA Under BOR Event Action - Reset. More... | |

| #define | SYSCTL_PTBOCTL_VDD_UBOR_SHIFT (1) |

| VDD Under BOR Event Action Shift. More... | |

| #define | SYSCTL_PTBOCTL_VDD_UBOR_MASK (0x3) |

| VDD Under BOR Event Action Mask. More... | |

| #define | SYSCTL_PTBOCTL_VDD_UBOR_NO (0x0) |

| VDD Under BOR Event Action - No action. More... | |

| #define | SYSCTL_PTBOCTL_VDD_UBOR_INT (0x1) |

| VDD Under BOR Event Action - System Control Interrupt. More... | |

| #define | SYSCTL_PTBOCTL_VDD_UBOR_NMI (0x2) |

| VDD Under BOR Event Action - Non-maskable interrupt. More... | |

| #define | SYSCTL_PTBOCTL_VDD_UBOR_RESET (0x3) |

| VDD Under BOR Event Action - Reset. More... | |

| #define | SYSCTL_RIS_MOSCPUPRIS (1 << 8) |

| MOSC Power Up Raw Interrupt Status. More... | |

| #define | SYSCTL_RIS_PLLLRIS (1 << 6) |

| PLL Lock Raw Interrupt Status. More... | |

| #define | SYSCTL_RIS_MOFRIS (1 << 3) |

| Main Oscillator Failure Raw Interrupt Status. More... | |

| #define | SYSCTL_RIS_BORRIS (1 << 1) |

| Brown-Out Reset Raw Interrupt Status. More... | |

| #define | SYSCTL_IMC_MOSCPUPIM (1 << 8) |

| MOSC Power Up Raw Interrupt Mask. More... | |

| #define | SYSCTL_IMC_PLLLIM (1 << 6) |

| PLL Lock Raw Interrupt Mask. More... | |

| #define | SYSCTL_IMC_MOFIM (1 << 3) |

| Main Oscillator Failure Raw Interrupt Mask. More... | |

| #define | SYSCTL_IMC_BORIM (1 << 1) |

| Brown-Out Reset Raw Interrupt Mask. More... | |

| #define | SYSCTL_MISC_MOSCPUPMIS (1 << 8) |

| MOSC Power Up Raw Interrupt Status. More... | |

| #define | SYSCTL_MISC_PLLLMIS (1 << 6) |

| PLL Lock Raw Interrupt Status. More... | |

| #define | SYSCTL_MISC_MOFMIS (1 << 3) |

| Main Oscillator Failure Raw Interrupt Status. More... | |

| #define | SYSCTL_MISC_BORMIS (1 << 1) |

| Brown-Out Reset Raw Interrupt Status. More... | |

| #define | SYSCTL_RESC_MOSCFAIL (1 << 16) |

| MOSC Failure Reset. More... | |

| #define | SYSCTL_RESC_HSSR (1 << 12) |

| HSSR Reset. More... | |

| #define | SYSCTL_RESC_WDT1 (1 << 5) |

| Watchdog Timer 1 Reset. More... | |

| #define | SYSCTL_RESC_SW (1 << 4) |

| Software Reset. More... | |

| #define | SYSCTL_RESC_WDT0 (1 << 3) |

| Watchdog Timer 0 Reset. More... | |

| #define | SYSCTL_RESC_BOR (1 << 2) |

| Brown-Out Reset. More... | |

| #define | SYSCTL_RESC_POR (1 << 1) |

| Power-On Reset. More... | |

| #define | SYSCTL_RESC_EXT (1 << 0) |

| External Reset. More... | |

| #define | SYSCTL_PWRTC_VDDA_UBOR (1 << 4) |

| VDDA Under BOR Status. More... | |

| #define | SYSCTL_PWRTC_VDD_UBOR (1 << 0) |

| VDD Under BOR Status. More... | |

| #define | SYSCTL_NMIC_MOSCFAIL (1 << 16) |

| MOSC Failure NMI. More... | |

| #define | SYSCTL_NMIC_TAMPER (1 << 9) |

| Tamper Event NMI. More... | |

| #define | SYSCTL_NMIC_WDT1 (1 << 5) |

| WDT1 NMI. More... | |

| #define | SYSCTL_NMIC_WDT0 (1 << 3) |

| WDT0 NMI. More... | |

| #define | SYSCTL_NMIC_POWER (1 << 2) |

| Power/Brownout Event NMI. More... | |

| #define | SYSCTL_NMIC_EXTERNAL (1 << 0) |

| External Pin NMI. More... | |

| #define | SYSCTL_MOSCCTL_OSCRNG (1 << 4) |

| Oscillator Range. More... | |

| #define | SYSCTL_MOSCCTL_PWRDN (1 << 3) |

| Power Down. More... | |

| #define | SYSCTL_MOSCCTL_NOXTAL (1 << 2) |

| No MOSC or Crystal Connected. More... | |

| #define | SYSCTL_MOSCCTL_MOSCIM (1 << 1) |

| MOSC Failure Action. More... | |

| #define | SYSCTL_MOSCCTL_CVAL (1 << 0) |

| Clock Validation for MOSC. More... | |

| #define | SYSCTL_RSCLKCFG_MEMTIMU (1 << 31) |

| Memory Timing Register Update. More... | |

| #define | SYSCTL_RSCLKCFG_NEWFREQ (1 << 30) |

| New PLLFREQ Accept. More... | |

| #define | SYSCTL_RSCLKCFG_ACG (1 << 29) |

| Auto Clock Gating. More... | |

| #define | SYSCTL_RSCLKCFG_USEPLL (1 << 28) |

| Use PLL. More... | |

| #define | SYSCTL_RSCLKCFG_PLLSRC_SHIFT (24) |

| PLL Source Shift. More... | |

| #define | SYSCTL_RSCLKCFG_PLLSRC_MASK (0xF) |

| PLL Source Mask. More... | |

| #define | SYSCTL_RSCLKCFG_PLLSRC_MOSC (0x3) |

| PLL Source - MOSC. More... | |

| #define | SYSCTL_RSCLKCFG_OSCSRC_SHIFT (20) |

| Oscillator Source Shift. More... | |

| #define | SYSCTL_RSCLKCFG_OSCSRC_MASK (0xF) |

| Oscillator Source Mask. More... | |

| #define | SYSCTL_RSCLKCFG_OSCSRC_LFIOSC (0x2) |

| Oscillator Source - LFIOSC. More... | |

| #define | SYSCTL_RSCLKCFG_OSCSRC_MOSC (0x3) |

| Oscillator Source - MOSC. More... | |

| #define | SYSCTL_RSCLKCFG_OSCSRC_RTCOSC (0x4) |

| Oscillator Source - RTCOSC. More... | |

| #define | SYSCTL_RSCLKCFG_OSYSDIV_SHIFT (10) |

| Oscillator System Clock Divisor Shift. More... | |

| #define | SYSCTL_RSCLKCFG_OSYSDIV_MASK (0x3FF) |

| Oscillator System Clock Divisor Mask. More... | |

| #define | SYSCTL_RSCLKCFG_PSYSDIV_SHIFT (0) |

| PLL System Clock Divisor Shift. More... | |

| #define | SYSCTL_RSCLKCFG_PSYSDIV_MASK (0x3FF) |

| PLL System Clock Divisor Mask. More... | |

| #define | SYSCTL_MEMTIM0_EBCHT_SHIFT (22) |

| EEPROM Clock High Time Shift. More... | |

| #define | SYSCTL_MEMTIM0_EBCHT_MASK (0xF) |

| EEPROM Clock High Time Mask. More... | |

| #define | SYSCTL_MEMTIM0_EBCHT_0_POINT_5 (0x0) |

| EBCHT - 0.5 sys clock period. More... | |

| #define | SYSCTL_MEMTIM0_EBCHT_1 (0x1) |

| EBCHT - 1 sys clock period. More... | |

| #define | SYSCTL_MEMTIM0_EBCHT_1_POINT_5 (0x2) |

| EBCHT - 1.5 sys clock period. More... | |

| #define | SYSCTL_MEMTIM0_EBCHT_2 (0x3) |

| EBCHT - 2 sys clock period. More... | |

| #define | SYSCTL_MEMTIM0_EBCHT_2_POINT_5 (0x4) |

| EBCHT - 2.5 sys clock period. More... | |

| #define | SYSCTL_MEMTIM0_EBCHT_3 (0x5) |

| EBCHT - 3 sys clock period. More... | |

| #define | SYSCTL_MEMTIM0_EBCHT_3_POINT_5 (0x6) |

| EBCHT - 3.5 sys clock period. More... | |

| #define | SYSCTL_MEMTIM0_EBCHT_4 (0x7) |

| EBCHT - 4 sys clock period. More... | |

| #define | SYSCTL_MEMTIM0_EBCHT_4_POINT_5 (0x8) |

| EBCHT - 4.5 sys clock period. More... | |

| #define | SYSCTL_MEMTIM0_EBCE (1 << 21) |

| EEPROM Bank Clock Edge. More... | |

| #define | SYSCTL_MEMTIM0_EWS_SHIFT (16) |

| EEPROM Wait States Shift. More... | |

| #define | SYSCTL_MEMTIM0_EWS_MASK (0xF) |

| EEPROM Wait States Mask. More... | |

| #define | SYSCTL_MEMTIM0_EWS_1 (0x1) |

| EWS - 1 wait state. More... | |

| #define | SYSCTL_MEMTIM0_EWS_2 (0x2) |

| EWS - 2 wait state. More... | |

| #define | SYSCTL_MEMTIM0_EWS_3 (0x3) |

| EWS - 3 wait state. More... | |

| #define | SYSCTL_MEMTIM0_EWS_4 (0x4) |

| EWS - 4 wait state. More... | |

| #define | SYSCTL_MEMTIM0_EWS_5 (0x5) |

| EWS - 5 wait state. More... | |

| #define | SYSCTL_MEMTIM0_EWS_6 (0x6) |

| EWS - 6 wait state. More... | |

| #define | SYSCTL_MEMTIM0_EWS_7 (0x7) |

| EWS - 7 wait state. More... | |

| #define | SYSCTL_MEMTIM0_FBCHT_SHIFT (6) |

| Flash Clock High Time Shift. More... | |

| #define | SYSCTL_MEMTIM0_FBCHT_MASK (0xF) |

| Flash Clock High Time Mask. More... | |

| #define | SYSCTL_MEMTIM0_FBCHT_0_POINT_5 (0x0) |

| FBCHT - 0.5 sys clock period. More... | |

| #define | SYSCTL_MEMTIM0_FBCHT_1 (0x1) |

| FBCHT - 1 sys clock period. More... | |

| #define | SYSCTL_MEMTIM0_FBCHT_1_POINT_5 (0x2) |

| FBCHT - 1.5 sys clock period. More... | |

| #define | SYSCTL_MEMTIM0_FBCHT_2 (0x3) |

| FBCHT - 2 sys clock period. More... | |

| #define | SYSCTL_MEMTIM0_FBCHT_2_POINT_5 (0x4) |

| FBCHT - 2.5 sys clock period. More... | |

| #define | SYSCTL_MEMTIM0_FBCHT_3 (0x5) |

| FBCHT - 3 sys clock period. More... | |

| #define | SYSCTL_MEMTIM0_FBCHT_3_POINT_5 (0x6) |

| FBCHT - 3.5 sys clock period. More... | |

| #define | SYSCTL_MEMTIM0_FBCHT_4 (0x7) |

| FBCHT - 4 sys clock period. More... | |

| #define | SYSCTL_MEMTIM0_FBCHT_4_POINT_5 (0x8) |

| FBCHT - 4.5 sys clock period. More... | |

| #define | SYSCTL_MEMTIM0_FBCE (1 << 5) |

| Flash Bank Clock Edge. More... | |

| #define | SYSCTL_MEMTIM0_FWS_SHIFT (0) |

| Flash Wait States Shift. More... | |

| #define | SYSCTL_MEMTIM0_FWS_MASK (0xF) |

| Flash Wait States Mask. More... | |

| #define | SYSCTL_MEMTIM0_FWS_1 (0x1) |

| FWS - 1 wait state. More... | |

| #define | SYSCTL_MEMTIM0_FWS_2 (0x2) |

| FWS - 2 wait state. More... | |

| #define | SYSCTL_MEMTIM0_FWS_3 (0x3) |

| FWS - 3 wait state. More... | |

| #define | SYSCTL_MEMTIM0_FWS_4 (0x4) |

| FWS - 4 wait state. More... | |

| #define | SYSCTL_MEMTIM0_FWS_5 (0x5) |

| FWS - 5 wait state. More... | |

| #define | SYSCTL_MEMTIM0_FWS_6 (0x6) |

| FWS - 6 wait state. More... | |

| #define | SYSCTL_MEMTIM0_FWS_7 (0x7) |

| FWS - 7 wait state. More... | |

| #define | SYSCTL_ALTCLKCFG_ALTCLK_SHIFT (0) |

| Alternate Clock Source Shift. More... | |

| #define | SYSCTL_ALTCLKCFG_ALTCLK_MASK (0xF) |

| Alternate Clock Source Mask. More... | |

| #define | SYSCTL_ALTCLKCFG_ALTCLK_RTCOSC (0x3) |

| Alternate Clock Source - RTCOSC. More... | |

| #define | SYSCTL_ALTCLKCFG_ALTCLK_LFIOSC (0x4) |

| Alternate Clock Source - LFIOSC. More... | |

| #define | SYSCTL_DSCLKCFG_PIOSCPD (1 << 31) |

| PIOSC Power Down. More... | |

| #define | SYSCTL_DSCLKCFG_MOSCDPD (1 << 30) |

| MOSC Disable Power Down. More... | |

| #define | SYSCTL_DSCLKCFG_DSOSCSRC_SHIFT (20) |

| Deep Sleep Oscillator Source Shift. More... | |

| #define | SYSCTL_DSCLKCFG_DSOSCSRC_MASK (0xF) |

| Deep Sleep Oscillator Source Mask. More... | |

| #define | SYSCTL_DSCLKCFG_DSOSCSRC_LFIOSC (0x2) |

| Deep Sleep Oscillator Source - LFIOSC. More... | |

| #define | SYSCTL_DSCLKCFG_DSOSCSRC_MOSC (0x3) |

| Deep Sleep Oscillator Source - MOSC. More... | |

| #define | SYSCTL_DSCLKCFG_DSOSCSRC_RTCOSC (0x4) |

| Deep Sleep Oscillator Source - RTCOSC. More... | |

| #define | SYSCTL_DSCLKCFG_DSSYSDIV_SHIFT (0) |

| Deep Sleep Clock Divisor Shift. More... | |

| #define | SYSCTL_DSCLKCFG_DSSYSDIV_MASK (0x3FF) |

| Deep Sleep Clock Divisor Mask. More... | |

| #define | SYSCTL_DIVSCLK_EN (1 << 31) |

| DIVSCLK Enable. More... | |

| #define | SYSCTL_DIVSCLK_SRC_SHIFT (16) |

| Clock Source Shift. More... | |

| #define | SYSCTL_DIVSCLK_SRC_MASK (0x3) |

| Clock Source Mask. More... | |

| #define | SYSCTL_DIVSCLK_SRC_PIOSC (0x1) |

| Clock Source - PIOSCK. More... | |

| #define | SYSCTL_DIVSCLK_SRC_MOSC (0x2) |

| Clock Source - MOSC. More... | |

| #define | SYSCTL_DIVSCLK_DIV_SHIFT (0) |

| Divisor Value Shift. More... | |

| #define | SYSCTL_DIVSCLK_DIV_MASK (0xF) |

| Divisor Value Mask. More... | |

| #define | SYSCTL_DIVSCLK_DIV_1 (0x0) |

| Divisor Value - 1. More... | |

| #define | SYSCTL_DIVSCLK_DIV_2 (0x1) |

| Divisor Value - 2. More... | |

| #define | SYSCTL_SYSPROP_LDOSME (1 << 17) |

| LDO Sleep Mode Enable. More... | |

| #define | SYSCTL_SYSPROP_TSPDE (1 << 16) |

| Temp Sense Power Down Enable. More... | |

| #define | SYSCTL_SYSPROP_PIOSCPDE (1 << 12) |

| PIOSC Power Down Present. More... | |

| #define | SYSCTL_SYSPROP_SRAMSM (1 << 11) |

| SRAM Sleep/Deep-Sleep Standby Mode Present. More... | |

| #define | SYSCTL_SYSPROP_SRAMLPM (1 << 10) |

| SRAM Sleep/Deep-Sleep Low Power Mode Present. More... | |

| #define | SYSCTL_SYSPROP_FLASHLPM (1 << 8) |

| Flash Memory Sleep/Deep-Sleep Low Power Mode Present. More... | |

| #define | SYSCTL_SYSPROP_LDOSEQ (1 << 5) |

| Automatic LDO Sequence Control Present. More... | |

| #define | SYSCTL_SYSPROP_FPU (1 << 0) |

| FPU Present. More... | |

| #define | SYSCTL_PIOSCCAL_UTEN (1 << 31) |

| Use User Trim Value. More... | |

| #define | SYSCTL_PIOSCCAL_CAL (1 << 9) |

| Start Calibration. More... | |

| #define | SYSCTL_PIOSCCAL_UPDATE (1 << 8) |

| Update Trim. More... | |

| #define | SYSCTL_PIOSCCAL_UT_SHIFT (0) |

| User Trim Value Shift. More... | |

| #define | SYSCTL_PIOSCCAL_UT_MASK (0x7F) |

| User Trim Value Mask. More... | |

| #define | SYSCTL_PIOSCSTAT_DT_SHIFT (16) |

| Default Trim Value Shift. More... | |

| #define | SYSCTL_PIOSCSTAT_DT_MASK (0x7F) |

| Default Trim Value Mask. More... | |

| #define | SYSCTL_PIOSCSTAT_RESULT_SHIFT (8) |

| Calibration Result Shift. More... | |

| #define | SYSCTL_PIOSCSTAT_RESULT_MASK (0x3) |

| Calibration Result Mask. More... | |

| #define | SYSCTL_PIOSCSTAT_RESULT_NOT_ATTEMPT (0x0) |

| Calibration Not Attempted. More... | |

| #define | SYSCTL_PIOSCSTAT_RESULT_COMPLETE (0x1) |

| Calibration Completed. More... | |

| #define | SYSCTL_PIOSCSTAT_RESULT_FAIL (0x2) |

| Calibration Failed. More... | |

| #define | SYSCTL_PIOSCSTAT_CT_SHIFT (0) |

| Calibration Value Shift. More... | |

| #define | SYSCTL_PIOSCSTAT_CT_MASK (0x7F) |

| Calibration Value Mask. More... | |

| #define | SYSCTL_PLLFREQ0_PLLPWR (1 << 23) |

| PLL Power. More... | |

| #define | SYSCTL_PLLFREQ0_MFRAC_SHIFT (10) |

| PLL M Fractional Value Shift. More... | |

| #define | SYSCTL_PLLFREQ0_MFRAC_MASK (0x3FF) |

| PLL M Fractional Value Mask. More... | |

| #define | SYSCTL_PLLFREQ0_MINT_SHIFT (0) |

| PLL M Integer Value Shift. More... | |

| #define | SYSCTL_PLLFREQ0_MINT_MASK (0x3FF) |

| PLL M Integer Value Mask. More... | |

| #define | SYSCTL_PLLFREQ1_Q_SHIFT (8) |

| PLL Q Value Shift. More... | |

| #define | SYSCTL_PLLFREQ1_Q_MASK (0x1F) |

| PLL Q Value Mask. More... | |

| #define | SYSCTL_PLLFREQ1_N_SHIFT (0) |

| PLL N Value Shift. More... | |

| #define | SYSCTL_PLLFREQ1_N_MASK (0x1F) |

| PLL N Value Mask. More... | |

| #define | SYSCTL_PLLSTAT_LOCK (1 << 0) |

| PLL Lock. More... | |

| #define | SYSCTL_SLPPWRCFG_FLASHPM_SHIFT (4) |

| Flash Power Modes Shift. More... | |

| #define | SYSCTL_SLPPWRCFG_FLASHPM_MASK (0x3) |

| Flash Power Modes Mask. More... | |

| #define | SYSCTL_SLPPWRCFG_FLASHPM_ACTIVE (0x0) |

| Flash Power Mode - Active mode. More... | |

| #define | SYSCTL_SLPPWRCFG_FLASHPM_LP (0x2) |

| Flash Power Mode - Low-Power Mode. More... | |

| #define | SYSCTL_SLPPWRCFG_SRAMPM_SHIFT (0) |

| SRAM Power Modes Shift. More... | |

| #define | SYSCTL_SLPPWRCFG_SRAMPM_MASK (0x3) |

| SRAM Power Modes Mask. More... | |

| #define | SYSCTL_SLPPWRCFG_SRAMPM_ACTIVE (0x0) |

| SRAM Power Mode - Active mode. More... | |

| #define | SYSCTL_SLPPWRCFG_SRAMPM_STANDBY (0x1) |

| SRAM Power Mode - Standby mode. More... | |

| #define | SYSCTL_SLPPWRCFG_SRAMPM_LP (0x3) |

| SRAM Power Mode - Low-Power Mode. More... | |

| #define | SYSCTL_DSLPPWRCFG_LDOSM (1 << 9) |

| LDO Sleep Mode. More... | |

| #define | SYSCTL_DSLPPWRCFG_TSPD (1 << 8) |

| Temp Sense Power Down. More... | |

| #define | SYSCTL_DSLPPWRCFG_FLASHPM_SHIFT (4) |

| Flash Power Modes Shift. More... | |

| #define | SYSCTL_DSLPPWRCFG_FLASHPM_MASK (0x3) |

| Flash Power Modes Mask. More... | |

| #define | SYSCTL_DSLPPWRCFG_FLASHPM_ACTIVE (0x0) |

| Flash Power Mode - Active mode. More... | |

| #define | SYSCTL_DSLPPWRCFG_FLASHPM_LP (0x2) |

| Flash Power Mode - Low-Power Mode. More... | |

| #define | SYSCTL_DSLPPWRCFG_SRAMPM_SHIFT (0) |

| SRAM Power Modes Shift. More... | |

| #define | SYSCTL_DSLPPWRCFG_SRAMPM_MASK (0x3) |

| SRAM Power Modes Mask. More... | |

| #define | SYSCTL_DSLPPWRCFG_SRAMPM_ACTIVE (0x0) |

| SRAM Power Mode - Active mode. More... | |

| #define | SYSCTL_DSLPPWRCFG_SRAMPM_STANDBY (0x1) |

| SRAM Power Mode - Standby mode. More... | |

| #define | SYSCTL_DSLPPWRCFG_SRAMPM_LP (0x3) |

| SRAM Power Mode - Low-Power Mode. More... | |

| #define | SYSCTL_NVMSTAT_FWB (1 << 0) |

| 32 Word Flash Write Buffer Available More... | |

| #define | SYSCTL_LDOSPCTL_VADJEN (1 << 31) |

| Voltage Adjust Enable. More... | |

| #define | SYSCTL_LDOSPCTL_VLDO_SHIFT (0) |

| LDO Out Voltage Shift. More... | |

| #define | SYSCTL_LDOSPCTL_VLDO_MASK (0xFF) |

| LDO Out Voltage Mask. More... | |

| #define | SYSCTL_LDOSPCTL_VLDO_0_POINT_90 (0x12) |

| LDO Out Voltage - 0.90V. More... | |

| #define | SYSCTL_LDOSPCTL_VLDO_0_POINT_95 (0x13) |

| LDO Out Voltage - 0.95V. More... | |

| #define | SYSCTL_LDOSPCTL_VLDO_1_POINT_00 (0x14) |

| LDO Out Voltage - 1.00V. More... | |

| #define | SYSCTL_LDOSPCTL_VLDO_1_POINT_05 (0x15) |

| LDO Out Voltage - 1.05V. More... | |

| #define | SYSCTL_LDOSPCTL_VLDO_1_POINT_10 (0x16) |

| LDO Out Voltage - 1.10V. More... | |

| #define | SYSCTL_LDOSPCTL_VLDO_1_POINT_15 (0x17) |

| LDO Out Voltage - 1.15V. More... | |

| #define | SYSCTL_LDOSPCTL_VLDO_1_POINT_20 (0x18) |

| LDO Out Voltage - 1.20V. More... | |

| #define | SYSCTL_LDOSPCAL_WITHPLL_SHIFT (8) |

| Sleep With PLL Shift. More... | |

| #define | SYSCTL_LDOSPCAL_WITHPLL_MASK (0xFF) |

| Sleep With PLL Mask. More... | |

| #define | SYSCTL_LDOSPCAL_NOPLL_SHIFT (0) |

| Sleep Without PLL Shift. More... | |

| #define | SYSCTL_LDOSPCAL_NOPLL_MASK (0xFF) |

| Sleep Without PLL Mask. More... | |

| #define | SYSCTL_LDODPCTL_VADJEN (1 << 31) |

| Voltage Adjust Enable. More... | |

| #define | SYSCTL_LDODPCTL_VLDO_SHIFT (0) |

| LDO Out Voltage Shift. More... | |

| #define | SYSCTL_LDODPCTL_VLDO_MASK (0xFF) |

| LDO Out Voltage Mask. More... | |

| #define | SYSCTL_LDODPCTL_VLDO_0_POINT_90 (0x12) |

| LDO Out Voltage - 0.90V. More... | |

| #define | SYSCTL_LDODPCTL_VLDO_0_POINT_95 (0x13) |

| LDO Out Voltage - 0.95V. More... | |

| #define | SYSCTL_LDODPCTL_VLDO_1_POINT_00 (0x14) |

| LDO Out Voltage - 1.00V. More... | |

| #define | SYSCTL_LDODPCTL_VLDO_1_POINT_05 (0x15) |

| LDO Out Voltage - 1.05V. More... | |

| #define | SYSCTL_LDODPCTL_VLDO_1_POINT_10 (0x16) |

| LDO Out Voltage - 1.10V. More... | |

| #define | SYSCTL_LDODPCTL_VLDO_1_POINT_15 (0x17) |

| LDO Out Voltage - 1.15V. More... | |

| #define | SYSCTL_LDODPCTL_VLDO_1_POINT_20 (0x18) |

| LDO Out Voltage - 1.20V. More... | |

| #define | SYSCTL_LDODPCAL_NOPLL_SHIFT (8) |

| Deep-Sleep Without PLL Shift. More... | |

| #define | SYSCTL_LDODPCAL_NOPLL_MASK (0xFF) |

| Deep-Sleep Without PLL Mask. More... | |

| #define | SYSCTL_LDODPCAL_30KHZ_SHIFT (0) |

| Deep-Sleep With IOSC Shift. More... | |

| #define | SYSCTL_LDODPCAL_30KHZ_MASK (0xFF) |

| Deep-Sleep With IOSC Mask. More... | |

| #define | SYSCTL_SDPMST_LDOUA (1 << 19) |

| LDO Update Active. More... | |

| #define | SYSCTL_SDPMST_FLASHLP (1 << 18) |

| Flash Memory in Low Power State. More... | |

| #define | SYSCTL_SDPMST_LOWPWR (1 << 17) |

| Sleep or Deep-Sleep Mode. More... | |

| #define | SYSCTL_SDPMST_PRACT (1 << 16) |

| Sleep or Deep-Sleep Power Request Active. More... | |

| #define | SYSCTL_SDPMST_PPDW (1 << 7) |

| PIOSC Power Down Request Warning. More... | |

| #define | SYSCTL_SDPMST_LMAXERR (1 << 6) |

| VLDO Value Above Max Error. More... | |

| #define | SYSCTL_SDPMST_LSMINERR (1 << 4) |

| VLDO Value Below Minimum Error in Sleep Mode. More... | |

| #define | SYSCTL_SDPMST_LDMINERR (1 << 3) |

| VLDO Value Below Minimum Error in Deep-Sleep Mode. More... | |

| #define | SYSCTL_SDPMST_PPDERR (1 << 2) |

| PIOSC Power Down Request Error. More... | |

| #define | SYSCTL_SDPMST_FPDERR (1 << 1) |

| Flash Memory Power Down Request Error. More... | |

| #define | SYSCTL_SDPMST_SPDERR (1 << 0) |

| SRAM Power Down Request Error. More... | |

| #define | SYSCTL_RESBEHAVCTL_SYSRES (0x2) |

| Reset Operation - System Reset. More... | |

| #define | SYSCTL_RESBEHAVCTL_POR (0x3) |

| Reset Operation - Power-On-Reset. More... | |

| #define | SYSCTL_RESBEHAVCTL_WDOG1_SHIFT (6) |

| Watchdog 1 Reset Operation Shift. More... | |

| #define | SYSCTL_RESBEHAVCTL_WDOG1_MASK (0x3) |

| Watchdog 1 Reset Operation Mask. More... | |

| #define | SYSCTL_RESBEHAVCTL_WDOG0_SHIFT (4) |

| Watchdog 0 Reset Operation Shift. More... | |

| #define | SYSCTL_RESBEHAVCTL_WDOG0_MASK (0x3) |

| Watchdog 0 Reset Operation Mask. More... | |

| #define | SYSCTL_RESBEHAVCTL_BOR_SHIFT (2) |

| BOR Reset Operation Shift. More... | |

| #define | SYSCTL_RESBEHAVCTL_BOR_MASK (0x3) |

| BOR Reset Operation Shift. More... | |

| #define | SYSCTL_RESBEHAVCTL_EXTRES_SHIFT (2) |

| EXT Reset Operation Shift. More... | |

| #define | SYSCTL_RESBEHAVCTL_EXTRES_MASK (0x3) |

| EXT Reset Operation Mask. More... | |

| #define | SYSCTL_HSSR_KEY_SHIFT (24) |

| Write Key Shift. More... | |

| #define | SYSCTL_HSSR_KEY_MASK (0xFF) |

| Write Key Mask. More... | |

| #define | SYSCTL_HSSR_KEY_VALUE (0xCA) |

| Key Value for initiate request. More... | |

| #define | SYSCTL_HSSR_CDOFF_SHIFT (0) |

| Command Descriptor Pointer Shift. More... | |

| #define | SYSCTL_HSSR_CDOFF_MASK (0xFFFFFF) |

| Command Descriptor Pointer Mask. More... | |

| #define | SYSCTL_HSSR_CDOFF_NO_REQUEST (0x000000) |

| Command Descriptor - No Request. More... | |

| #define | SYSCTL_HSSR_CDOFF_ERROR (0xFFFFFF) |

| Command Descriptor - Error Or Incomplete Request. More... | |

| #define | SYSCTL_USBPDS_MEMSTAT_SHIFT (2) |

| Memory Array Power Status Shift. More... | |

| #define | SYSCTL_USBPDS_MEMSTAT_MASK (0x3) |

| Memory Array Power Status Mask. More... | |

| #define | SYSCTL_USBPDS_MEMSTAT_ARR_OFF (0x0) |

| Memory Array Power Status - Off. More... | |

| #define | SYSCTL_USBPDS_MEMSTAT_SRAM_RET (0x1) |

| Memory Array Power Status - SRAM Retention. More... | |

| #define | SYSCTL_USBPDS_MEMSTAT_ARR_ON (0x3) |

| Memory Array Power Status - On. More... | |

| #define | SYSCTL_USBPDS_PWRSTAT_SHIFT (0) |

| Power Domain Status Shift. More... | |

| #define | SYSCTL_USBPDS_PWRSTAT_MASK (0x3) |

| Power Domain Status Mask. More... | |

| #define | SYSCTL_USBPDS_PWRSTAT_OFF (0x0) |

| Power Domain Status - Off. More... | |

| #define | SYSCTL_USBPDS_PWRSTAT_ON (0x3) |

| Power Domain Status - On. More... | |

| #define | SYSCTL_USBMPC_PWRCTL_SHIFT (0) |

| Memory Array Power Control Shift. More... | |

| #define | SYSCTL_USBMPC_PWRCTL_MASK (0x3) |

| Memory Array Power Control Mask. More... | |

| #define | SYSCTL_USBMPC_PWRCTL_ARR_OFF (0x0) |

| Memory Array Power Control - Off. More... | |

| #define | SYSCTL_USBMPC_PWRCTL_SRAM_RET (0x1) |

| Memory Array Power Control - SRAM Retention. More... | |

| #define | SYSCTL_USBMPC_PWRCTL_ARR_ON (0x3) |

| Memory Array Power Control - On. More... | |

| #define | SYSCTL_EMACPDS_MEMSTAT_SHIFT (2) |

| Memory Array Power Status Shift. More... | |

| #define | SYSCTL_EMACPDS_MEMSTAT_MASK (0x3) |

| Memory Array Power Status Mask. More... | |

| #define | SYSCTL_EMACPDS_MEMSTAT_ARR_OFF (0x0) |

| Memory Array Power Status - Off. More... | |

| #define | SYSCTL_EMACPDS_MEMSTAT_ARR_ON (0x3) |

| Memory Array Power Status - On. More... | |

| #define | SYSCTL_EMACPDS_PWRSTAT_SHIFT (0) |

| Power Domain Status Shift. More... | |

| #define | SYSCTL_EMACPDS_PWRSTAT_MASK (0x3) |

| Power Domain Status Mask. More... | |

| #define | SYSCTL_EMACPDS_PWRSTAT_OFF (0x0) |

| Power Domain Status - Off. More... | |

| #define | SYSCTL_EMACPDS_PWRSTAT_ON (0x3) |

| Power Domain Status - On. More... | |

| #define | SYSCTL_EMACMPC_PWRCTL_SHIFT (0) |

| Memory Array Power Control Shift. More... | |

| #define | SYSCTL_EMACMPC_PWRCTL_MASK (0x3) |

| Memory Array Power Control Mask. More... | |

| #define | SYSCTL_EMACMPC_PWRCTL_ARR_OFF (0x0) |

| Memory Array Power Control - Off. More... | |

| #define | SYSCTL_EMACMPC_PWRCTL_ARR_ON (0x3) |

| Memory Array Power Control - On. More... | |

| #define | SYSCTL_LCDPDS_MEMSTAT_SHIFT (2) |

| Memory Array Power Status Shift. More... | |

| #define | SYSCTL_LCDPDS_MEMSTAT_MASK (0x3) |

| Memory Array Power Status Mask. More... | |

| #define | SYSCTL_LCDPDS_MEMSTAT_ARR_OFF (0x0) |

| Memory Array Power Status - Off. More... | |

| #define | SYSCTL_LCDPDS_MEMSTAT_ARR_ON (0x3) |

| Memory Array Power Status - On. More... | |

| #define | SYSCTL_LCDPDS_PWRSTAT_SHIFT (0) |

| Power Domain Status Shift. More... | |

| #define | SYSCTL_LCDPDS_PWRSTAT_MASK (0x3) |

| Power Domain Status Mask. More... | |

| #define | SYSCTL_LCDPDS_PWRSTAT_OFF (0x0) |

| Power Domain Status - Off. More... | |

| #define | SYSCTL_LCDPDS_PWRSTAT_ON (0x3) |

| Power Domain Status - On. More... | |

| #define | SYSCTL_LCDMPC_PWRCTL_SHIFT (0) |

| Memory Array Power Control Shift. More... | |

| #define | SYSCTL_LCDMPC_PWRCTL_MASK (0x3) |

| Memory Array Power Control Mask. More... | |

| #define | SYSCTL_LCDMPC_PWRCTL_ARR_OFF (0x0) |

| Memory Array Power Control - Off. More... | |

| #define | SYSCTL_LCDMPC_PWRCTL_ARR_ON (0x3) |

| Memory Array Power Control - On. More... | |

| #define | SYSCTL_CAN0PDS_MEMSTAT_SHIFT (2) |

| Memory Array Power Status Shift. More... | |

| #define | SYSCTL_CAN0PDS_MEMSTAT_MASK (0x3) |

| Memory Array Power Status Mask. More... | |

| #define | SYSCTL_CAN0PDS_MEMSTAT_ARR_OFF (0x0) |

| Memory Array Power Status - Off. More... | |

| #define | SYSCTL_CAN0PDS_MEMSTAT_ARR_ON (0x3) |

| Memory Array Power Status - On. More... | |

| #define | SYSCTL_CAN0PDS_PWRSTAT_SHIFT (0) |

| Power Domain Status Shift. More... | |

| #define | SYSCTL_CAN0PDS_PWRSTAT_MASK (0x3) |

| Power Domain Status Mask. More... | |

| #define | SYSCTL_CAN0PDS_PWRSTAT_OFF (0x0) |

| Power Domain Status - Off. More... | |

| #define | SYSCTL_CAN0PDS_PWRSTAT_ON (0x3) |

| Power Domain Status - On. More... | |

| #define | SYSCTL_CAN0MPC_PWRCTL_SHIFT (0) |

| Memory Array Power Control Shift. More... | |

| #define | SYSCTL_CAN0MPC_PWRCTL_MASK (0x3) |

| Memory Array Power Control Mask. More... | |

| #define | SYSCTL_CAN0MPC_PWRCTL_ARR_OFF (0x0) |

| Memory Array Power Control - Off. More... | |

| #define | SYSCTL_CAN0MPC_PWRCTL_ARR_ON (0x3) |

| Memory Array Power Control - On. More... | |

| #define | SYSCTL_CAN1PDS_MEMSTAT_SHIFT (2) |

| Memory Array Power Status Shift. More... | |

| #define | SYSCTL_CAN1PDS_MEMSTAT_MASK (0x3) |

| Memory Array Power Status Mask. More... | |

| #define | SYSCTL_CAN1PDS_MEMSTAT_ARR_OFF (0x0) |

| Memory Array Power Status - Off. More... | |

| #define | SYSCTL_CAN1PDS_MEMSTAT_ARR_ON (0x3) |

| Memory Array Power Status - On. More... | |

| #define | SYSCTL_CAN1PDS_PWRSTAT_SHIFT (0) |

| Power Domain Status Shift. More... | |

| #define | SYSCTL_CAN1PDS_PWRSTAT_MASK (0x3) |

| Power Domain Status Mask. More... | |

| #define | SYSCTL_CAN1PDS_PWRSTAT_OFF (0x0) |

| Power Domain Status - Off. More... | |

| #define | SYSCTL_CAN1PDS_PWRSTAT_ON (0x3) |

| Power Domain Status - On. More... | |

| #define | SYSCTL_CAN1MPC_PWRCTL_SHIFT (0) |

| Memory Array Power Control Shift. More... | |

| #define | SYSCTL_CAN1MPC_PWRCTL_MASK (0x3) |

| Memory Array Power Control Mask. More... | |

| #define | SYSCTL_CAN1MPC_PWRCTL_ARR_OFF (0x0) |

| Memory Array Power Control - Off. More... | |

| #define | SYSCTL_CAN1MPC_PWRCTL_ARR_ON (0x3) |

| Memory Array Power Control - On. More... | |

| #define | _REG_BIT(base, bit) (((base) << 5) + (bit)) |

Enumerations | |

| enum | msp432_clock_mode { CLOCK_RUN = 0x600 , CLOCK_SLEEP = 0x700 , CLOCK_DEEP_SLEEP = 0x800 } |

| Clock mode definitions The definitions are specified in the form offset from SYSCTL_BASE. More... | |

| enum | msp432_power_mode { POWER_DISABLE = false , POWER_ENABLE = true } |

| Power mode definitions. More... | |

| enum | msp432_periph { PERIPH_WD0 = _REG_BIT(0x00, 0) , PERIPH_WD1 , PERIPH_TIMER0 = _REG_BIT(0x04, 0) , PERIPH_TIMER1 , PERIPH_TIMER2 , PERIPH_TIMER3 , PERIPH_TIMER4 , PERIPH_TIMER5 , PERIPH_TIMER6 , PERIPH_TIMER7 , PERIPH_GPIOA = _REG_BIT(0x08, 0) , PERIPH_GPIOB , PERIPH_GPIOC , PERIPH_GPIOD , PERIPH_GPIOE , PERIPH_GPIOF , PERIPH_GPIOG , PERIPH_GPIOH , PERIPH_GPIOJ , PERIPH_GPIOK , PERIPH_GPIOL , PERIPH_GPIOM , PERIPH_GPION , PERIPH_GPIOP , PERIPH_GPIOQ , PERIPH_GPIOR , PERIPH_GPIOS , PERIPH_GPIOT , PERIPH_DMA = _REG_BIT(0x0C, 0) , PERIPH_EPI = _REG_BIT(0x10, 0) , PERIPH_HIB = _REG_BIT(0x14, 0) , PERIPH_UART0 = _REG_BIT(0x18, 0) , PERIPH_UART1 , PERIPH_UART2 , PERIPH_UART3 , PERIPH_UART4 , PERIPH_UART5 , PERIPH_UART6 , PERIPH_UART7 , PERIPH_SSI0 = _REG_BIT(0x1C, 0) , PERIPH_SSI1 , PERIPH_SSI2 , PERIPH_SSI3 , PERIPH_I2C0 = _REG_BIT(0x20, 0) , PERIPH_I2C1 , PERIPH_I2C2 , PERIPH_I2C3 , PERIPH_I2C4 , PERIPH_I2C5 , PERIPH_I2C6 , PERIPH_I2C7 , PERIPH_I2C8 , PERIPH_I2C9 , PERIPH_USB0 = _REG_BIT(0x28, 0) , PERIPH_EPHY = _REG_BIT(0x30, 0) , PERIPH_CAN0 = _REG_BIT(0x34, 0) , PERIPH_CAN1 , PERIPH_ADC0 = _REG_BIT(0x38, 0) , PERIPH_ADC1 , PERIPH_ACMP = _REG_BIT(0x3C, 0) , PERIPH_PWM = _REG_BIT(0x40, 0) , PERIPH_QEI = _REG_BIT(0x44, 0) , PERIPH_EEPROM = _REG_BIT(0x58, 0) , PERIPH_CCM = _REG_BIT(0x74, 0) , PERIPH_LCD = _REG_BIT(0x90, 0) , PERIPH_OWIRE = _REG_BIT(0x98, 0) , PERIPH_EMAC = _REG_BIT(0x9C, 0) , PERIPH_PRB = _REG_BIT(0xA0, 0) } |

| Peripheral list definitions The definitions are specified in the form 31:5 register offset from first register for SR, PP, RCGC, SCGC, DCGC, PC, PR 4:0 bit offset for the given peripheral. More... | |

Functions | |

| void | sysctl_periph_clock_enable (enum msp432_clock_mode clock_mode, enum msp432_periph periph) |

| System Control Enable Peripheral Clock. More... | |

| void | sysctl_periph_clock_disable (enum msp432_clock_mode clock_mode, enum msp432_periph periph) |

| System Control Disable Peripheral Clock. More... | |

| void | sysctl_periph_reset (enum msp432_periph periph) |

| System Control Peripheral Software Reset. More... | |

| void | sysctl_periph_clear_reset (enum msp432_periph periph) |

| System Control Peripheral Clear Software Reset. More... | |

| bool | sysctl_periph_is_present (enum msp432_periph periph) |

| System Control Peripheral Is Present. More... | |

| bool | sysctl_periph_is_ready (enum msp432_periph periph) |

| System Control Peripheral Is Ready. More... | |

| void | sysctl_periph_set_power_state (enum msp432_power_mode power_mode, enum msp432_periph periph) |

| System Control Peripheral Set Power State. More... | |