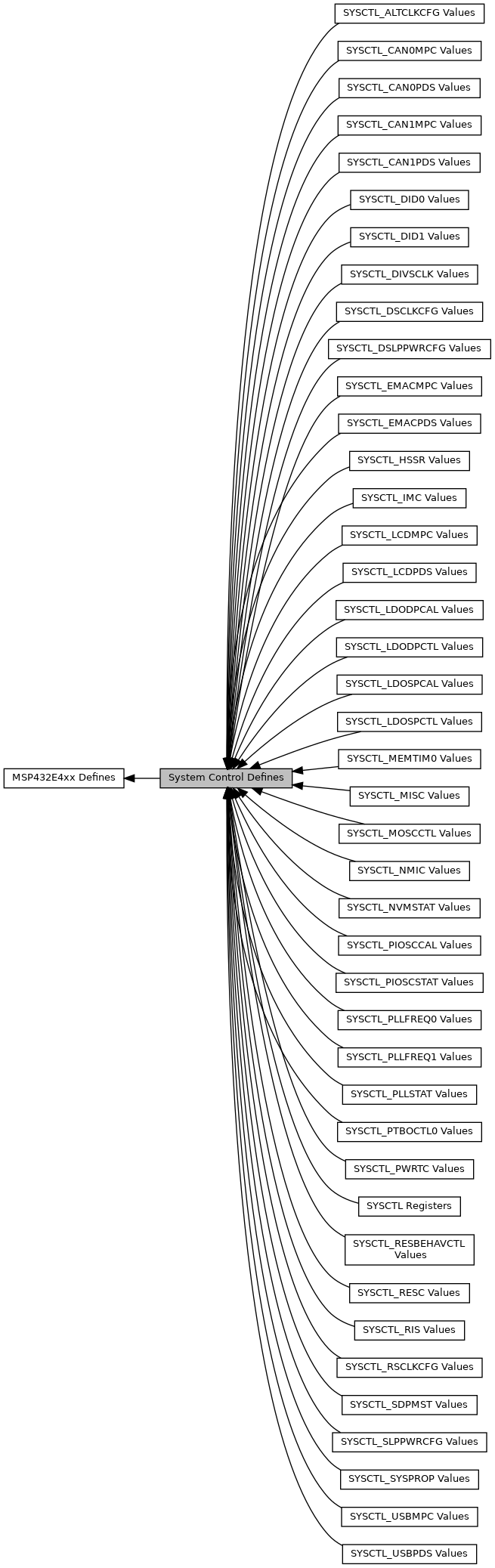

Defined Constants and Types for the MSP432E4xx System Control. More...

Modules | |

| SYSCTL Registers | |

| System Control Registers. | |

| SYSCTL_DID0 Values | |

| System Control Device Identification 0 Register Values. | |

| SYSCTL_DID1 Values | |

| System Control Device Identification 1 Register Values. | |

| SYSCTL_PTBOCTL0 Values | |

| System Control Power-Temp Brownout Control Register Values. | |

| SYSCTL_RIS Values | |

| System Control Raw Interrupt Status Register Values. | |

| SYSCTL_IMC Values | |

| System Control Interrupt Mask Control Register Values. | |

| SYSCTL_MISC Values | |

| System Control Masked Interrupt Status and Clear Register Values. | |

| SYSCTL_RESC Values | |

| System Control Reset Cause Register Values. | |

| SYSCTL_PWRTC Values | |

| System Control Power-Temperature Cause Register Values. | |

| SYSCTL_NMIC Values | |

| System Control NMI Cause Register Values. | |

| SYSCTL_MOSCCTL Values | |

| System Control Main Oscillator Control Register Values. | |

| SYSCTL_RSCLKCFG Values | |

| System Control Run and Sleep Mode Configuration Register Values. | |

| SYSCTL_MEMTIM0 Values | |

| System Control Memory Timing Parameter Register 0 for Main Flash and EEPROM Register Values. | |

| SYSCTL_ALTCLKCFG Values | |

| System Control Alternate Clock Configuration Register Values. | |

| SYSCTL_DSCLKCFG Values | |

| System Control Deep Sleep Clock Configuration Register Values. | |

| SYSCTL_DIVSCLK Values | |

| System Control Divisor and Source Clock Configuration Register Values. | |

| SYSCTL_SYSPROP Values | |

| System Control System Properties Register Values. | |

| SYSCTL_PIOSCCAL Values | |

| System Control Precision Internal Oscillator Calibration Register Values. | |

| SYSCTL_PIOSCSTAT Values | |

| System Control Precision Internal Oscillator Statistics Register Values. | |

| SYSCTL_PLLFREQ0 Values | |

| System Control PLL Frequency 0 Register Values. | |

| SYSCTL_PLLFREQ1 Values | |

| System Control PLL Frequency 1 Register Values. | |

| SYSCTL_PLLSTAT Values | |

| System Control PLL Status Register Values. | |

| SYSCTL_SLPPWRCFG Values | |

| System Control Sleep Power Configuration Register Values. | |

| SYSCTL_DSLPPWRCFG Values | |

| System Control Deep-Sleep Power Configuration Register Values. | |

| SYSCTL_NVMSTAT Values | |

| System Control Non-Volatile Memory Information Register Values. | |

| SYSCTL_LDOSPCTL Values | |

| System Control LDO Sleep Power Control Register Values. | |

| SYSCTL_LDOSPCAL Values | |

| System Control LDO Sleep Power Calibration Register Values. | |

| SYSCTL_LDODPCTL Values | |

| System Control LDO Deep-Sleep Power Control Register Values. | |

| SYSCTL_LDODPCAL Values | |

| System Control LDO Deep-Sleep Power Calibration Register Values. | |

| SYSCTL_SDPMST Values | |

| System Control Sleep/Deep-Sleep Power Mode Status Register Values. | |

| SYSCTL_RESBEHAVCTL Values | |

| System Control Reset Behavior Control Register Values. | |

| SYSCTL_HSSR Values | |

| System Control Hardware System Service Request Register Values. | |

| SYSCTL_USBPDS Values | |

| System Control USB Power Domain Status Register Values. | |

| SYSCTL_USBMPC Values | |

| System Control USB Memory Power Control Register Values. | |

| SYSCTL_EMACPDS Values | |

| System Control Ethernet MAC Power Domain Status Register Values. | |

| SYSCTL_EMACMPC Values | |

| System Control Ethernet MAC Memory Power Control Register Values. | |

| SYSCTL_LCDPDS Values | |

| System Control LCD Power Domain Status Register Values. | |

| SYSCTL_LCDMPC Values | |

| System Control LCD Memory Power Control Register Values. | |

| SYSCTL_CAN0PDS Values | |

| System Control CAN 0 Power Domain Status Register Values. | |

| SYSCTL_CAN0MPC Values | |

| System Control CAN 0 Memory Power Control Register Values. | |

| SYSCTL_CAN1PDS Values | |

| System Control CAN 1 Power Domain Status Register Values. | |

| SYSCTL_CAN1MPC Values | |

| System Control CAN 1 Memory Power Control Register Values. | |

Macros | |

| #define | _REG_BIT(base, bit) (((base) << 5) + (bit)) |

Enumerations | |

| enum | msp432_clock_mode { CLOCK_RUN = 0x600 , CLOCK_SLEEP = 0x700 , CLOCK_DEEP_SLEEP = 0x800 } |

| Clock mode definitions The definitions are specified in the form offset from SYSCTL_BASE. More... | |

| enum | msp432_power_mode { POWER_DISABLE = false , POWER_ENABLE = true } |

| Power mode definitions. More... | |

| enum | msp432_periph { PERIPH_WD0 = _REG_BIT(0x00, 0) , PERIPH_WD1 , PERIPH_TIMER0 = _REG_BIT(0x04, 0) , PERIPH_TIMER1 , PERIPH_TIMER2 , PERIPH_TIMER3 , PERIPH_TIMER4 , PERIPH_TIMER5 , PERIPH_TIMER6 , PERIPH_TIMER7 , PERIPH_GPIOA = _REG_BIT(0x08, 0) , PERIPH_GPIOB , PERIPH_GPIOC , PERIPH_GPIOD , PERIPH_GPIOE , PERIPH_GPIOF , PERIPH_GPIOG , PERIPH_GPIOH , PERIPH_GPIOJ , PERIPH_GPIOK , PERIPH_GPIOL , PERIPH_GPIOM , PERIPH_GPION , PERIPH_GPIOP , PERIPH_GPIOQ , PERIPH_GPIOR , PERIPH_GPIOS , PERIPH_GPIOT , PERIPH_DMA = _REG_BIT(0x0C, 0) , PERIPH_EPI = _REG_BIT(0x10, 0) , PERIPH_HIB = _REG_BIT(0x14, 0) , PERIPH_UART0 = _REG_BIT(0x18, 0) , PERIPH_UART1 , PERIPH_UART2 , PERIPH_UART3 , PERIPH_UART4 , PERIPH_UART5 , PERIPH_UART6 , PERIPH_UART7 , PERIPH_SSI0 = _REG_BIT(0x1C, 0) , PERIPH_SSI1 , PERIPH_SSI2 , PERIPH_SSI3 , PERIPH_I2C0 = _REG_BIT(0x20, 0) , PERIPH_I2C1 , PERIPH_I2C2 , PERIPH_I2C3 , PERIPH_I2C4 , PERIPH_I2C5 , PERIPH_I2C6 , PERIPH_I2C7 , PERIPH_I2C8 , PERIPH_I2C9 , PERIPH_USB0 = _REG_BIT(0x28, 0) , PERIPH_EPHY = _REG_BIT(0x30, 0) , PERIPH_CAN0 = _REG_BIT(0x34, 0) , PERIPH_CAN1 , PERIPH_ADC0 = _REG_BIT(0x38, 0) , PERIPH_ADC1 , PERIPH_ACMP = _REG_BIT(0x3C, 0) , PERIPH_PWM = _REG_BIT(0x40, 0) , PERIPH_QEI = _REG_BIT(0x44, 0) , PERIPH_EEPROM = _REG_BIT(0x58, 0) , PERIPH_CCM = _REG_BIT(0x74, 0) , PERIPH_LCD = _REG_BIT(0x90, 0) , PERIPH_OWIRE = _REG_BIT(0x98, 0) , PERIPH_EMAC = _REG_BIT(0x9C, 0) , PERIPH_PRB = _REG_BIT(0xA0, 0) } |

| Peripheral list definitions The definitions are specified in the form 31:5 register offset from first register for SR, PP, RCGC, SCGC, DCGC, PC, PR 4:0 bit offset for the given peripheral. More... | |

Functions | |

| void | sysctl_periph_clock_enable (enum msp432_clock_mode clock_mode, enum msp432_periph periph) |

| System Control Enable Peripheral Clock. More... | |

| void | sysctl_periph_clock_disable (enum msp432_clock_mode clock_mode, enum msp432_periph periph) |

| System Control Disable Peripheral Clock. More... | |

| void | sysctl_periph_reset (enum msp432_periph periph) |

| System Control Peripheral Software Reset. More... | |

| void | sysctl_periph_clear_reset (enum msp432_periph periph) |

| System Control Peripheral Clear Software Reset. More... | |

| bool | sysctl_periph_is_present (enum msp432_periph periph) |

| System Control Peripheral Is Present. More... | |

| bool | sysctl_periph_is_ready (enum msp432_periph periph) |

| System Control Peripheral Is Ready. More... | |

| void | sysctl_periph_set_power_state (enum msp432_power_mode power_mode, enum msp432_periph periph) |

| System Control Peripheral Set Power State. More... | |

Detailed Description

Defined Constants and Types for the MSP432E4xx System Control.

- Version

- 1.0.0

- Date

- 22 July 2018

LGPL License Terms libopencm3 License

Macro Definition Documentation

◆ _REG_BIT

| #define _REG_BIT | ( | base, | |

| bit | |||

| ) | (((base) << 5) + (bit)) |

Definition at line 1346 of file systemcontrol.h.

Enumeration Type Documentation

◆ msp432_clock_mode

| enum msp432_clock_mode |

Clock mode definitions The definitions are specified in the form offset from SYSCTL_BASE.

- CLOCK_RUN - Run mode

- CLOCK_SLEEP - Sleep mode

- CLOCK_DEEP_SLEEP - Deep-Sleep Mode

| Enumerator | |

|---|---|

| CLOCK_RUN | |

| CLOCK_SLEEP | |

| CLOCK_DEEP_SLEEP | |

Definition at line 1326 of file systemcontrol.h.

◆ msp432_periph

| enum msp432_periph |

Peripheral list definitions The definitions are specified in the form 31:5 register offset from first register for SR, PP, RCGC, SCGC, DCGC, PC, PR 4:0 bit offset for the given peripheral.

Definition at line 1355 of file systemcontrol.h.

◆ msp432_power_mode

| enum msp432_power_mode |

Power mode definitions.

- POWER_DISABLE - Module is not powered and does not receive a clock

- POWER_ENABLE - Module is powered but does not receive a clock

- Note

- If the module is in run, sleep or deep-sleep mode - the module is powered and receives a clock regardless of the value of power mode.

| Enumerator | |

|---|---|

| POWER_DISABLE | |

| POWER_ENABLE | |

Definition at line 1341 of file systemcontrol.h.

Function Documentation

◆ sysctl_periph_clear_reset()

| void sysctl_periph_clear_reset | ( | enum msp432_periph | periph | ) |

System Control Peripheral Clear Software Reset.

- Parameters

-

[in] periph msp432_periph Peripheral block

Definition at line 79 of file systemcontrol.c.

References _SYSCTL_REG, and SYSCTL_SRWD.

◆ sysctl_periph_clock_disable()

| void sysctl_periph_clock_disable | ( | enum msp432_clock_mode | clock_mode, |

| enum msp432_periph | periph | ||

| ) |

System Control Disable Peripheral Clock.

- Parameters

-

[in] clock_mode msp432_clock_mode Clock mode [in] periph msp432_periph Peripheral block

Definition at line 58 of file systemcontrol.c.

References _SYSCTL_REG, and SYSCTL_BASE.

◆ sysctl_periph_clock_enable()

| void sysctl_periph_clock_enable | ( | enum msp432_clock_mode | clock_mode, |

| enum msp432_periph | periph | ||

| ) |

System Control Enable Peripheral Clock.

- Parameters

-

[in] clock_mode msp432_clock_mode Clock mode [in] periph msp432_periph Peripheral block

Definition at line 46 of file systemcontrol.c.

References _SYSCTL_BIT, _SYSCTL_REG, and SYSCTL_BASE.

◆ sysctl_periph_is_present()

| bool sysctl_periph_is_present | ( | enum msp432_periph | periph | ) |

System Control Peripheral Is Present.

- Parameters

-

[in] periph msp432_periph Peripheral block

Definition at line 89 of file systemcontrol.c.

References _SYSCTL_BIT, _SYSCTL_REG, and SYSCTL_PPWD.

◆ sysctl_periph_is_ready()

| bool sysctl_periph_is_ready | ( | enum msp432_periph | periph | ) |

System Control Peripheral Is Ready.

- Parameters

-

[in] periph msp432_periph Peripheral block

Definition at line 102 of file systemcontrol.c.

References _SYSCTL_BIT, _SYSCTL_REG, and SYSCTL_PRWD.

◆ sysctl_periph_reset()

| void sysctl_periph_reset | ( | enum msp432_periph | periph | ) |

System Control Peripheral Software Reset.

- Parameters

-

[in] periph msp432_periph Peripheral block

Definition at line 69 of file systemcontrol.c.

References _SYSCTL_BIT, _SYSCTL_REG, and SYSCTL_SRWD.

◆ sysctl_periph_set_power_state()

| void sysctl_periph_set_power_state | ( | enum msp432_power_mode | power_mode, |

| enum msp432_periph | periph | ||

| ) |

System Control Peripheral Set Power State.

- Parameters

-

[in] power_mode msp432_power_mode Power mode [in] periph msp432_periph Peripheral block

- Note

- If the module is in run, sleep or deep-sleep mode - the module is powered and receives a clock regardless of the value of power mode.

Definition at line 119 of file systemcontrol.c.

References _SYSCTL_BIT, _SYSCTL_REG, POWER_ENABLE, and SYSCTL_PCWD.