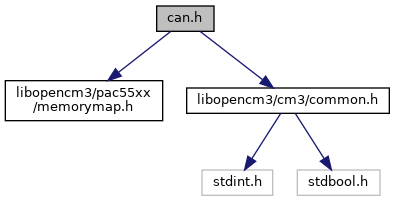

Include dependency graph for can.h:

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Macros | |

| #define | CAN_ISR_SR_CMR_MR(can_base) MMIO32((can_base) + 0x0000) |

| This is the 32-bit memory mapped read/write accessor for: More... | |

| #define | CAN_ISR_SR_CMR_MR_SET(can_base, bits) |

| #define | CAN_ISR_SR_CMR_MR_CLEAR(can_base, bits) |

| #define | CAN_BTR1_BTR0_RMC_IMR(can_base) MMIO32((can_base) + 0x0004) |

| This is the 32-bit memory mapped read/write accessor for: More... | |

| #define | CAN_TXBUF(can_base) MMIO32((can_base) + 0x0008) |

| CAN Transmit Buffer Register RW, default 00000000h. More... | |

| #define | CAN_RXBUF(can_base) MMIO32((can_base) + 0x000C) |

| CAN Receive Buffer Register RO, default 00000000h. More... | |

| #define | CAN_ACR(can_base) MMIO32((can_base) + 0x0010) |

| CAN Acceptance Code Register RW, default 00000000h. More... | |

| #define | CAN_AMR(can_base) MMIO32((can_base) + 0x0014) |

| CAN Acceptance Mask Register RW, default 00000000h. More... | |

| #define | CAN_ALC_TXERR_RXERR_ECC(can_base) MMIO32((can_base) + 0x0018) |

| #define | CAN_ECC(can_base) (CAN_ALC_TXERR_RXERR_ECC(can_base) & 0xFF) |

| CAN Error Code Capture Register RO, default 00h. More... | |

| #define | CAN_RXERR(can_base) ((CAN_ALC_TXERR_RXERR_ECC(can_base) >> 8) & 0xFF) |

| CAN RX Error Counter Register RO, default 00h. More... | |

| #define | CAN_TXERR(can_base) ((CAN_ALC_TXERR_RXERR_ECC(can_base) >> 16) & 0xFF) |

| CAN TX Error Counter Register RO, default 00h. More... | |

| #define | CAN_ALC(can_base) ((CAN_ALC_TXERR_RXERR_ECC(can_base) >> 24) & 0xFF) |

| CAN Arbitration Lost Code Capture Register RO, default 00h. More... | |

| #define | CAN_MR_AFM BIT0 |

| AFM: Acceptance Filter Mode. More... | |

| #define | CAN_MR_LOM BIT1 |

| LOM: Listen only mode. More... | |

| #define | CAN_MR_RM BIT2 |

| RM: Reset Mode. More... | |

| #define | CAN_CMR_AT BIT9 |

| AT: Abort transmission. More... | |

| #define | CAN_CMR_TR BIT10 |

| TR: Transmit Request. More... | |

| #define | CAN_SR_BS BIT16 |

| BS: Bus Off Status. More... | |

| #define | CAN_SR_ES BIT17 |

| ES: Error Status. More... | |

| #define | CAN_SR_TS BIT18 |

| TS: Transmit Status. More... | |

| #define | CAN_SR_RS BIT19 |

| RS: Receive Status. More... | |

| #define | CAN_SR_TBS BIT21 |

| TBS: Transmit Buffer Status. More... | |

| #define | CAN_SR_DSO BIT22 |

| DSO: Data Overrun Status. More... | |

| #define | CAN_SR_RBS BIT23 |

| RBS: Receive Buffer Status. More... | |

| #define | CAN_ISR_DOI BIT24 |

| DOI: Data Overflow Interrupt. More... | |

| #define | CAN_ISR_BEI BIT25 |

| BEI: Bus Error Interrupt. More... | |

| #define | CAN_ISR_TI BIT26 |

| TI: Transmit Interrupt. More... | |

| #define | CAN_ISR_RI BIT27 |

| RI: Receive Interrupt. More... | |

| #define | CAN_ISR_EPI BIT28 |

| EPI: Error Passive Interrupt. More... | |

| #define | CAN_ISR_EWI BIT29 |

| EWI: Error Warning Interrupt. More... | |

| #define | CAN_ISR_ALI BIT30 |

| ALI: Arbitration Lost Interrupt. More... | |

| #define | CAN_ISR_ACKNOWLEDGE(can_base, isr) CAN_ISR_SR_CMR_MR_SET(can_base, ((isr) & 0x7F000000)) |

| This is a helper to acknowledge an ISR. More... | |

| #define | CAN_IMR_DOIM BIT0 |

| DOIM: DOI Interrupt Mask. More... | |

| #define | CAN_IMR_BEIM BIT1 |

| BEIM: BEI Interrupt Mask. More... | |

| #define | CAN_IMR_TIM BIT2 |

| TIM: TI Interrupt Mask. More... | |

| #define | CAN_IMR_RIM BIT3 |

| RIM: RI Interrupt Mask. More... | |

| #define | CAN_IMR_EPIM BIT4 |

| EPIM: EPI Interrupt Mask. More... | |

| #define | CAN_IMR_EWIM BIT5 |

| EWIM: EWI Interrupt Mask. More... | |

| #define | CAN_IMR_ALIM BIT6 |

| ALIM: ALI Interrupt Mask. More... | |

| #define | CAN_RMC(can_base) ((CAN_BTR1_BTR0_RMC_IMR(can_base) >> 8) & 0x1F) |

| #define | CAN_BTR0_BRP_MASK (0x3F) |

| #define | CAN_BTR0_BRP_SHIFT 16 |

| #define | CAN_BTR0_BRP(val) (((val) & CAN_BTR0_BRP_MASK) << CAN_BTR0_BRP_SHIFT) |

| #define | CAN_BTR0_SJW_MASK (0x03) |

| #define | CAN_BTR0_SJW_SHIFT 22 |

| #define | CAN_BTR0_SJW(val) (((val) & CAN_BTR0_SJW_MASK) << CAN_BTR0_SJW_SHIFT) |

| #define | CAN_BTR1_TSEG1_MASK (0x0F) |

| #define | CAN_BTR1_TSEG1_SHIFT 24 |

| #define | CAN_BTR1_TSEG1(val) (((val) & CAN_BTR1_TSEG1_MASK) << CAN_BTR1_TSEG1_SHIFT) |

| #define | CAN_BTR1_TSEG2_MASK (0x07) |

| #define | CAN_BTR1_TSEG2_SHIFT 28 |

| #define | CAN_BTR1_TSEG2(val) (((val) & CAN_BTR1_TSEG2_MASK) << CAN_BTR1_TSEG2_SHIFT) |

| #define | CAN_BTR1_SAM BIT31 |

| #define | CAN_ECC_BER BIT0 |

| BER: Bit error ocurred. More... | |

| #define | CAN_ECC_STFER BIT1 |

| STFER: Stuff error occurred. More... | |

| #define | CAN_ECC_CRCER BIT2 |

| CRCER: CRC error occurred. More... | |

| #define | CAN_ECC_FRMER BIT3 |

| FRMER: Form error occurred. More... | |

| #define | CAN_ECC_ACKER BIT4 |

| ACKER: ACK error occurred. More... | |

| #define | CAN_ECC_EDIR BIT5 |

| EDIR: Direction of transfer 0:TX, 1:RX. More... | |

| #define | CAN_ECC_TXWRN BIT6 |

| TXWRN: set when CAN_TXERR >= 96. More... | |

| #define | CAN_ECC_RXWRN BIT7 |

| RXWRN: set when CAN_RXERR >= 96. More... | |

| #define | CAN_ACR_DUAL_DB_UPPER 0x000F0000U /* 19:16 */ |

| #define | CAN_ACR_DUAL_DB_LOWER 0x0000000FU /* 3:0 */ |

| #define | CAN_ACR_DUAL_ID1 0xFFE00000U /* 31:21 */ |

| #define | CAN_ACR_DUAL_ID2 0x0000FFE0U /* 15:5 */ |

| #define | CAN_ACR_DUAL_RTR1 0x00100000U /* 20 */ |

| #define | CAN_ACR_DUAL_RTR2 0x00000010U /* 4 */ |

| #define | CAN_ACR_SINGLE_STD_ID 0xFFE00000U /* 31:21 */ |

| #define | CAN_ACR_SINGLE_STD_RTR 0x00100000U /* 20 */ |

| #define | CAN_ACR_SINGLE_STD_DB1 0x0000FF00U /* 15:8 */ |

| #define | CAN_ACR_SINGLE_STD_DB2 0x000000FFU /* 7:0 */ |

| #define | CAN_ACR_SINGLE_EXT_ID 0xFFFFFFF8U /* 31:3 */ |

| #define | CAN_ACR_SINGLE_EXT_RTR 0x00000004U /* 2 */ |

| #define | CAN_BITS_2_0 (0x07) |

| #define | CAN_BITS_3_0 (0x0F) |

| #define | CAN_BITS_4_0 (0x1F) |

| #define | CAN_BITS_7_3 (0xF8) |

| #define | CAN_BITS_10_3 (0x07F8) |

| #define | CAN_BITS_12_5 (0x00001FE0U) |

| #define | CAN_BITS_20_13 (0x001FE000U) |

| #define | CAN_BITS_28_21 (0x1FE00000U) |

| #define | CAN_BITS_15_8 (0x0000FF00U) |

| #define | CAN_BITS_23_16 (0x00FF0000U) |

| #define | CAN_BITS_31_24 (0xFF000000U) |

| #define | CAN_BITS_23_21 (0x00E00000U) |

Functions | |

| void | can_enable (uint32_t canport) |

| CAN Enable Enable the CAN peripheral and its associated FIFOs/counters/interrupts. More... | |

| void | can_disable (uint32_t canport) |

| CAN Disable Disable the CAN peripheral and all associated FIFOs/counters/interrupts. More... | |

| void | can_init (uint32_t canport, bool listen_only, uint32_t sjw, uint32_t tseg1, uint32_t tseg2, bool sam3, uint32_t brp) |

| CAN Init Initialize the selected CAN peripheral block. More... | |

| void | can_filter_clear (uint32_t canport) |

| CAN Filter Clear Clear the message filters to receive all messages. More... | |

| void | can_filter_dual (uint32_t canport, uint32_t id1, uint32_t id1_mask, uint32_t id2, uint32_t id2_mask, uint8_t db, uint8_t db_mask) |

| CAN Dual Filter Standard Frame Notes: More... | |

| void | can_filter_single_std (uint32_t canport, uint32_t id, uint32_t id_mask, uint8_t db1, uint8_t db1_mask, uint8_t db2, uint8_t db2_mask) |

| CAN Filter Single Standard Frame Notes: More... | |

| void | can_filter_single_std_rtr (uint32_t canport, uint32_t id, uint32_t id_mask, uint8_t db1, uint8_t db1_mask, uint8_t db2, uint8_t db2_mask) |

| CAN Filter Single Standard Frame w/RTR set Notes: More... | |

| void | can_filter_single_ext (uint32_t canport, uint32_t id, uint32_t id_mask) |

| CAN Filter Single Extended Frame Notes: More... | |

| void | can_filter_single_ext_rtr (uint32_t canport, uint32_t id, uint32_t id_mask) |

| CAN Filter Single Extended Frame w/RTR set Notes: More... | |

| void | can_enable_irq (uint32_t canport, uint8_t imr) |

| CAN Enable IRQ. More... | |

| void | can_disable_irq (uint32_t canport, uint8_t imr) |

| CAN Disable IRQ. More... | |

| bool | can_transmit_std (uint32_t canport, uint32_t id, bool rtr, uint8_t length, const uint8_t *data) |

| CAN Transmit Standard Frame. More... | |

| bool | can_transmit_ext (uint32_t canport, uint32_t id, bool rtr, uint8_t length, const uint8_t *data) |

| CAN Transmit Extended Frame. More... | |

| void | can_abort_transmit (uint32_t canport) |

| CAN Abort Transmit Aborts the current transmission. More... | |

| void | can_receive (uint32_t canport, uint32_t *id, bool *ext, bool *rtr, uint8_t *length, uint8_t *data) |

| CAN Receive Message If no data is in the RX buffer, id and length are set to 0. More... | |