cmu_common.h File Reference

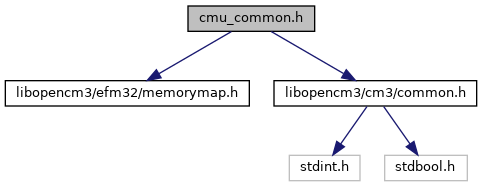

Include dependency graph for cmu_common.h:

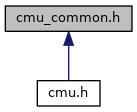

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Enumerations | |

| enum | cmu_periph_clken { CMU_PCNT2 = _REG_BIT(0x078, 4) , CMU_PCNT1 = _REG_BIT(0x078, 2) , CMU_PCNT0 = _REG_BIT(0x078, 0) , CMU_LEUART1 = _REG_BIT(0x060, 1) , CMU_LEUART0 = _REG_BIT(0x060, 0) , CMU_LCD = _REG_BIT(0x058, 3) , CMU_LETIMER0 = _REG_BIT(0x058, 2) , CMU_RTC = _REG_BIT(0x058, 1) , CMU_LESENSE = _REG_BIT(0x058, 0) , CMU_DAC0 = _REG_BIT(0x044, 17) , CMU_ADC0 = _REG_BIT(0x044, 16) , CMU_PRS = _REG_BIT(0x044, 15) , CMU_VCMP = _REG_BIT(0x044, 14) , CMU_GPIO = _REG_BIT(0x044, 13) , CMU_I2C1 = _REG_BIT(0x044, 12) , CMU_I2C0 = _REG_BIT(0x044, 11) , CMU_ACMP1 = _REG_BIT(0x044, 10) , CMU_ACMP0 = _REG_BIT(0x044, 9) , CMU_TIMER3 = _REG_BIT(0x044, 8) , CMU_TIMER2 = _REG_BIT(0x044, 7) , CMU_TIMER1 = _REG_BIT(0x044, 6) , CMU_TIMER0 = _REG_BIT(0x044, 5) , CMU_UART1 = _REG_BIT(0x044, 4) , CMU_UART0 = _REG_BIT(0x044, 3) , CMU_USART2 = _REG_BIT(0x044, 2) , CMU_USART1 = _REG_BIT(0x044, 1) , CMU_USART0 = _REG_BIT(0x044, 0) , CMU_EBI = _REG_BIT(0x040, 5) , CMU_LE = _REG_BIT(0x040, 4) , CMU_USB = _REG_BIT(0x040, 3) , CMU_USBC = _REG_BIT(0x040, 2) , CMU_AES = _REG_BIT(0x040, 1) , CMU_DMA = _REG_BIT(0x040, 0) } |

| enum | cmu_osc { HFRCO , LFRCO , ULFRCO , HFXO , LFXO , AUXHFRCO } |

Functions | |

| void | cmu_enable_lock (void) |

| Enable CMU registers lock. More... | |

| void | cmu_disable_lock (void) |

| Disable CMU registers lock. More... | |

| bool | cmu_get_lock_flag (void) |

| Get CMU register lock flag. More... | |

| void | cmu_periph_clock_enable (enum cmu_periph_clken periph) |

| Enable Peripheral Clock in running mode. More... | |

| void | cmu_periph_clock_disable (enum cmu_periph_clken periph) |

| Disable Peripheral Clock in running mode. More... | |

| void | cmu_osc_on (enum cmu_osc osc) |

| Turn on Oscillator. More... | |

| void | cmu_osc_off (enum cmu_osc osc) |

| Turn off Oscillator. More... | |

| bool | cmu_osc_ready_flag (enum cmu_osc osc) |

| Get Oscillator read flag. More... | |

| void | cmu_wait_for_osc_ready (enum cmu_osc osc) |

| Wait till oscillator is not ready. More... | |

| void | cmu_set_hfclk_source (enum cmu_osc osc) |

| Set HFCLK clock source. More... | |

| void | cmu_set_usbclk_source (enum cmu_osc osc) |

| enum cmu_osc | cmu_get_hfclk_source (void) |

| void | cmu_clock_setup_in_hfxo_out_48mhz (void) |

| HFXO output 48Mhz and core running at 48Mhz. More... | |