Macros | |

| #define | LSI_FREQUENCY 32000 |

| #define | COUNT_LENGTH 12 |

| #define | COUNT_MASK ((1 << COUNT_LENGTH)-1) |

Functions | |

| void | iwdg_start (void) |

| IWDG Enable Watchdog Timer. More... | |

| void | iwdg_set_period_ms (uint32_t period) |

| IWDG Set Period in Milliseconds. More... | |

| bool | iwdg_reload_busy (void) |

| IWDG Get Reload Register Status. More... | |

| bool | iwdg_prescaler_busy (void) |

| IWDG Get Prescaler Register Status. More... | |

| void | iwdg_reset (void) |

| IWDG reset Watchdog Timer. More... | |

Detailed Description

This library supports the Independent Watchdog Timer System in the STM32F1xx series of ARM Cortex Microcontrollers by ST Microelectronics.

The watchdog timer uses the LSI (low speed internal) clock which is low power and continues to operate during stop and standby modes. Its frequency is nominally 32kHz (40kHz for the STM32F1xx series) but can vary from as low as 17kHz up to 60kHz (refer to datasheet electrical characteristics).

Note that the User Configuration option byte provides a means of automatically enabling the IWDG timer at power on (with counter value 0xFFF). If the relevant bit is not set, the IWDG timer must be enabled by software.

- Note

- : Tested: CPU STM32F103RET6, Board ET-ARM Stamp STM32

Macro Definition Documentation

◆ COUNT_LENGTH

| #define COUNT_LENGTH 12 |

Definition at line 43 of file iwdg_common_all.c.

◆ COUNT_MASK

| #define COUNT_MASK ((1 << COUNT_LENGTH)-1) |

Definition at line 44 of file iwdg_common_all.c.

◆ LSI_FREQUENCY

| #define LSI_FREQUENCY 32000 |

Definition at line 42 of file iwdg_common_all.c.

Function Documentation

◆ iwdg_prescaler_busy()

| bool iwdg_prescaler_busy | ( | void | ) |

IWDG Get Prescaler Register Status.

- Returns

- boolean: TRUE if the prescaler register is busy and unavailable for loading a new period value.

Definition at line 135 of file iwdg_common_all.c.

References IWDG_SR, and IWDG_SR_PVU.

Referenced by iwdg_set_period_ms().

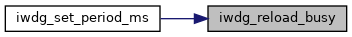

◆ iwdg_reload_busy()

| bool iwdg_reload_busy | ( | void | ) |

IWDG Get Reload Register Status.

- Returns

- boolean: TRUE if the reload register is busy and unavailable for loading a new count value.

Definition at line 123 of file iwdg_common_all.c.

References IWDG_SR, and IWDG_SR_RVU.

Referenced by iwdg_set_period_ms().

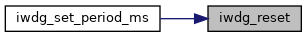

◆ iwdg_reset()

| void iwdg_reset | ( | void | ) |

IWDG reset Watchdog Timer.

The watchdog timer is reset. The counter restarts from the value in the reload register.

Definition at line 147 of file iwdg_common_all.c.

References IWDG_KR, and IWDG_KR_RESET.

Referenced by iwdg_set_period_ms().

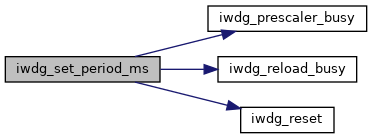

◆ iwdg_set_period_ms()

| void iwdg_set_period_ms | ( | uint32_t | period | ) |

IWDG Set Period in Milliseconds.

The countdown period is converted into count and prescale values. The maximum period is 32.76 seconds; values above this are truncated. Periods less than 1ms are not supported by this library.

A delay of up to 5 clock cycles of the LSI clock (about 156 microseconds) can occasionally occur if the prescale or preload registers are currently busy loading a previous value.

- Parameters

-

[in] period uint32_t Period in milliseconds (< 32760) from a watchdog reset until a system reset is issued.

Definition at line 73 of file iwdg_common_all.c.

References COUNT_LENGTH, COUNT_MASK, IWDG_KR, IWDG_KR_UNLOCK, IWDG_PR, iwdg_prescaler_busy(), iwdg_reload_busy(), iwdg_reset(), and IWDG_RLR.

◆ iwdg_start()

| void iwdg_start | ( | void | ) |

IWDG Enable Watchdog Timer.

The watchdog timer is started. The timeout period defaults to 512 milliseconds unless it has been previously defined.

Definition at line 54 of file iwdg_common_all.c.

References IWDG_KR, and IWDG_KR_START.