Ethernet MAC STM32Fxx7 Drivers More...

Functions | |

| void | eth_set_mac (const uint8_t *mac) |

| Set MAC to the PHY. More... | |

| void | eth_desc_init (uint8_t *buf, uint32_t nTx, uint32_t nRx, uint32_t cTx, uint32_t cRx, bool isext) |

| Initialize buffers and descriptors. More... | |

| bool | eth_tx (uint8_t *ppkt, uint32_t n) |

| Transmit packet. More... | |

| bool | eth_rx (uint8_t *ppkt, uint32_t *len, uint32_t maxlen) |

| Receive packet. More... | |

| void | eth_start (void) |

| Start the Ethernet DMA processing. More... | |

| void | eth_init (uint8_t phy, enum eth_clk clock) |

| Initialize ethernet. More... | |

| void | eth_irq_enable (uint32_t reason) |

| Enable the Ethernet IRQ. More... | |

| void | eth_irq_disable (uint32_t reason) |

| Disable the Ethernet IRQ. More... | |

| bool | eth_irq_is_pending (uint32_t reason) |

| Check if IRQ is pending. More... | |

| bool | eth_irq_ack_pending (uint32_t reason) |

| Check if IRQ is pending, and acknowledge it. More... | |

| void | eth_enable_checksum_offload (void) |

| Enable checksum offload feature. More... | |

| static void | eth_smi_transact (void) |

| Process pending SMI transaction and wait to be done. More... | |

| void | eth_smi_write (uint8_t phy, uint8_t reg, uint16_t data) |

| Write 16-bit register to the PHY. More... | |

| uint16_t | eth_smi_read (uint8_t phy, uint8_t reg) |

| Read the 16-bit register from the PHY. More... | |

| void | eth_smi_bit_op (uint8_t phy, uint8_t reg, uint16_t bits, uint16_t mask) |

| Process the bit-operation on PHY register. More... | |

| void | eth_smi_bit_clear (uint8_t phy, uint8_t reg, uint16_t clearbits) |

| Clear bits in the register. More... | |

| void | eth_smi_bit_set (uint8_t phy, uint8_t reg, uint16_t setbits) |

| Set bits in the register. More... | |

Variables | |

| uint32_t | TxBD |

| uint32_t | RxBD |

Detailed Description

Ethernet MAC STM32Fxx7 Drivers

- Version

- 1.0.0

- Date

- 1 September 2013

LGPL License Terms libopencm3 License

Function Documentation

◆ eth_desc_init()

| void eth_desc_init | ( | uint8_t * | buf, |

| uint32_t | nTx, | ||

| uint32_t | nRx, | ||

| uint32_t | cTx, | ||

| uint32_t | cRx, | ||

| bool | isext | ||

| ) |

Initialize buffers and descriptors.

- Parameters

-

[in] buf uint8_t* Memory area for the descriptors and data buffers [in] nTx uint32_t Count of transmit descriptors (equal to count of buffers) [in] nRx uint32_t Count of receive descriptors (equal to count of buffers) [in] cTx uint32_t Bytes in each transmit buffer, must be a multiple of 4 [in] cRx uint32_t Bytes in each receive buffer, must be a multiple of 4 [in] isext bool true if extended descriptors should be used

Note, the space passed via buf pointer must be large enough to hold all the buffers and one descriptor per buffer.

Definition at line 73 of file mac_stm32fxx7.c.

References ETH_DES0, ETH_DES1, ETH_DES2, ETH_DES3, ETH_DES_EXT_SIZE, ETH_DES_STD_SIZE, ETH_DMABMR, ETH_DMABMR_EDFE, ETH_DMARDLAR, ETH_DMATDLAR, ETH_RDES0_OWN, ETH_RDES1_RCH, ETH_TDES0_TCH, RxBD, and TxBD.

◆ eth_enable_checksum_offload()

| void eth_enable_checksum_offload | ( | void | ) |

Enable checksum offload feature.

This function will enable the Checksum offload feature for all of the transmit descriptors. Note to use this feature, descriptors must be in extended format.

Definition at line 279 of file mac_stm32fxx7.c.

References ETH_DES0, ETH_DES3, ETH_MACCR, ETH_MACCR_IPCO, ETH_TDES0_CIC_IPPLPH, and TxBD.

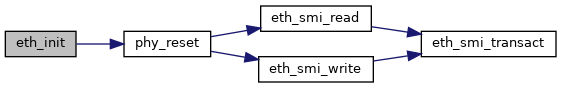

◆ eth_init()

| void eth_init | ( | uint8_t | phy, |

| enum eth_clk | clock | ||

| ) |

Initialize ethernet.

This function will initialize ethernet, set up clocks, and initialize DMA.

- Parameters

-

[in] phy phy id [in] clock enum eth_clk Core clock speed

Definition at line 209 of file mac_stm32fxx7.c.

References ETH_DMABMR, ETH_DMABMR_AAB, ETH_DMABMR_FB, ETH_DMABMR_PBL_SHIFT, ETH_DMABMR_PM_2_1, ETH_DMABMR_RDP_SHIFT, ETH_DMABMR_USP, ETH_DMAOMR, ETH_DMAOMR_DFRF, ETH_DMAOMR_DTCEFD, ETH_DMAOMR_FEF, ETH_DMAOMR_OSF, ETH_DMAOMR_RSF, ETH_DMAOMR_TSF, ETH_MACCR, ETH_MACCR_APCS, ETH_MACCR_CSTF, ETH_MACCR_DM, ETH_MACCR_FES, ETH_MACCR_RD, ETH_MACFCR, ETH_MACFCR_PT_SHIFT, ETH_MACFFR, ETH_MACFFR_PM, ETH_MACFFR_RA, ETH_MACHTHR, ETH_MACHTLR, ETH_MACMIIAR, ETH_MACVLANTR, and phy_reset().

◆ eth_irq_ack_pending()

| bool eth_irq_ack_pending | ( | uint32_t | reason | ) |

Check if IRQ is pending, and acknowledge it.

- Parameters

-

[in] reason uint32_t Which irq type has to be tested

- Returns

- bool true, if IRQ is pending

Definition at line 265 of file mac_stm32fxx7.c.

References ETH_DMASR.

◆ eth_irq_disable()

| void eth_irq_disable | ( | uint32_t | reason | ) |

Disable the Ethernet IRQ.

- Parameters

-

[in] reason uint32_t Which irq will be disabled

Definition at line 243 of file mac_stm32fxx7.c.

References ETH_DMAIER.

◆ eth_irq_enable()

| void eth_irq_enable | ( | uint32_t | reason | ) |

Enable the Ethernet IRQ.

- Parameters

-

[in] reason uint32_t Which irq will be enabled

Definition at line 233 of file mac_stm32fxx7.c.

References ETH_DMAIER.

◆ eth_irq_is_pending()

| bool eth_irq_is_pending | ( | uint32_t | reason | ) |

Check if IRQ is pending.

- Parameters

-

[in] reason uint32_t Which irq type has to be tested

- Returns

- bool true, if IRQ is pending

Definition at line 254 of file mac_stm32fxx7.c.

References ETH_DMASR.

◆ eth_rx()

| bool eth_rx | ( | uint8_t * | ppkt, |

| uint32_t * | len, | ||

| uint32_t | maxlen | ||

| ) |

Receive packet.

- Parameters

-

[in,out] ppkt uint8_t* Pointer to the data buffer where to store data [in,out] len uint32_t* Pointer to the variable with the packet length [in] maxlen uint32_t Maximum length of the packet

- Returns

- bool true, if the buffer contains readed packet data

Definition at line 154 of file mac_stm32fxx7.c.

References ETH_DES0, ETH_DES2, ETH_DES3, ETH_DMARPDR, ETH_DMASR, ETH_DMASR_RBUS, ETH_RDES0_FL, ETH_RDES0_FL_SHIFT, ETH_RDES0_FS, ETH_RDES0_LS, ETH_RDES0_OWN, and RxBD.

◆ eth_set_mac()

| void eth_set_mac | ( | const uint8_t * | mac | ) |

Set MAC to the PHY.

- Parameters

-

[in] mac uint8_t* Desired MAC

Definition at line 50 of file mac_stm32fxx7.c.

References ETH_MACA0HR_MACA0H, ETH_MACAHR, and ETH_MACALR.

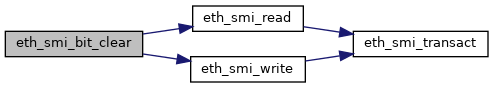

◆ eth_smi_bit_clear()

| void eth_smi_bit_clear | ( | uint8_t | phy, |

| uint8_t | reg, | ||

| uint16_t | clearbits | ||

| ) |

Clear bits in the register.

- Parameters

-

[in] phy uint8_t ID of the PHY (defaults to 1) [in] reg uint8_t Register address [in] clearbits uint16_t Bits that have to be cleared

Definition at line 363 of file mac_stm32fxx7.c.

References eth_smi_read(), and eth_smi_write().

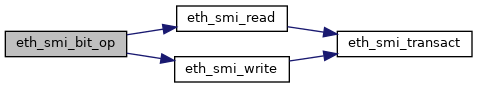

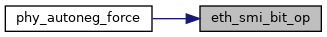

◆ eth_smi_bit_op()

| void eth_smi_bit_op | ( | uint8_t | phy, |

| uint8_t | reg, | ||

| uint16_t | bits, | ||

| uint16_t | mask | ||

| ) |

Process the bit-operation on PHY register.

- Parameters

-

[in] phy uint8_t ID of the PHY (defaults to 1) [in] reg uint8_t Register address [in] bits uint16_t Bits that have to be set (or'ed) [in] mask uint16_t Bits that have to be clear (and'ed)

Definition at line 350 of file mac_stm32fxx7.c.

References eth_smi_read(), and eth_smi_write().

Referenced by phy_autoneg_force().

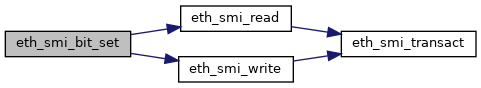

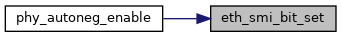

◆ eth_smi_bit_set()

| void eth_smi_bit_set | ( | uint8_t | phy, |

| uint8_t | reg, | ||

| uint16_t | setbits | ||

| ) |

Set bits in the register.

- Parameters

-

[in] phy uint8_t ID of the PHY (defaults to 1) [in] reg uint8_t Register address [in] setbits uint16_t Bits that have to be set (or'ed)

Definition at line 376 of file mac_stm32fxx7.c.

References eth_smi_read(), and eth_smi_write().

Referenced by phy_autoneg_enable().

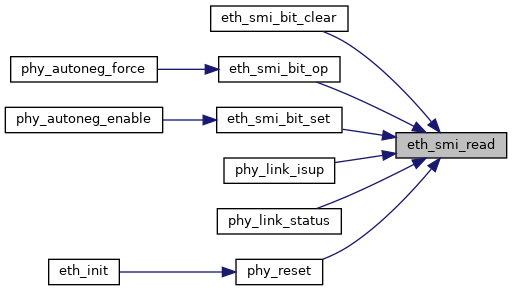

◆ eth_smi_read()

| uint16_t eth_smi_read | ( | uint8_t | phy, |

| uint8_t | reg | ||

| ) |

Read the 16-bit register from the PHY.

- Parameters

-

[in] phy uint8_t ID of the PHY (defaults to 1) [in] reg uint8_t Register address

- Returns

- uint16_t Readed data

Definition at line 330 of file mac_stm32fxx7.c.

References ETH_MACMIIAR, ETH_MACMIIAR_CR, ETH_MACMIIAR_MR_SHIFT, ETH_MACMIIAR_PA_SHIFT, ETH_MACMIIDR, ETH_MACMIIDR_MD, and eth_smi_transact().

Referenced by eth_smi_bit_clear(), eth_smi_bit_op(), eth_smi_bit_set(), phy_link_isup(), phy_link_status(), and phy_reset().

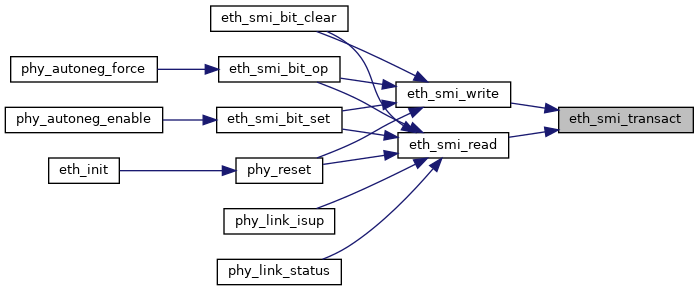

◆ eth_smi_transact()

|

static |

Process pending SMI transaction and wait to be done.

Definition at line 294 of file mac_stm32fxx7.c.

References ETH_MACMIIAR, and ETH_MACMIIAR_MB.

Referenced by eth_smi_read(), and eth_smi_write().

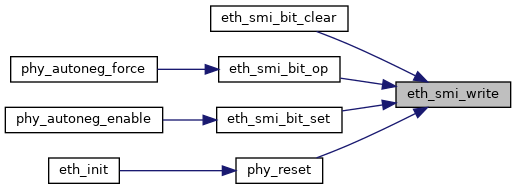

◆ eth_smi_write()

| void eth_smi_write | ( | uint8_t | phy, |

| uint8_t | reg, | ||

| uint16_t | data | ||

| ) |

Write 16-bit register to the PHY.

- Parameters

-

[in] phy uint8_t ID of the PHY (defaults to 1) [in] reg uint8_t Register address [in] data uint16_t Data to write

Definition at line 310 of file mac_stm32fxx7.c.

References ETH_MACMIIAR, ETH_MACMIIAR_CR, ETH_MACMIIAR_MR_SHIFT, ETH_MACMIIAR_MW, ETH_MACMIIAR_PA_SHIFT, ETH_MACMIIDR, ETH_MACMIIDR_MD, and eth_smi_transact().

Referenced by eth_smi_bit_clear(), eth_smi_bit_op(), eth_smi_bit_set(), and phy_reset().

◆ eth_start()

| void eth_start | ( | void | ) |

Start the Ethernet DMA processing.

Definition at line 191 of file mac_stm32fxx7.c.

References ETH_DMAOMR, ETH_DMAOMR_FTF, ETH_DMAOMR_SR, ETH_DMAOMR_ST, ETH_MACCR, ETH_MACCR_RE, and ETH_MACCR_TE.

◆ eth_tx()

| bool eth_tx | ( | uint8_t * | ppkt, |

| uint32_t | n | ||

| ) |

Transmit packet.

- Parameters

-

[in] ppkt uint8_t* Pointer to the beginning of the packet [in] n uint32_t Size of the packet

- Returns

- bool true, if success

Definition at line 126 of file mac_stm32fxx7.c.

References ETH_DES0, ETH_DES1, ETH_DES2, ETH_DES3, ETH_DMASR, ETH_DMASR_TBUS, ETH_DMATPDR, ETH_TDES0_FS, ETH_TDES0_LS, ETH_TDES0_OWN, ETH_TDES1_TBS1, and TxBD.

Variable Documentation

◆ RxBD

| uint32_t RxBD |

Definition at line 43 of file mac_stm32fxx7.c.

Referenced by eth_desc_init(), and eth_rx().

◆ TxBD

| uint32_t TxBD |

Definition at line 42 of file mac_stm32fxx7.c.

Referenced by eth_desc_init(), eth_enable_checksum_offload(), and eth_tx().