Defined Constants and Types for the STM32F7xx I2C More...

Modules | |

| I2C register base address | |

Macros | |

| #define | I2C_CR1(i2c_base) MMIO32((i2c_base) + 0x00) |

| #define | I2C1_CR1 I2C_CR1(I2C1) |

| #define | I2C2_CR1 I2C_CR1(I2C2) |

| #define | I2C_CR2(i2c_base) MMIO32((i2c_base) + 0x04) |

| #define | I2C1_CR2 I2C_CR2(I2C1) |

| #define | I2C2_CR2 I2C_CR2(I2C2) |

| #define | I2C_OAR1(i2c_base) MMIO32((i2c_base) + 0x08) |

| #define | I2C1_OAR1 I2C_OAR1(I2C1) |

| #define | I2C2_OAR1 I2C_OAR1(I2C2) |

| #define | I2C_OAR2(i2c_base) MMIO32((i2c_base) + 0x0c) |

| #define | I2C1_OAR2 I2C_OAR2(I2C1) |

| #define | I2C2_OAR2 I2C_OAR2(I2C2) |

| #define | I2C_TIMINGR(i2c_base) MMIO32((i2c_base) + 0x10) |

| #define | I2C1_TIMINGR I2C_TIMINGR(I2C1) |

| #define | I2C2_TIMINGR I2C_TIMINGR(I2C2) |

| #define | I2C_TIMEOUTR(i2c_base) MMIO32((i2c_base) + 0x14) |

| #define | I2C1_TIMEOUTR I2C_TIMEOUTR(I2C1) |

| #define | I2C2_TIMEOUTR I2C_TIMEOUTR(I2C2) |

| #define | I2C_ISR(i2c_base) MMIO32((i2c_base) + 0x18) |

| #define | I2C1_ISR I2C_ISR(I2C1) |

| #define | I2C2_ISR I2C_ISR(I2C2) |

| #define | I2C_ICR(i2c_base) MMIO32((i2c_base) + 0x1C) |

| #define | I2C1_ICR I2C_ICR(I2C1) |

| #define | I2C2_ICR I2C_ICR(I2C2) |

| #define | I2C_PECR(i2c_base) MMIO32((i2c_base) + 0x20) |

| #define | I2C1_PECR I2C_PECR(I2C1) |

| #define | I2C2_PECR I2C_PECR(I2C2) |

| #define | I2C_RXDR(i2c_base) MMIO32((i2c_base) + 0x24) |

| #define | I2C1_RXDR I2C_RXDR(I2C1) |

| #define | I2C2_RXDR I2C_RXDR(I2C2) |

| #define | I2C_TXDR(i2c_base) MMIO32((i2c_base) + 0x28) |

| #define | I2C1_TXDR I2C_TXDR(I2C1) |

| #define | I2C2_TXDR I2C_TXDR(I2C2) |

| #define | I2C_CR1_PECEN (1 << 23) |

| #define | I2C_CR1_ALERTEN (1 << 22) |

| #define | I2C_CR1_SMBDEN (1 << 21) |

| #define | I2C_CR1_SMBHEN (1 << 20) |

| #define | I2C_CR1_GCEN (1 << 19) |

| #define | I2C_CR1_WUPEN (1 << 18) |

| #define | I2C_CR1_NOSTRETCH (1 << 17) |

| #define | I2C_CR1_SBC (1 << 16) |

| #define | I2C_CR1_RXDMAEN (1 << 15) |

| #define | I2C_CR1_TXDMAEN (1 << 14) |

| #define | I2C_CR1_ANFOFF (1 << 12) |

| #define | I2C_CR1_DNF_MASK 0xF |

| DNF[3:0]: Digital noise filter. More... | |

| #define | I2C_CR1_DNF_SHIFT 8 |

| #define | I2C_CR1_ERRIE (1 << 7) |

| #define | I2C_CR1_TCIE (1 << 6) |

| #define | I2C_CR1_STOPIE (1 << 5) |

| #define | I2C_CR1_NACKIE (1 << 4) |

| #define | I2C_CR1_ADDRIE (1 << 3) |

| #define | I2C_CR1_RXIE (1 << 2) |

| #define | I2C_CR1_TXIE (1 << 1) |

| #define | I2C_CR1_PE (1 << 0) |

| #define | I2C_CR2_PECBYTE (1 << 26) |

| #define | I2C_CR2_AUTOEND (1 << 25) |

| #define | I2C_CR2_RELOAD (1 << 24) |

| #define | I2C_CR2_NBYTES_SHIFT 16 |

| #define | I2C_CR2_NBYTES_MASK (0xFF << I2C_CR2_NBYTES_SHIFT) |

| #define | I2C_CR2_NACK (1 << 15) |

| #define | I2C_CR2_STOP (1 << 14) |

| #define | I2C_CR2_START (1 << 13) |

| #define | I2C_CR2_HEAD10R (1 << 12) |

| #define | I2C_CR2_ADD10 (1 << 11) |

| #define | I2C_CR2_RD_WRN (1 << 10) |

| #define | I2C_CR2_SADD_7BIT_SHIFT 1 |

| #define | I2C_CR2_SADD_10BIT_SHIFT 0 |

| #define | I2C_CR2_SADD_7BIT_MASK (0x7F << I2C_CR2_SADD_7BIT_SHIFT) |

| #define | I2C_CR2_SADD_10BIT_MASK 0x3FF |

| #define | I2C_OAR1_OA1EN_DISABLE (0x0 << 15) |

| #define | I2C_OAR1_OA1EN_ENABLE (0x1 << 15) |

| #define | I2C_OAR1_OA1MODE (1 << 10) |

| #define | I2C_OAR1_OA1MODE_7BIT 0 |

| #define | I2C_OAR1_OA1MODE_10BIT 1 |

| #define | I2C_OAR1_OA1 (1 << 10) |

| #define | I2C_OAR1_OA1_7BIT 0 |

| #define | I2C_OAR1_OA1_10BIT 1 |

| #define | I2C_OAR2_OA2EN (1 << 15) |

| #define | I2C_OAR2_OA2MSK_NO_MASK (0x0 << 8) |

| #define | I2C_OAR2_OA2MSK_OA2_7_OA2_2 (0x1 << 8) |

| #define | I2C_OAR2_OA2MSK_OA2_7_OA2_3 (0x2 << 8) |

| #define | I2C_OAR2_OA2MSK_OA2_7_OA2_4 (0x3 << 8) |

| #define | I2C_OAR2_OA2MSK_OA2_7_OA2_5 (0x4 << 8) |

| #define | I2C_OAR2_OA2MSK_OA2_7_OA2_6 (0x5 << 8) |

| #define | I2C_OAR2_OA2MSK_OA2_7 (0x6 << 8) |

| #define | I2C_OAR2_OA2MSK_NO_CMP (0x7 << 8) |

| #define | I2C_TIMINGR_PRESC_SHIFT 28 |

| #define | I2C_TIMINGR_PRESC_MASK (0xF << 28) |

| #define | I2C_TIMINGR_SCLDEL_SHIFT 20 |

| #define | I2C_TIMINGR_SCLDEL_MASK (0xF << I2C_TIMINGR_SCLDEL_SHIFT) |

| #define | I2C_TIMINGR_SDADEL_SHIFT 16 |

| #define | I2C_TIMINGR_SDADEL_MASK (0xF << I2C_TIMINGR_SDADEL_SHIFT) |

| #define | I2C_TIMINGR_SCLH_SHIFT 8 |

| #define | I2C_TIMINGR_SCLH_MASK (0xFF << I2C_TIMINGR_SCLH_SHIFT) |

| #define | I2C_TIMINGR_SCLL_SHIFT 0 |

| #define | I2C_TIMINGR_SCLL_MASK (0xFF << I2C_TIMINGR_SCLL_SHIFT) |

| #define | I2C_TIEMOUTR_TEXTEN (1 << 31) |

| #define | I2C_TIEMOUTR_TIMOUTEN (1 << 15) |

| #define | I2C_TIEMOUTR_TIDLE_SCL_LOW (0x0 << 12) |

| #define | I2C_TIEMOUTR_TIDLE_SCL_SDA_HIGH (0x1 << 12) |

| #define | I2C_ISR_DIR_READ (0x1 << 16) |

| #define | I2C_ISR_DIR_WRITE (0x0 << 16) |

| #define | I2C_ISR_BUSY (1 << 15) |

| #define | I2C_ISR_ALERT (1 << 13) |

| #define | I2C_ISR_TIMEOUT (1 << 12) |

| #define | I2C_ISR_PECERR (1 << 11) |

| #define | I2C_ISR_OVR (1 << 10) |

| #define | I2C_ISR_ARLO (1 << 9) |

| #define | I2C_ISR_BERR (1 << 8) |

| #define | I2C_ISR_TCR (1 << 7) |

| #define | I2C_ISR_TC (1 << 6) |

| #define | I2C_ISR_STOPF (1 << 5) |

| #define | I2C_ISR_NACKF (1 << 4) |

| #define | I2C_ISR_ADDR (1 << 3) |

| #define | I2C_ISR_RXNE (1 << 2) |

| #define | I2C_ISR_TXIS (1 << 1) |

| #define | I2C_ISR_TXE (1 << 0) |

| #define | I2C_ICR_ALERTCF (1 << 13) |

| #define | I2C_ICR_TIMOUTCF (1 << 12) |

| #define | I2C_ICR_PECCF (1 << 11) |

| #define | I2C_ICR_OVRCF (1 << 10) |

| #define | I2C_ICR_ARLOCF (1 << 9) |

| #define | I2C_ICR_BERRCF (1 << 8) |

| #define | I2C_ICR_STOPCF (1 << 5) |

| #define | I2C_ICR_NACKCF (1 << 4) |

| #define | I2C_ICR_ADDRCF (1 << 3) |

Enumerations | |

| enum | i2c_speeds { i2c_speed_sm_100k , i2c_speed_fm_400k , i2c_speed_fmp_1m , i2c_speed_unknown } |

| I2C speed modes. More... | |

Functions | |

| void | i2c_peripheral_enable (uint32_t i2c) |

| I2C Peripheral Enable. More... | |

| void | i2c_peripheral_disable (uint32_t i2c) |

| I2C Peripheral Disable. More... | |

| void | i2c_send_start (uint32_t i2c) |

| I2C Send Start Condition. More... | |

| void | i2c_send_stop (uint32_t i2c) |

| I2C Send Stop Condition. More... | |

| void | i2c_clear_stop (uint32_t i2c) |

| I2C Clear Stop Flag. More... | |

| void | i2c_set_own_7bit_slave_address (uint32_t i2c, uint8_t slave) |

| I2C Set the 7 bit Slave Address for the Peripheral. More... | |

| void | i2c_set_own_10bit_slave_address (uint32_t i2c, uint16_t slave) |

| I2C Set the 10 bit Slave Address for the Peripheral. More... | |

| void | i2c_send_data (uint32_t i2c, uint8_t data) |

| I2C Send Data. More... | |

| uint8_t | i2c_get_data (uint32_t i2c) |

| I2C Get Data. More... | |

| void | i2c_enable_analog_filter (uint32_t i2c) |

| void | i2c_disable_analog_filter (uint32_t i2c) |

| void | i2c_set_digital_filter (uint32_t i2c, uint8_t dnf_setting) |

| Set the I2C digital filter. More... | |

| void | i2c_set_prescaler (uint32_t i2c, uint8_t presc) |

| void | i2c_set_data_setup_time (uint32_t i2c, uint8_t s_time) |

| void | i2c_set_data_hold_time (uint32_t i2c, uint8_t h_time) |

| void | i2c_set_scl_high_period (uint32_t i2c, uint8_t period) |

| void | i2c_set_scl_low_period (uint32_t i2c, uint8_t period) |

| void | i2c_enable_stretching (uint32_t i2c) |

| void | i2c_disable_stretching (uint32_t i2c) |

| void | i2c_set_7bit_addr_mode (uint32_t i2c) |

| void | i2c_set_10bit_addr_mode (uint32_t i2c) |

| void | i2c_set_7bit_address (uint32_t i2c, uint8_t addr) |

| void | i2c_set_10bit_address (uint32_t i2c, uint16_t addr) |

| void | i2c_set_write_transfer_dir (uint32_t i2c) |

| void | i2c_set_read_transfer_dir (uint32_t i2c) |

| void | i2c_set_bytes_to_transfer (uint32_t i2c, uint32_t n_bytes) |

| bool | i2c_is_start (uint32_t i2c) |

| void | i2c_enable_autoend (uint32_t i2c) |

| void | i2c_disable_autoend (uint32_t i2c) |

| bool | i2c_nack (uint32_t i2c) |

| bool | i2c_busy (uint32_t i2c) |

| bool | i2c_transmit_int_status (uint32_t i2c) |

| bool | i2c_transfer_complete (uint32_t i2c) |

| bool | i2c_received_data (uint32_t i2c) |

| void | i2c_enable_interrupt (uint32_t i2c, uint32_t interrupt) |

| I2C Enable Interrupt. More... | |

| void | i2c_disable_interrupt (uint32_t i2c, uint32_t interrupt) |

| I2C Disable Interrupt. More... | |

| void | i2c_enable_rxdma (uint32_t i2c) |

| I2C Enable reception DMA. More... | |

| void | i2c_disable_rxdma (uint32_t i2c) |

| I2C Disable reception DMA. More... | |

| void | i2c_enable_txdma (uint32_t i2c) |

| I2C Enable transmission DMA. More... | |

| void | i2c_disable_txdma (uint32_t i2c) |

| I2C Disable transmission DMA. More... | |

| void | i2c_transfer7 (uint32_t i2c, uint8_t addr, const uint8_t *w, size_t wn, uint8_t *r, size_t rn) |

| Run a write/read transaction to a given 7bit i2c address If both write & read are provided, the read will use repeated start. More... | |

| void | i2c_set_speed (uint32_t i2c, enum i2c_speeds speed, uint32_t clock_megahz) |

| Set the i2c communication speed. More... | |

Detailed Description

Defined Constants and Types for the STM32F7xx I2C

- Version

- 1.0.0

- Date

- 04 April 2019

LGPL License Terms libopencm3 License

Macro Definition Documentation

◆ I2C1_CR1

Definition at line 58 of file i2c_common_v2.h.

◆ I2C1_CR2

Definition at line 63 of file i2c_common_v2.h.

◆ I2C1_ICR

Definition at line 93 of file i2c_common_v2.h.

◆ I2C1_ISR

Definition at line 88 of file i2c_common_v2.h.

◆ I2C1_OAR1

Definition at line 68 of file i2c_common_v2.h.

◆ I2C1_OAR2

Definition at line 73 of file i2c_common_v2.h.

◆ I2C1_PECR

Definition at line 98 of file i2c_common_v2.h.

◆ I2C1_RXDR

Definition at line 103 of file i2c_common_v2.h.

◆ I2C1_TIMEOUTR

| #define I2C1_TIMEOUTR I2C_TIMEOUTR(I2C1) |

Definition at line 83 of file i2c_common_v2.h.

◆ I2C1_TIMINGR

| #define I2C1_TIMINGR I2C_TIMINGR(I2C1) |

Definition at line 78 of file i2c_common_v2.h.

◆ I2C1_TXDR

Definition at line 108 of file i2c_common_v2.h.

◆ I2C2_CR1

Definition at line 59 of file i2c_common_v2.h.

◆ I2C2_CR2

Definition at line 64 of file i2c_common_v2.h.

◆ I2C2_ICR

Definition at line 94 of file i2c_common_v2.h.

◆ I2C2_ISR

Definition at line 89 of file i2c_common_v2.h.

◆ I2C2_OAR1

Definition at line 69 of file i2c_common_v2.h.

◆ I2C2_OAR2

Definition at line 74 of file i2c_common_v2.h.

◆ I2C2_PECR

Definition at line 99 of file i2c_common_v2.h.

◆ I2C2_RXDR

Definition at line 104 of file i2c_common_v2.h.

◆ I2C2_TIMEOUTR

| #define I2C2_TIMEOUTR I2C_TIMEOUTR(I2C2) |

Definition at line 84 of file i2c_common_v2.h.

◆ I2C2_TIMINGR

| #define I2C2_TIMINGR I2C_TIMINGR(I2C2) |

Definition at line 79 of file i2c_common_v2.h.

◆ I2C2_TXDR

Definition at line 109 of file i2c_common_v2.h.

◆ I2C_CR1

| #define I2C_CR1 | ( | i2c_base | ) | MMIO32((i2c_base) + 0x00) |

Definition at line 57 of file i2c_common_v2.h.

◆ I2C_CR1_ADDRIE

| #define I2C_CR1_ADDRIE (1 << 3) |

Definition at line 176 of file i2c_common_v2.h.

◆ I2C_CR1_ALERTEN

| #define I2C_CR1_ALERTEN (1 << 22) |

Definition at line 130 of file i2c_common_v2.h.

◆ I2C_CR1_ANFOFF

| #define I2C_CR1_ANFOFF (1 << 12) |

Definition at line 157 of file i2c_common_v2.h.

◆ I2C_CR1_DNF_MASK

| #define I2C_CR1_DNF_MASK 0xF |

DNF[3:0]: Digital noise filter.

Definition at line 160 of file i2c_common_v2.h.

◆ I2C_CR1_DNF_SHIFT

| #define I2C_CR1_DNF_SHIFT 8 |

Definition at line 161 of file i2c_common_v2.h.

◆ I2C_CR1_ERRIE

| #define I2C_CR1_ERRIE (1 << 7) |

Definition at line 164 of file i2c_common_v2.h.

◆ I2C_CR1_GCEN

| #define I2C_CR1_GCEN (1 << 19) |

Definition at line 139 of file i2c_common_v2.h.

◆ I2C_CR1_NACKIE

| #define I2C_CR1_NACKIE (1 << 4) |

Definition at line 173 of file i2c_common_v2.h.

◆ I2C_CR1_NOSTRETCH

| #define I2C_CR1_NOSTRETCH (1 << 17) |

Definition at line 145 of file i2c_common_v2.h.

◆ I2C_CR1_PE

| #define I2C_CR1_PE (1 << 0) |

Definition at line 185 of file i2c_common_v2.h.

◆ I2C_CR1_PECEN

| #define I2C_CR1_PECEN (1 << 23) |

Definition at line 127 of file i2c_common_v2.h.

◆ I2C_CR1_RXDMAEN

| #define I2C_CR1_RXDMAEN (1 << 15) |

Definition at line 151 of file i2c_common_v2.h.

◆ I2C_CR1_RXIE

| #define I2C_CR1_RXIE (1 << 2) |

Definition at line 179 of file i2c_common_v2.h.

◆ I2C_CR1_SBC

| #define I2C_CR1_SBC (1 << 16) |

Definition at line 148 of file i2c_common_v2.h.

◆ I2C_CR1_SMBDEN

| #define I2C_CR1_SMBDEN (1 << 21) |

Definition at line 133 of file i2c_common_v2.h.

◆ I2C_CR1_SMBHEN

| #define I2C_CR1_SMBHEN (1 << 20) |

Definition at line 136 of file i2c_common_v2.h.

◆ I2C_CR1_STOPIE

| #define I2C_CR1_STOPIE (1 << 5) |

Definition at line 170 of file i2c_common_v2.h.

◆ I2C_CR1_TCIE

| #define I2C_CR1_TCIE (1 << 6) |

Definition at line 167 of file i2c_common_v2.h.

◆ I2C_CR1_TXDMAEN

| #define I2C_CR1_TXDMAEN (1 << 14) |

Definition at line 154 of file i2c_common_v2.h.

◆ I2C_CR1_TXIE

| #define I2C_CR1_TXIE (1 << 1) |

Definition at line 182 of file i2c_common_v2.h.

◆ I2C_CR1_WUPEN

| #define I2C_CR1_WUPEN (1 << 18) |

Definition at line 142 of file i2c_common_v2.h.

◆ I2C_CR2

| #define I2C_CR2 | ( | i2c_base | ) | MMIO32((i2c_base) + 0x04) |

Definition at line 62 of file i2c_common_v2.h.

◆ I2C_CR2_ADD10

| #define I2C_CR2_ADD10 (1 << 11) |

Definition at line 215 of file i2c_common_v2.h.

◆ I2C_CR2_AUTOEND

| #define I2C_CR2_AUTOEND (1 << 25) |

Definition at line 193 of file i2c_common_v2.h.

◆ I2C_CR2_HEAD10R

| #define I2C_CR2_HEAD10R (1 << 12) |

Definition at line 212 of file i2c_common_v2.h.

◆ I2C_CR2_NACK

| #define I2C_CR2_NACK (1 << 15) |

Definition at line 203 of file i2c_common_v2.h.

◆ I2C_CR2_NBYTES_MASK

| #define I2C_CR2_NBYTES_MASK (0xFF << I2C_CR2_NBYTES_SHIFT) |

Definition at line 200 of file i2c_common_v2.h.

◆ I2C_CR2_NBYTES_SHIFT

| #define I2C_CR2_NBYTES_SHIFT 16 |

Definition at line 199 of file i2c_common_v2.h.

◆ I2C_CR2_PECBYTE

| #define I2C_CR2_PECBYTE (1 << 26) |

Definition at line 190 of file i2c_common_v2.h.

◆ I2C_CR2_RD_WRN

| #define I2C_CR2_RD_WRN (1 << 10) |

Definition at line 218 of file i2c_common_v2.h.

◆ I2C_CR2_RELOAD

| #define I2C_CR2_RELOAD (1 << 24) |

Definition at line 196 of file i2c_common_v2.h.

◆ I2C_CR2_SADD_10BIT_MASK

| #define I2C_CR2_SADD_10BIT_MASK 0x3FF |

Definition at line 223 of file i2c_common_v2.h.

◆ I2C_CR2_SADD_10BIT_SHIFT

| #define I2C_CR2_SADD_10BIT_SHIFT 0 |

Definition at line 221 of file i2c_common_v2.h.

◆ I2C_CR2_SADD_7BIT_MASK

| #define I2C_CR2_SADD_7BIT_MASK (0x7F << I2C_CR2_SADD_7BIT_SHIFT) |

Definition at line 222 of file i2c_common_v2.h.

◆ I2C_CR2_SADD_7BIT_SHIFT

| #define I2C_CR2_SADD_7BIT_SHIFT 1 |

Definition at line 220 of file i2c_common_v2.h.

◆ I2C_CR2_START

| #define I2C_CR2_START (1 << 13) |

Definition at line 209 of file i2c_common_v2.h.

◆ I2C_CR2_STOP

| #define I2C_CR2_STOP (1 << 14) |

Definition at line 206 of file i2c_common_v2.h.

◆ I2C_ICR

| #define I2C_ICR | ( | i2c_base | ) | MMIO32((i2c_base) + 0x1C) |

Definition at line 92 of file i2c_common_v2.h.

◆ I2C_ICR_ADDRCF

| #define I2C_ICR_ADDRCF (1 << 3) |

Definition at line 385 of file i2c_common_v2.h.

◆ I2C_ICR_ALERTCF

| #define I2C_ICR_ALERTCF (1 << 13) |

Definition at line 361 of file i2c_common_v2.h.

◆ I2C_ICR_ARLOCF

| #define I2C_ICR_ARLOCF (1 << 9) |

Definition at line 373 of file i2c_common_v2.h.

◆ I2C_ICR_BERRCF

| #define I2C_ICR_BERRCF (1 << 8) |

Definition at line 376 of file i2c_common_v2.h.

◆ I2C_ICR_NACKCF

| #define I2C_ICR_NACKCF (1 << 4) |

Definition at line 382 of file i2c_common_v2.h.

◆ I2C_ICR_OVRCF

| #define I2C_ICR_OVRCF (1 << 10) |

Definition at line 370 of file i2c_common_v2.h.

◆ I2C_ICR_PECCF

| #define I2C_ICR_PECCF (1 << 11) |

Definition at line 367 of file i2c_common_v2.h.

◆ I2C_ICR_STOPCF

| #define I2C_ICR_STOPCF (1 << 5) |

Definition at line 379 of file i2c_common_v2.h.

◆ I2C_ICR_TIMOUTCF

| #define I2C_ICR_TIMOUTCF (1 << 12) |

Definition at line 364 of file i2c_common_v2.h.

◆ I2C_ISR

| #define I2C_ISR | ( | i2c_base | ) | MMIO32((i2c_base) + 0x18) |

Definition at line 87 of file i2c_common_v2.h.

◆ I2C_ISR_ADDR

| #define I2C_ISR_ADDR (1 << 3) |

Definition at line 347 of file i2c_common_v2.h.

◆ I2C_ISR_ALERT

| #define I2C_ISR_ALERT (1 << 13) |

Definition at line 317 of file i2c_common_v2.h.

◆ I2C_ISR_ARLO

| #define I2C_ISR_ARLO (1 << 9) |

Definition at line 329 of file i2c_common_v2.h.

◆ I2C_ISR_BERR

| #define I2C_ISR_BERR (1 << 8) |

Definition at line 332 of file i2c_common_v2.h.

◆ I2C_ISR_BUSY

| #define I2C_ISR_BUSY (1 << 15) |

Definition at line 314 of file i2c_common_v2.h.

◆ I2C_ISR_DIR_READ

| #define I2C_ISR_DIR_READ (0x1 << 16) |

Definition at line 310 of file i2c_common_v2.h.

◆ I2C_ISR_DIR_WRITE

| #define I2C_ISR_DIR_WRITE (0x0 << 16) |

Definition at line 311 of file i2c_common_v2.h.

◆ I2C_ISR_NACKF

| #define I2C_ISR_NACKF (1 << 4) |

Definition at line 344 of file i2c_common_v2.h.

◆ I2C_ISR_OVR

| #define I2C_ISR_OVR (1 << 10) |

Definition at line 326 of file i2c_common_v2.h.

◆ I2C_ISR_PECERR

| #define I2C_ISR_PECERR (1 << 11) |

Definition at line 323 of file i2c_common_v2.h.

◆ I2C_ISR_RXNE

| #define I2C_ISR_RXNE (1 << 2) |

Definition at line 350 of file i2c_common_v2.h.

◆ I2C_ISR_STOPF

| #define I2C_ISR_STOPF (1 << 5) |

Definition at line 341 of file i2c_common_v2.h.

◆ I2C_ISR_TC

| #define I2C_ISR_TC (1 << 6) |

Definition at line 338 of file i2c_common_v2.h.

◆ I2C_ISR_TCR

| #define I2C_ISR_TCR (1 << 7) |

Definition at line 335 of file i2c_common_v2.h.

◆ I2C_ISR_TIMEOUT

| #define I2C_ISR_TIMEOUT (1 << 12) |

Definition at line 320 of file i2c_common_v2.h.

◆ I2C_ISR_TXE

| #define I2C_ISR_TXE (1 << 0) |

Definition at line 356 of file i2c_common_v2.h.

◆ I2C_ISR_TXIS

| #define I2C_ISR_TXIS (1 << 1) |

Definition at line 353 of file i2c_common_v2.h.

◆ I2C_OAR1

| #define I2C_OAR1 | ( | i2c_base | ) | MMIO32((i2c_base) + 0x08) |

Definition at line 67 of file i2c_common_v2.h.

◆ I2C_OAR1_OA1

| #define I2C_OAR1_OA1 (1 << 10) |

Definition at line 241 of file i2c_common_v2.h.

◆ I2C_OAR1_OA1_10BIT

| #define I2C_OAR1_OA1_10BIT 1 |

Definition at line 243 of file i2c_common_v2.h.

◆ I2C_OAR1_OA1_7BIT

| #define I2C_OAR1_OA1_7BIT 0 |

Definition at line 242 of file i2c_common_v2.h.

◆ I2C_OAR1_OA1EN_DISABLE

| #define I2C_OAR1_OA1EN_DISABLE (0x0 << 15) |

Definition at line 228 of file i2c_common_v2.h.

◆ I2C_OAR1_OA1EN_ENABLE

| #define I2C_OAR1_OA1EN_ENABLE (0x1 << 15) |

Definition at line 229 of file i2c_common_v2.h.

◆ I2C_OAR1_OA1MODE

| #define I2C_OAR1_OA1MODE (1 << 10) |

Definition at line 232 of file i2c_common_v2.h.

◆ I2C_OAR1_OA1MODE_10BIT

| #define I2C_OAR1_OA1MODE_10BIT 1 |

Definition at line 234 of file i2c_common_v2.h.

◆ I2C_OAR1_OA1MODE_7BIT

| #define I2C_OAR1_OA1MODE_7BIT 0 |

Definition at line 233 of file i2c_common_v2.h.

◆ I2C_OAR2

| #define I2C_OAR2 | ( | i2c_base | ) | MMIO32((i2c_base) + 0x0c) |

Definition at line 72 of file i2c_common_v2.h.

◆ I2C_OAR2_OA2EN

| #define I2C_OAR2_OA2EN (1 << 15) |

Definition at line 248 of file i2c_common_v2.h.

◆ I2C_OAR2_OA2MSK_NO_CMP

| #define I2C_OAR2_OA2MSK_NO_CMP (0x7 << 8) |

Definition at line 258 of file i2c_common_v2.h.

◆ I2C_OAR2_OA2MSK_NO_MASK

| #define I2C_OAR2_OA2MSK_NO_MASK (0x0 << 8) |

Definition at line 251 of file i2c_common_v2.h.

◆ I2C_OAR2_OA2MSK_OA2_7

| #define I2C_OAR2_OA2MSK_OA2_7 (0x6 << 8) |

Definition at line 257 of file i2c_common_v2.h.

◆ I2C_OAR2_OA2MSK_OA2_7_OA2_2

| #define I2C_OAR2_OA2MSK_OA2_7_OA2_2 (0x1 << 8) |

Definition at line 252 of file i2c_common_v2.h.

◆ I2C_OAR2_OA2MSK_OA2_7_OA2_3

| #define I2C_OAR2_OA2MSK_OA2_7_OA2_3 (0x2 << 8) |

Definition at line 253 of file i2c_common_v2.h.

◆ I2C_OAR2_OA2MSK_OA2_7_OA2_4

| #define I2C_OAR2_OA2MSK_OA2_7_OA2_4 (0x3 << 8) |

Definition at line 254 of file i2c_common_v2.h.

◆ I2C_OAR2_OA2MSK_OA2_7_OA2_5

| #define I2C_OAR2_OA2MSK_OA2_7_OA2_5 (0x4 << 8) |

Definition at line 255 of file i2c_common_v2.h.

◆ I2C_OAR2_OA2MSK_OA2_7_OA2_6

| #define I2C_OAR2_OA2MSK_OA2_7_OA2_6 (0x5 << 8) |

Definition at line 256 of file i2c_common_v2.h.

◆ I2C_PECR

| #define I2C_PECR | ( | i2c_base | ) | MMIO32((i2c_base) + 0x20) |

Definition at line 97 of file i2c_common_v2.h.

◆ I2C_RXDR

| #define I2C_RXDR | ( | i2c_base | ) | MMIO32((i2c_base) + 0x24) |

Definition at line 102 of file i2c_common_v2.h.

◆ I2C_TIEMOUTR_TEXTEN

| #define I2C_TIEMOUTR_TEXTEN (1 << 31) |

Definition at line 287 of file i2c_common_v2.h.

◆ I2C_TIEMOUTR_TIDLE_SCL_LOW

| #define I2C_TIEMOUTR_TIDLE_SCL_LOW (0x0 << 12) |

Definition at line 296 of file i2c_common_v2.h.

◆ I2C_TIEMOUTR_TIDLE_SCL_SDA_HIGH

| #define I2C_TIEMOUTR_TIDLE_SCL_SDA_HIGH (0x1 << 12) |

Definition at line 297 of file i2c_common_v2.h.

◆ I2C_TIEMOUTR_TIMOUTEN

| #define I2C_TIEMOUTR_TIMOUTEN (1 << 15) |

Definition at line 293 of file i2c_common_v2.h.

◆ I2C_TIMEOUTR

| #define I2C_TIMEOUTR | ( | i2c_base | ) | MMIO32((i2c_base) + 0x14) |

Definition at line 82 of file i2c_common_v2.h.

◆ I2C_TIMINGR

| #define I2C_TIMINGR | ( | i2c_base | ) | MMIO32((i2c_base) + 0x10) |

Definition at line 77 of file i2c_common_v2.h.

◆ I2C_TIMINGR_PRESC_MASK

| #define I2C_TIMINGR_PRESC_MASK (0xF << 28) |

Definition at line 266 of file i2c_common_v2.h.

◆ I2C_TIMINGR_PRESC_SHIFT

| #define I2C_TIMINGR_PRESC_SHIFT 28 |

Definition at line 265 of file i2c_common_v2.h.

◆ I2C_TIMINGR_SCLDEL_MASK

| #define I2C_TIMINGR_SCLDEL_MASK (0xF << I2C_TIMINGR_SCLDEL_SHIFT) |

Definition at line 270 of file i2c_common_v2.h.

◆ I2C_TIMINGR_SCLDEL_SHIFT

| #define I2C_TIMINGR_SCLDEL_SHIFT 20 |

Definition at line 269 of file i2c_common_v2.h.

◆ I2C_TIMINGR_SCLH_MASK

| #define I2C_TIMINGR_SCLH_MASK (0xFF << I2C_TIMINGR_SCLH_SHIFT) |

Definition at line 278 of file i2c_common_v2.h.

◆ I2C_TIMINGR_SCLH_SHIFT

| #define I2C_TIMINGR_SCLH_SHIFT 8 |

Definition at line 277 of file i2c_common_v2.h.

◆ I2C_TIMINGR_SCLL_MASK

| #define I2C_TIMINGR_SCLL_MASK (0xFF << I2C_TIMINGR_SCLL_SHIFT) |

Definition at line 282 of file i2c_common_v2.h.

◆ I2C_TIMINGR_SCLL_SHIFT

| #define I2C_TIMINGR_SCLL_SHIFT 0 |

Definition at line 281 of file i2c_common_v2.h.

◆ I2C_TIMINGR_SDADEL_MASK

| #define I2C_TIMINGR_SDADEL_MASK (0xF << I2C_TIMINGR_SDADEL_SHIFT) |

Definition at line 274 of file i2c_common_v2.h.

◆ I2C_TIMINGR_SDADEL_SHIFT

| #define I2C_TIMINGR_SDADEL_SHIFT 16 |

Definition at line 273 of file i2c_common_v2.h.

◆ I2C_TXDR

| #define I2C_TXDR | ( | i2c_base | ) | MMIO32((i2c_base) + 0x28) |

Definition at line 107 of file i2c_common_v2.h.

Enumeration Type Documentation

◆ i2c_speeds

| enum i2c_speeds |

I2C speed modes.

| Enumerator | |

|---|---|

| i2c_speed_sm_100k | |

| i2c_speed_fm_400k | |

| i2c_speed_fmp_1m | |

| i2c_speed_unknown | |

Definition at line 396 of file i2c_common_v2.h.

Function Documentation

◆ i2c_busy()

| bool i2c_busy | ( | uint32_t | i2c | ) |

Definition at line 268 of file i2c_common_v2.c.

References I2C_ISR, and I2C_ISR_BUSY.

◆ i2c_clear_stop()

| void i2c_clear_stop | ( | uint32_t | i2c | ) |

I2C Clear Stop Flag.

Clear the "Send Stop" flag in the I2C config register

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address.

Definition at line 89 of file i2c_common_v2.c.

References I2C_ICR, and I2C_ICR_STOPCF.

◆ i2c_disable_analog_filter()

| void i2c_disable_analog_filter | ( | uint32_t | i2c | ) |

Definition at line 150 of file i2c_common_v2.c.

References I2C_CR1, and I2C_CR1_ANFOFF.

◆ i2c_disable_autoend()

| void i2c_disable_autoend | ( | uint32_t | i2c | ) |

Definition at line 258 of file i2c_common_v2.c.

References I2C_CR2.

Referenced by i2c_transfer7().

◆ i2c_disable_interrupt()

| void i2c_disable_interrupt | ( | uint32_t | i2c, |

| uint32_t | interrupt | ||

| ) |

I2C Disable Interrupt.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address. [in] interrupt Unsigned int32. Interrupt to disable.

Definition at line 306 of file i2c_common_v2.c.

References I2C_CR1.

◆ i2c_disable_rxdma()

| void i2c_disable_rxdma | ( | uint32_t | i2c | ) |

I2C Disable reception DMA.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address.

Definition at line 326 of file i2c_common_v2.c.

References I2C_CR1.

◆ i2c_disable_stretching()

| void i2c_disable_stretching | ( | uint32_t | i2c | ) |

Definition at line 205 of file i2c_common_v2.c.

References I2C_CR1, and I2C_CR1_NOSTRETCH.

◆ i2c_disable_txdma()

| void i2c_disable_txdma | ( | uint32_t | i2c | ) |

I2C Disable transmission DMA.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address.

Definition at line 346 of file i2c_common_v2.c.

References I2C_CR1.

◆ i2c_enable_analog_filter()

| void i2c_enable_analog_filter | ( | uint32_t | i2c | ) |

Definition at line 145 of file i2c_common_v2.c.

References I2C_CR1.

◆ i2c_enable_autoend()

| void i2c_enable_autoend | ( | uint32_t | i2c | ) |

Definition at line 253 of file i2c_common_v2.c.

References I2C_CR2, and I2C_CR2_AUTOEND.

Referenced by i2c_transfer7().

◆ i2c_enable_interrupt()

| void i2c_enable_interrupt | ( | uint32_t | i2c, |

| uint32_t | interrupt | ||

| ) |

I2C Enable Interrupt.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address. [in] interrupt Unsigned int32. Interrupt to enable.

Definition at line 295 of file i2c_common_v2.c.

References I2C_CR1.

◆ i2c_enable_rxdma()

| void i2c_enable_rxdma | ( | uint32_t | i2c | ) |

I2C Enable reception DMA.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address.

Definition at line 316 of file i2c_common_v2.c.

References I2C_CR1, and I2C_CR1_RXDMAEN.

◆ i2c_enable_stretching()

| void i2c_enable_stretching | ( | uint32_t | i2c | ) |

Definition at line 200 of file i2c_common_v2.c.

References I2C_CR1.

◆ i2c_enable_txdma()

| void i2c_enable_txdma | ( | uint32_t | i2c | ) |

I2C Enable transmission DMA.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address.

Definition at line 336 of file i2c_common_v2.c.

References I2C_CR1, and I2C_CR1_TXDMAEN.

◆ i2c_get_data()

| uint8_t i2c_get_data | ( | uint32_t | i2c | ) |

I2C Get Data.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address.

Definition at line 140 of file i2c_common_v2.c.

References I2C_RXDR.

Referenced by i2c_transfer7().

◆ i2c_is_start()

| bool i2c_is_start | ( | uint32_t | i2c | ) |

Definition at line 248 of file i2c_common_v2.c.

References I2C_CR2, and I2C_CR2_START.

◆ i2c_nack()

| bool i2c_nack | ( | uint32_t | i2c | ) |

Definition at line 263 of file i2c_common_v2.c.

References I2C_ISR, and I2C_ISR_NACKF.

Referenced by i2c_transfer7().

◆ i2c_peripheral_disable()

| void i2c_peripheral_disable | ( | uint32_t | i2c | ) |

I2C Peripheral Disable.

This must not be reset while in Master mode until a communication has finished. In Slave mode, the peripheral is disabled only after communication has ended.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address.

Definition at line 48 of file i2c_common_v2.c.

References I2C_CR1.

◆ i2c_peripheral_enable()

| void i2c_peripheral_enable | ( | uint32_t | i2c | ) |

I2C Peripheral Enable.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address.

Definition at line 33 of file i2c_common_v2.c.

References I2C_CR1, and I2C_CR1_PE.

◆ i2c_received_data()

| bool i2c_received_data | ( | uint32_t | i2c | ) |

Definition at line 283 of file i2c_common_v2.c.

References I2C_ISR, and I2C_ISR_RXNE.

Referenced by i2c_transfer7().

◆ i2c_send_data()

| void i2c_send_data | ( | uint32_t | i2c, |

| uint8_t | data | ||

| ) |

I2C Send Data.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address. [in] data Unsigned int8. Byte to send.

Definition at line 130 of file i2c_common_v2.c.

References I2C_TXDR.

Referenced by i2c_transfer7().

◆ i2c_send_start()

| void i2c_send_start | ( | uint32_t | i2c | ) |

I2C Send Start Condition.

If in Master mode this will cause a restart condition to occur at the end of the current transmission. If in Slave mode, this will initiate a start condition when the current bus activity is completed.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address.

Definition at line 63 of file i2c_common_v2.c.

References I2C_CR2, and I2C_CR2_START.

Referenced by i2c_transfer7().

◆ i2c_send_stop()

| void i2c_send_stop | ( | uint32_t | i2c | ) |

I2C Send Stop Condition.

After the current byte transfer this will initiate a stop condition if in Master mode, or simply release the bus if in Slave mode.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address.

Definition at line 77 of file i2c_common_v2.c.

References I2C_CR2, and I2C_CR2_STOP.

◆ i2c_set_10bit_addr_mode()

| void i2c_set_10bit_addr_mode | ( | uint32_t | i2c | ) |

Definition at line 215 of file i2c_common_v2.c.

References I2C_CR2, and I2C_CR2_ADD10.

◆ i2c_set_10bit_address()

| void i2c_set_10bit_address | ( | uint32_t | i2c, |

| uint16_t | addr | ||

| ) |

Definition at line 226 of file i2c_common_v2.c.

References I2C_CR2, and I2C_CR2_SADD_10BIT_SHIFT.

◆ i2c_set_7bit_addr_mode()

| void i2c_set_7bit_addr_mode | ( | uint32_t | i2c | ) |

Definition at line 210 of file i2c_common_v2.c.

References I2C_CR2.

◆ i2c_set_7bit_address()

| void i2c_set_7bit_address | ( | uint32_t | i2c, |

| uint8_t | addr | ||

| ) |

Definition at line 220 of file i2c_common_v2.c.

References I2C_CR2, and I2C_CR2_SADD_7BIT_SHIFT.

Referenced by i2c_transfer7().

◆ i2c_set_bytes_to_transfer()

| void i2c_set_bytes_to_transfer | ( | uint32_t | i2c, |

| uint32_t | n_bytes | ||

| ) |

Definition at line 242 of file i2c_common_v2.c.

References I2C_CR2, and I2C_CR2_NBYTES_SHIFT.

Referenced by i2c_transfer7().

◆ i2c_set_data_hold_time()

| void i2c_set_data_hold_time | ( | uint32_t | i2c, |

| uint8_t | h_time | ||

| ) |

Definition at line 182 of file i2c_common_v2.c.

References I2C_TIMINGR, and I2C_TIMINGR_SDADEL_SHIFT.

Referenced by i2c_set_speed().

◆ i2c_set_data_setup_time()

| void i2c_set_data_setup_time | ( | uint32_t | i2c, |

| uint8_t | s_time | ||

| ) |

Definition at line 176 of file i2c_common_v2.c.

References I2C_TIMINGR, and I2C_TIMINGR_SCLDEL_SHIFT.

Referenced by i2c_set_speed().

◆ i2c_set_digital_filter()

| void i2c_set_digital_filter | ( | uint32_t | i2c, |

| uint8_t | dnf_setting | ||

| ) |

Set the I2C digital filter.

These bits are used to configure the digital noise filter on SDA and SCL input. The digital filter will filter spikes with a length of up to dnf_setting * I2CCLK clocks

- Parameters

-

i2c peripheral of interest dnf_setting 0 to disable, else 1..15 i2c clocks

Definition at line 163 of file i2c_common_v2.c.

References I2C_CR1, I2C_CR1_DNF_MASK, and I2C_CR1_DNF_SHIFT.

◆ i2c_set_own_10bit_slave_address()

| void i2c_set_own_10bit_slave_address | ( | uint32_t | i2c, |

| uint16_t | slave | ||

| ) |

I2C Set the 10 bit Slave Address for the Peripheral.

This sets an address for Slave mode operation, in 10 bit form.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address. [in] slave Unsigned int16. Slave address 0...1023.

Definition at line 118 of file i2c_common_v2.c.

References I2C_OAR1, and I2C_OAR1_OA1MODE.

◆ i2c_set_own_7bit_slave_address()

| void i2c_set_own_7bit_slave_address | ( | uint32_t | i2c, |

| uint8_t | slave | ||

| ) |

I2C Set the 7 bit Slave Address for the Peripheral.

This sets an address for Slave mode operation, in 7 bit form.

- Parameters

-

[in] i2c Unsigned int32. I2C register base address I2C register base address. [in] slave Unsigned int8. Slave address 0...127.

Definition at line 103 of file i2c_common_v2.c.

References I2C_OAR1.

◆ i2c_set_prescaler()

| void i2c_set_prescaler | ( | uint32_t | i2c, |

| uint8_t | presc | ||

| ) |

Definition at line 170 of file i2c_common_v2.c.

References I2C_TIMINGR, and I2C_TIMINGR_PRESC_SHIFT.

Referenced by i2c_set_speed().

◆ i2c_set_read_transfer_dir()

| void i2c_set_read_transfer_dir | ( | uint32_t | i2c | ) |

Definition at line 237 of file i2c_common_v2.c.

References I2C_CR2, and I2C_CR2_RD_WRN.

Referenced by i2c_transfer7().

◆ i2c_set_scl_high_period()

| void i2c_set_scl_high_period | ( | uint32_t | i2c, |

| uint8_t | period | ||

| ) |

Definition at line 188 of file i2c_common_v2.c.

References I2C_TIMINGR, and I2C_TIMINGR_SCLH_SHIFT.

Referenced by i2c_set_speed().

◆ i2c_set_scl_low_period()

| void i2c_set_scl_low_period | ( | uint32_t | i2c, |

| uint8_t | period | ||

| ) |

Definition at line 194 of file i2c_common_v2.c.

References I2C_TIMINGR, and I2C_TIMINGR_SCLL_SHIFT.

Referenced by i2c_set_speed().

◆ i2c_set_speed()

| void i2c_set_speed | ( | uint32_t | i2c, |

| enum i2c_speeds | speed, | ||

| uint32_t | clock_megahz | ||

| ) |

Set the i2c communication speed.

NOTE: 1MHz mode not yet implemented! Min clock speed: 8MHz for FM, 2Mhz for SM,

- Parameters

-

i2c peripheral, eg I2C1 speed one of the listed speed modes i2c_speeds clock_megahz i2c peripheral clock speed in MHz. Usually, rcc_apb1_frequency / 1e6

Definition at line 420 of file i2c_common_v2.c.

References i2c_set_data_hold_time(), i2c_set_data_setup_time(), i2c_set_prescaler(), i2c_set_scl_high_period(), i2c_set_scl_low_period(), i2c_speed_fm_400k, i2c_speed_fmp_1m, and i2c_speed_sm_100k.

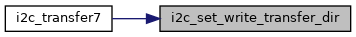

◆ i2c_set_write_transfer_dir()

| void i2c_set_write_transfer_dir | ( | uint32_t | i2c | ) |

Definition at line 232 of file i2c_common_v2.c.

References I2C_CR2.

Referenced by i2c_transfer7().

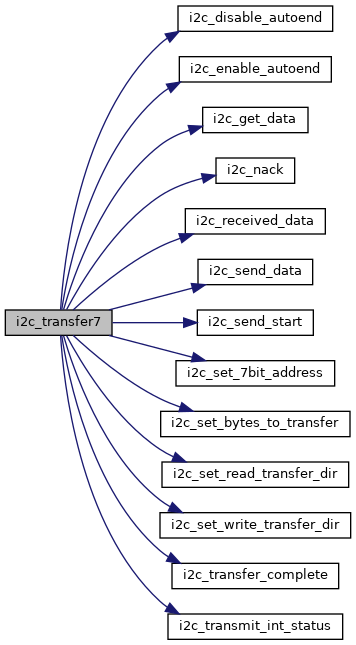

◆ i2c_transfer7()

| void i2c_transfer7 | ( | uint32_t | i2c, |

| uint8_t | addr, | ||

| const uint8_t * | w, | ||

| size_t | wn, | ||

| uint8_t * | r, | ||

| size_t | rn | ||

| ) |

Run a write/read transaction to a given 7bit i2c address If both write & read are provided, the read will use repeated start.

Both write and read are optional

- Parameters

-

i2c peripheral of choice, eg I2C1 addr 7 bit i2c device address w buffer of data to write wn length of w r destination buffer to read into rn number of bytes to read (r should be at least this long)

Definition at line 362 of file i2c_common_v2.c.

References i2c_disable_autoend(), i2c_enable_autoend(), i2c_get_data(), i2c_nack(), i2c_received_data(), i2c_send_data(), i2c_send_start(), i2c_set_7bit_address(), i2c_set_bytes_to_transfer(), i2c_set_read_transfer_dir(), i2c_set_write_transfer_dir(), i2c_transfer_complete(), and i2c_transmit_int_status().

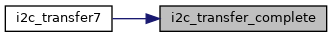

◆ i2c_transfer_complete()

| bool i2c_transfer_complete | ( | uint32_t | i2c | ) |

Definition at line 278 of file i2c_common_v2.c.

References I2C_ISR, and I2C_ISR_TC.

Referenced by i2c_transfer7().

◆ i2c_transmit_int_status()

| bool i2c_transmit_int_status | ( | uint32_t | i2c | ) |

Definition at line 273 of file i2c_common_v2.c.

References I2C_ISR, and I2C_ISR_TXIS.

Referenced by i2c_transfer7().