Functions | |

| void | pwr_set_mode_ldo (void) |

| Set power subsystem to utilize the LDO for CPU. More... | |

| void | pwr_set_mode_scu_ldo (void) |

| Specific STM32H742/43/50/53 LDO mode setting. More... | |

| void | pwr_set_mode_smps_ldo (bool supply_external, uint32_t smps_level, bool use_ldo) |

| Set power subsystem to utilize the SMPS run through the LDO for CPU. More... | |

| void | pwr_set_mode (enum pwr_sys_mode mode, uint8_t smps_level) |

| Set power system based on "System Supply Configurations" table in reference manual. More... | |

| void | pwr_set_mode_bypass (void) |

| Set power subsystem to bypass all internal supplies. More... | |

| void | pwr_set_mode_scu_bypass (void) |

| Specific STM32H742/43/50/53 Bypsass mode setting. More... | |

| void | pwr_set_svos_scale (enum pwr_svos_scale scale) |

| Set the voltage scaling/strength for the internal SMPS/LDO when in Stop mode. More... | |

| void | pwr_set_vos_scale (enum pwr_vos_scale scale) |

| Set the voltage scaling/strength for the internal SMPS/LDO while running. More... | |

Detailed Description

Function Documentation

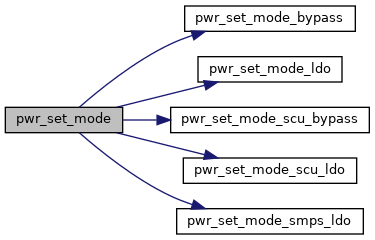

◆ pwr_set_mode()

| void pwr_set_mode | ( | enum pwr_sys_mode | mode, |

| uint8_t | smps_level | ||

| ) |

Set power system based on "System Supply Configurations" table in reference manual.

- Parameters

-

[in] mode Mode mapping to a mode in the system configuration. Note special SCU modes. [in] smps_level Optional, only needed if using an EXT_SMPS or SMPS_LDO mode. Provide zero if unused, otherwise SMPS step-down converter voltage output level selection.

Definition at line 83 of file pwr.c.

References PWR_CR3_SMPSLEVEL_VOS, PWR_CSR1, PWR_CSR1_ACTVOSRDY, pwr_set_mode_bypass(), pwr_set_mode_ldo(), pwr_set_mode_scu_bypass(), pwr_set_mode_scu_ldo(), pwr_set_mode_smps_ldo(), PWR_SYS_BYPASS, PWR_SYS_EXT_SMPS_LDO, PWR_SYS_EXT_SMPS_LDO_BYP, PWR_SYS_LDO, PWR_SYS_SCU_BYPASS, PWR_SYS_SCU_LDO, PWR_SYS_SMPS_DIRECT, and PWR_SYS_SMPS_LDO.

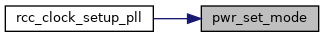

Referenced by rcc_clock_setup_pll().

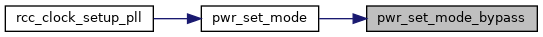

◆ pwr_set_mode_bypass()

| void pwr_set_mode_bypass | ( | void | ) |

Set power subsystem to bypass all internal supplies.

Definition at line 72 of file pwr.c.

References PWR_CR3, PWR_CR3_BYPASS, PWR_CR3_LDOEN, and PWR_CR3_SMPSEN.

Referenced by pwr_set_mode().

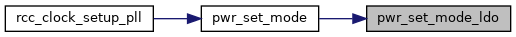

◆ pwr_set_mode_ldo()

| void pwr_set_mode_ldo | ( | void | ) |

Set power subsystem to utilize the LDO for CPU.

Definition at line 43 of file pwr.c.

References PWR_CR3, PWR_CR3_BYPASS, PWR_CR3_LDOEN, and PWR_CR3_SMPSEN.

Referenced by pwr_set_mode().

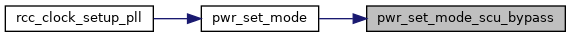

◆ pwr_set_mode_scu_bypass()

| void pwr_set_mode_scu_bypass | ( | void | ) |

Specific STM32H742/43/50/53 Bypsass mode setting.

Definition at line 77 of file pwr.c.

References PWR_CR3, PWR_CR3_BYPASS, PWR_CR3_LDOEN, and PWR_CR3_SCUEN.

Referenced by pwr_set_mode().

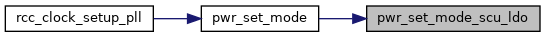

◆ pwr_set_mode_scu_ldo()

| void pwr_set_mode_scu_ldo | ( | void | ) |

Specific STM32H742/43/50/53 LDO mode setting.

Definition at line 49 of file pwr.c.

References PWR_CR3, PWR_CR3_BYPASS, PWR_CR3_LDOEN, and PWR_CR3_SCUEN.

Referenced by pwr_set_mode().

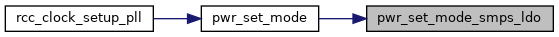

◆ pwr_set_mode_smps_ldo()

| void pwr_set_mode_smps_ldo | ( | bool | supply_external, |

| uint32_t | smps_level, | ||

| bool | use_ldo | ||

| ) |

Set power subsystem to utilize the SMPS run through the LDO for CPU.

- Parameters

-

[in] supply_external Supply is powering external circuits, enable high power mode. [in] smps_level Voltage level from SMPS step-down converter voltage output level selection (1.8V/2.5V) [in] use_ldo Set this value to true if the internal LDO should be enabled.

Definition at line 54 of file pwr.c.

References cm3_assert, PWR_CR3, PWR_CR3_BYPASS, PWR_CR3_LDOEN, PWR_CR3_SMPSEN, PWR_CR3_SMPSEXTHP, PWR_CR3_SMPSLEVEL_MASK, PWR_CR3_SMPSLEVEL_SHIFT, and PWR_CR3_SMPSLEVEL_VOS.

Referenced by pwr_set_mode().

◆ pwr_set_svos_scale()

| void pwr_set_svos_scale | ( | enum pwr_svos_scale | scale | ) |

Set the voltage scaling/strength for the internal SMPS/LDO when in Stop mode.

- Parameters

-

[in] scale Voltage scale value to set.

Definition at line 110 of file pwr.c.

References PWR_CR1, PWR_CR1_SVOS_MASK, and PWR_CR1_SVOS_SHIFT.

◆ pwr_set_vos_scale()

| void pwr_set_vos_scale | ( | enum pwr_vos_scale | scale | ) |

Set the voltage scaling/strength for the internal SMPS/LDO while running.

- Parameters

-

[in] scale Voltage scale value to set.

Definition at line 117 of file pwr.c.

References cm3_assert, DBGMCU_IDCODE, DBGMCU_IDCODE_DEV_ID_MASK, DBGMCU_IDCODE_DEV_ID_STM32H74X_5X, DBGMCU_IDCODE_DEV_ID_STM32H7A3_B3_B0, PWR_D3CR, PWR_D3CR_VOS_MASK, PWR_D3CR_VOS_SCALE_0, PWR_D3CR_VOS_SCALE_1, PWR_D3CR_VOS_SCALE_2, PWR_D3CR_VOS_SCALE_3, PWR_D3CR_VOS_SHIFT, PWR_D3CR_VOSRDY, PWR_SRDCR, PWR_SRDCR_VOS_MASK, PWR_SRDCR_VOS_SCALE_0, PWR_SRDCR_VOS_SCALE_1, PWR_SRDCR_VOS_SCALE_2, PWR_SRDCR_VOS_SCALE_3, PWR_SRDCR_VOS_SHIFT, PWR_VOS_SCALE_0, PWR_VOS_SCALE_UNDEFINED, rcc_periph_clock_enable(), RCC_SYSCFG, SYSCFG_PWRCR, and SYSCFG_PWRCR_ODEN.

Referenced by rcc_clock_setup_pll().