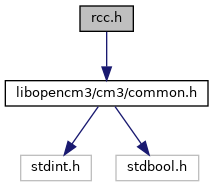

#include <libopencm3/cm3/common.h>

Include dependency graph for rcc.h:

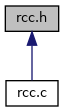

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Macros | |

| #define | RCC_RIS MMIO32(0x400FE050) |

| #define | RCC_CR MMIO32(0x400FE060) |

| #define | RCC2_CR MMIO32(0x400FE070) |

| #define | RCC_SYSDIV_MASK (0x0F << 23) |

| #define | RCC_SYSDIV_12_5MHZ (0x0F << 23) |

| #define | RCC_SYSDIV_50MHZ (0x03 << 23) |

| #define | RCC_USESYSDIV (1 << 22) |

| #define | RCC_USEPWMDIV (1 << 20) |

| #define | RCC_PWMDIV_MASK (0x07 << 17) |

| #define | RCC_PWMDIV_64 (0x07 << 17) |

| #define | RCC_OFF (1 << 13) |

| #define | RCC_BYPASS (1 << 11) |

| #define | RCC_XTAL_MASK (0x0F << 6) |

| #define | RCC_XTAL_6MHZ_RESET (0x0B << 6) |

| #define | RCC_XTAL_8MHZ_400MHZ (0x0D << 6) |

| #define | RCC_OSCRC_MASK (0x03 << 4) |

| #define | RCC_OSCRC_MOSC (0x00 << 4) |

| #define | RCC_OSCRC_IOSC (0x01 << 4) |

| #define | RCC_OSCRC_IOSC_Q (0x02 << 4) |

| #define | RCC_OSCRC_30KHZ (0x03 << 4) |

| #define | RCC_IOSCDIS (1 << 1) |

| #define | RCC_MOSCDIS (1 << 0) |

| #define | RCC2_USERRCC2 (1 << 31) |

| #define | RCC2_SYSDIV2_MASK 0x7f |

| #define | RCC2_SYSDIV2_SHIFT 23 |

| #define | RCC2_OFF (1 << 13) |

| #define | RCC2_BYPASS (1 << 11) |

| #define | RIS_PLLLRIS (1 << 6) |

| #define | RCC_RESET_VALUE (0x078E3AD1) |

| #define | RCC2_RESET_VALUE (0x07802810) |

Functions | |

| int | rcc_clock_setup_in_xtal_8mhz_out_50mhz (void) |

Macro Definition Documentation

◆ RCC2_BYPASS

◆ RCC2_CR

◆ RCC2_OFF

◆ RCC2_RESET_VALUE

◆ RCC2_SYSDIV2_MASK

◆ RCC2_SYSDIV2_SHIFT

◆ RCC2_USERRCC2

◆ RCC_BYPASS

◆ RCC_CR

◆ RCC_IOSCDIS

◆ RCC_MOSCDIS

◆ RCC_OFF

◆ RCC_OSCRC_30KHZ

◆ RCC_OSCRC_IOSC

◆ RCC_OSCRC_IOSC_Q

◆ RCC_OSCRC_MASK

◆ RCC_OSCRC_MOSC

◆ RCC_PWMDIV_64

◆ RCC_PWMDIV_MASK

◆ RCC_RESET_VALUE

◆ RCC_RIS

◆ RCC_SYSDIV_12_5MHZ

◆ RCC_SYSDIV_50MHZ

◆ RCC_SYSDIV_MASK

◆ RCC_USEPWMDIV

◆ RCC_USESYSDIV

◆ RCC_XTAL_6MHZ_RESET

◆ RCC_XTAL_8MHZ_400MHZ

◆ RCC_XTAL_MASK

◆ RIS_PLLLRIS

Function Documentation

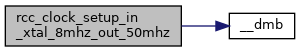

◆ rcc_clock_setup_in_xtal_8mhz_out_50mhz()

| int rcc_clock_setup_in_xtal_8mhz_out_50mhz | ( | void | ) |

Definition at line 39 of file rcc.c.

References __dmb(), RCC2_CR, RCC2_RESET_VALUE, RCC2_SYSDIV2_SHIFT, RCC_BYPASS, RCC_CR, RCC_PWMDIV_64, RCC_RESET_VALUE, RCC_RIS, RCC_SYSDIV_50MHZ, RCC_USEPWMDIV, RCC_USESYSDIV, RCC_XTAL_8MHZ_400MHZ, and RIS_PLLLRIS.

Here is the call graph for this function: