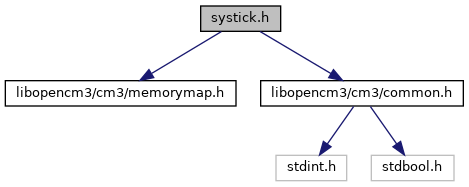

Include dependency graph for systick.h:

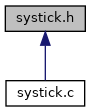

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Macros | |

| #define | STK_CSR MMIO32(SYS_TICK_BASE + 0x00) |

| SysTick Control and Status Register (CSR). More... | |

| #define | STK_RVR MMIO32(SYS_TICK_BASE + 0x04) |

| SysTick Reload Value Register (RVR). More... | |

| #define | STK_CVR MMIO32(SYS_TICK_BASE + 0x08) |

| SysTick Current Value Register (CVR). More... | |

| #define | STK_CALIB MMIO32(SYS_TICK_BASE + 0x0C) |

| SysTick Calibration Value Register(Read Only) (CALIB) Reads the calibration value and parameters for SysTick. More... | |

| #define | STK_CSR_COUNTFLAG (1 << 16) |

| COUNTFLAG Indicates whether the counter has counted to 0 since the last read of this register: 0 = Timer has not counted to 0 1 = Timer has counted to 0. More... | |

| #define | STK_CSR_CLKSOURCE_LSB 2 |

| #define | STK_CSR_CLKSOURCE (1 << STK_CSR_CLKSOURCE_LSB) |

| CLKSOURCE: Clock source selection for 0, SysTick uses the IMPLEMENTATION DEFINED external reference clock. More... | |

| #define | STK_CSR_CLKSOURCE_AHB_DIV8 (0 << STK_CSR_CLKSOURCE_LSB) |

| #define | STK_CSR_CLKSOURCE_AHB (1 << STK_CSR_CLKSOURCE_LSB) |

| #define | STK_CSR_TICKINT (1 << 1) |

| TICKINT: SysTick exception request enable. More... | |

| #define | STK_CSR_ENABLE (1 << 0) |

| ENABLE: Counter enable. More... | |

| #define | STK_RVR_RELOAD 0x00FFFFFF |

| RELOAD[23:0]: RELOAD value. More... | |

| #define | STK_CVR_CURRENT 0x00FFFFFF |

| CURRENT[23:0]: Current counter value. More... | |

| #define | STK_CALIB_NOREF (1 << 31) |

| NOREF: NOREF flag Bit31 => NOREF Indicates whether the IMPLEMENTATION DEFINED reference clock is implemented: 0 = The reference clock is implemented. More... | |

| #define | STK_CALIB_SKEW (1 << 30) |

| SKEW: SKEW flag Bit30 => SKEW Indicates whether the 10ms calibration value is exact: 0 = 10ms calibration value is exact. More... | |

| #define | STK_CALIB_TENMS 0x00FFFFFF |

| TENMS Calibration value for 10ms. More... | |

Functions | |

| void | systick_set_reload (uint32_t value) |

| SysTick Set the Automatic Reload Value. More... | |

| bool | systick_set_frequency (uint32_t freq, uint32_t ahb) |

| SysTick Set clock and frequency of overflow. More... | |

| uint32_t | systick_get_reload (void) |

| SysTick Read the Automatic Reload Value. More... | |

| uint32_t | systick_get_value (void) |

| Get the current SysTick counter value. More... | |

| void | systick_set_clocksource (uint8_t clocksource) |

| Set the SysTick Clock Source. More... | |

| void | systick_interrupt_enable (void) |

| Enable SysTick Interrupt. More... | |

| void | systick_interrupt_disable (void) |

| Disable SysTick Interrupt. More... | |

| void | systick_counter_enable (void) |

| Enable SysTick Counter. More... | |

| void | systick_counter_disable (void) |

| Disable SysTick Counter. More... | |

| uint8_t | systick_get_countflag (void) |

| SysTick Read the Counter Flag. More... | |

| void | systick_clear (void) |

| SysTick Clear counter Value. More... | |

| uint32_t | systick_get_calib (void) |

| SysTick Get Calibration Value. More... | |