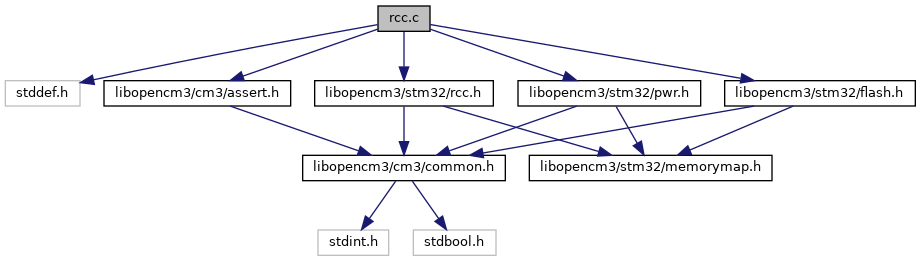

#include <stddef.h>#include <libopencm3/cm3/assert.h>#include <libopencm3/stm32/rcc.h>#include <libopencm3/stm32/pwr.h>#include <libopencm3/stm32/flash.h>

Go to the source code of this file.

Macros | |

| #define | HZ_PER_MHZ 1000000UL |

| #define | HZ_PER_KHZ 1000UL |

Functions | |

| static void | rcc_configure_pll (uint32_t clkin, const struct pll_config *config, int pll_num) |

| static void | rcc_set_and_enable_plls (const struct rcc_pll_config *config) |

| static uint16_t | rcc_prediv_log_skip32_div (uint16_t clk_mhz, uint32_t div_val) |

| static uint16_t | rcc_prediv_3bit_log_div (uint16_t clk_mhz, uint32_t div_val) |

| static void | rcc_clock_setup_domain1 (const struct rcc_pll_config *config) |

| static void | rcc_clock_setup_domain2 (const struct rcc_pll_config *config) |

| static void | rcc_clock_setup_domain3 (const struct rcc_pll_config *config) |

| void | rcc_clock_setup_pll (const struct rcc_pll_config *config) |

| Setup the base PLLs and clock domains for the STM32H7. More... | |

| uint32_t | rcc_get_bus_clk_freq (enum rcc_clock_source source) |

| Get the clock rate (in Hz) of the specified clock source. More... | |

| uint32_t | rcc_get_usart_clk_freq (uint32_t usart) |

| Get the peripheral clock speed for the USART at base specified. More... | |

| uint32_t | rcc_get_timer_clk_freq (uint32_t timer) |

| Get the peripheral clock speed for the Timer at base specified. More... | |

| uint32_t | rcc_get_i2c_clk_freq (uint32_t i2c) |

| Get the peripheral clock speed for the I2C device at base specified. More... | |

| uint32_t | rcc_get_spi_clk_freq (uint32_t spi) |

| Get the peripheral clock speed for the SPI device at base specified. More... | |

| uint32_t | rcc_get_fdcan_clk_freq (uint32_t fdcan) |

| Get the peripheral clock speed for the FDCAN device at base specified. More... | |

| void | rcc_set_peripheral_clk_sel (uint32_t periph, uint32_t sel) |

| Set the clksel value for the specified peripheral. More... | |

| void | rcc_set_fdcan_clksel (uint8_t clksel) |

| Set the clock select for the FDCAN devices. More... | |

| void | rcc_set_rng_clksel (uint8_t clksel) |

| Set the clock select for the RNG device. More... | |

| void | rcc_set_spi123_clksel (uint8_t clksel) |

| Set the clock select for the SPI 1/2/3 devices. More... | |

| void | rcc_set_spi45_clksel (uint8_t clksel) |

| Set the clock select for the SPI 4/5 devices. More... | |

Variables | |

| struct { | |

| uint16_t sysclk_mhz | |

| uint16_t cpu_mhz | |

| uint16_t hclk_mhz | |

| struct { | |

| uint16_t pclk1_mhz | |

| uint16_t pclk2_mhz | |

| uint16_t pclk3_mhz | |

| uint16_t pclk4_mhz | |

| } per | |

| struct pll_clocks { | |

| uint16_t p_mhz | |

| uint16_t q_mhz | |

| uint16_t r_mhz | |

| } pll1 | |

| struct pll_clocks { | |

| uint16_t p_mhz | |

| uint16_t q_mhz | |

| uint16_t r_mhz | |

| } pll2 | |

| struct pll_clocks { | |

| uint16_t p_mhz | |

| uint16_t q_mhz | |

| uint16_t r_mhz | |

| } pll3 | |

| uint16_t hse_khz | |

| } | rcc_clock_tree |

Macro Definition Documentation

◆ HZ_PER_KHZ

◆ HZ_PER_MHZ

Function Documentation

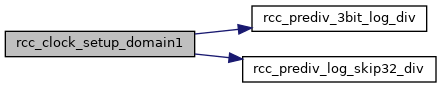

◆ rcc_clock_setup_domain1()

|

static |

Definition at line 146 of file rcc.c.

References rcc_pll_config::core_pre, rcc_pll_config::hpre, rcc_pll_config::ppre3, rcc_clock_tree, RCC_D1CFGR, RCC_D1CFGR_D1CPRE, RCC_D1CFGR_D1HPRE, RCC_D1CFGR_D1PPRE, rcc_prediv_3bit_log_div(), and rcc_prediv_log_skip32_div().

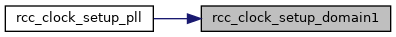

Referenced by rcc_clock_setup_pll().

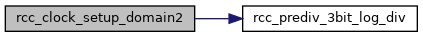

◆ rcc_clock_setup_domain2()

|

static |

Definition at line 160 of file rcc.c.

References rcc_pll_config::ppre1, rcc_pll_config::ppre2, rcc_clock_tree, RCC_D2CFGR, RCC_D2CFGR_D2PPRE1, RCC_D2CFGR_D2PPRE2, and rcc_prediv_3bit_log_div().

Referenced by rcc_clock_setup_pll().

◆ rcc_clock_setup_domain3()

|

static |

Definition at line 172 of file rcc.c.

References rcc_pll_config::ppre4, rcc_clock_tree, RCC_D3CFGR, RCC_D3CFGR_D3PPRE, and rcc_prediv_3bit_log_div().

Referenced by rcc_clock_setup_pll().

◆ rcc_configure_pll()

|

static |

Definition at line 45 of file rcc.c.

References HZ_PER_MHZ, rcc_clock_tree, RCC_CR, RCC_CR_PLL1ON, RCC_CR_PLL1RDY, RCC_PLLCFGR, RCC_PLLCFGR_DIVP1EN, RCC_PLLCFGR_DIVQ1EN, RCC_PLLCFGR_DIVR1EN, RCC_PLLCFGR_PLL1RGE_SHIFT, RCC_PLLCFGR_PLL1VCO_MED, RCC_PLLCFGR_PLLRGE_2_4MHZ, RCC_PLLCFGR_PLLRGE_4_8MHZ, RCC_PLLCFGR_PLLRGE_8_16MHZ, RCC_PLLDIVR, RCC_PLLNDIVR_DIVN, RCC_PLLNDIVR_DIVP, RCC_PLLNDIVR_DIVQ, and RCC_PLLNDIVR_DIVR.

Referenced by rcc_set_and_enable_plls().

◆ rcc_prediv_3bit_log_div()

|

static |

Definition at line 138 of file rcc.c.

Referenced by rcc_clock_setup_domain1(), rcc_clock_setup_domain2(), and rcc_clock_setup_domain3().

◆ rcc_prediv_log_skip32_div()

|

static |

Definition at line 126 of file rcc.c.

References RCC_D1CFGR_D1CPRE_DIV16.

Referenced by rcc_clock_setup_domain1().

◆ rcc_set_and_enable_plls()

|

static |

Definition at line 107 of file rcc.c.

References rcc_pll_config::pll_config::divm, rcc_pll_config::hse_frequency, rcc_pll_config::pll1, rcc_pll_config::pll2, rcc_pll_config::pll3, rcc_pll_config::pll_source, rcc_configure_pll(), RCC_HSI_BASE_FREQUENCY, RCC_PLLCFGR, RCC_PLLCKSELR, RCC_PLLCKSELR_DIVM1, RCC_PLLCKSELR_DIVM2, RCC_PLLCKSELR_DIVM3, and RCC_PLLCKSELR_PLLSRC_HSI.

Referenced by rcc_clock_setup_pll().

Variable Documentation

◆ cpu_mhz

◆ hclk_mhz

◆ hse_khz

◆ p_mhz

◆ pclk1_mhz

◆ pclk2_mhz

◆ pclk3_mhz

◆ pclk4_mhz

◆

| struct { ... } per |

◆

| struct { ... } ::pll_clocks pll1 |

◆

| struct { ... } ::pll_clocks pll2 |

◆

| struct { ... } ::pll_clocks pll3 |

◆ q_mhz

◆ r_mhz

◆

| struct { ... } rcc_clock_tree |

Referenced by rcc_clock_setup_domain1(), rcc_clock_setup_domain2(), rcc_clock_setup_domain3(), rcc_clock_setup_pll(), rcc_configure_pll(), rcc_get_bus_clk_freq(), rcc_get_fdcan_clk_freq(), rcc_get_i2c_clk_freq(), rcc_get_spi_clk_freq(), rcc_get_timer_clk_freq(), and rcc_get_usart_clk_freq().