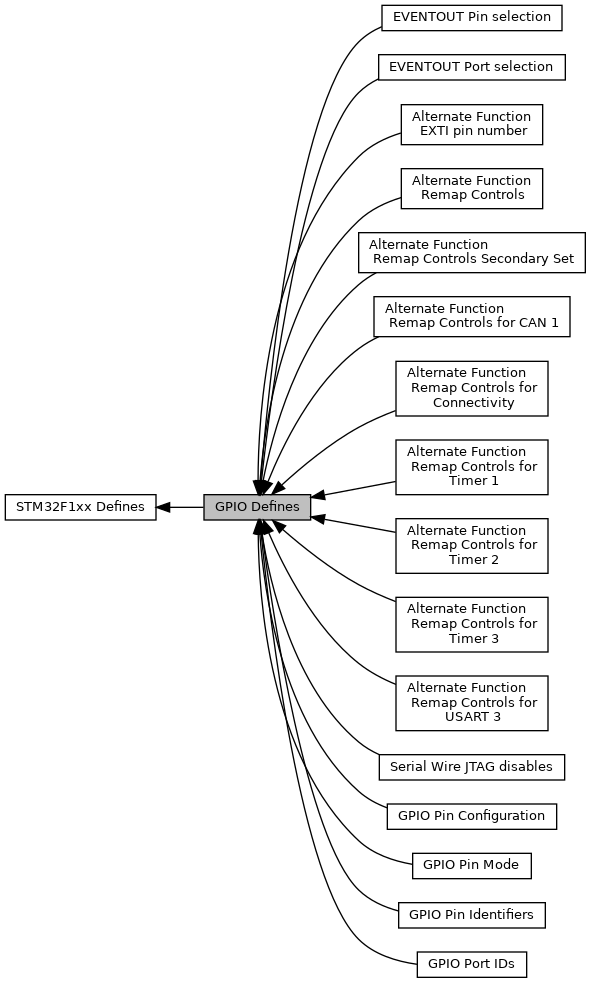

Defined Constants and Types for the STM32F1xx General Purpose I/O More...

Functions | |

| void | gpio_set_mode (uint32_t gpioport, uint8_t mode, uint8_t cnf, uint16_t gpios) |

| Set GPIO Pin Mode. More... | |

| void | gpio_set_eventout (uint8_t evoutport, uint8_t evoutpin) |

| Map the EVENTOUT signal. More... | |

| void | gpio_primary_remap (uint32_t swjenable, uint32_t maps) |

| Map Alternate Function Port Bits (Main Set) More... | |

| void | gpio_secondary_remap (uint32_t maps) |

| Map Alternate Function Port Bits (Secondary Set) More... | |

| void | gpio_set (uint32_t gpioport, uint16_t gpios) |

| Set a Group of Pins Atomic. More... | |

| void | gpio_clear (uint32_t gpioport, uint16_t gpios) |

| Clear a Group of Pins Atomic. More... | |

| uint16_t | gpio_get (uint32_t gpioport, uint16_t gpios) |

| Read a Group of Pins. More... | |

| void | gpio_toggle (uint32_t gpioport, uint16_t gpios) |

| Toggle a Group of Pins. More... | |

| uint16_t | gpio_port_read (uint32_t gpioport) |

| Read from a Port. More... | |

| void | gpio_port_write (uint32_t gpioport, uint16_t data) |

| Write to a Port. More... | |

| void | gpio_port_config_lock (uint32_t gpioport, uint16_t gpios) |

| Lock the Configuration of a Group of Pins. More... | |

Detailed Description

Defined Constants and Types for the STM32F1xx General Purpose I/O

- Version

- 1.0.0

- Date

- 1 July 2012

LGPL License Terms libopencm3 License

Macro Definition Documentation

◆ AFIO_EVCR

◆ AFIO_EVCR_EVOE

◆ AFIO_EXTICR

◆ AFIO_EXTICR1

| #define AFIO_EXTICR1 AFIO_EXTICR(0) |

◆ AFIO_EXTICR2

| #define AFIO_EXTICR2 AFIO_EXTICR(1) |

◆ AFIO_EXTICR3

| #define AFIO_EXTICR3 AFIO_EXTICR(2) |

◆ AFIO_EXTICR4

| #define AFIO_EXTICR4 AFIO_EXTICR(3) |

◆ AFIO_EXTICR_FIELDSIZE

| #define AFIO_EXTICR_FIELDSIZE 4 |

◆ AFIO_MAPR

◆ AFIO_MAPR2

◆ GPIO_BANK_CAN1_PB_RX

| #define GPIO_BANK_CAN1_PB_RX GPIO_BANK_CAN_PB_RX /* Alias */ |

◆ GPIO_BANK_CAN1_PB_TX

| #define GPIO_BANK_CAN1_PB_TX GPIO_BANK_CAN_PB_TX /* Alias */ |

◆ GPIO_BANK_CAN1_PD_RX

| #define GPIO_BANK_CAN1_PD_RX GPIO_BANK_CAN_PD_RX /* Alias */ |

◆ GPIO_BANK_CAN1_PD_TX

| #define GPIO_BANK_CAN1_PD_TX GPIO_BANK_CAN_PD_TX /* Alias */ |

◆ GPIO_BANK_CAN1_RX

◆ GPIO_BANK_CAN1_TX

◆ GPIO_BANK_CAN2_RE_RX

◆ GPIO_BANK_CAN2_RE_TX

◆ GPIO_BANK_CAN2_RX

◆ GPIO_BANK_CAN2_TX

◆ GPIO_BANK_CAN_PB_RX

◆ GPIO_BANK_CAN_PB_TX

◆ GPIO_BANK_CAN_PD_RX

◆ GPIO_BANK_CAN_PD_TX

◆ GPIO_BANK_CAN_RX

| #define GPIO_BANK_CAN_RX GPIO_BANK_CAN1_RX /* Alias */ |

◆ GPIO_BANK_CAN_TX

| #define GPIO_BANK_CAN_TX GPIO_BANK_CAN1_TX /* Alias */ |

◆ GPIO_BANK_ETH_RE_RX_DV_CRS_DV

◆ GPIO_BANK_ETH_RE_RXD0

◆ GPIO_BANK_ETH_RE_RXD1

◆ GPIO_BANK_ETH_RE_RXD2

◆ GPIO_BANK_ETH_RE_RXD3

◆ GPIO_BANK_ETH_RX_DV_CRS_DV

◆ GPIO_BANK_ETH_RXD0

◆ GPIO_BANK_ETH_RXD1

◆ GPIO_BANK_ETH_RXD2

◆ GPIO_BANK_ETH_RXD3

◆ GPIO_BANK_I2C1_RE_SCL

◆ GPIO_BANK_I2C1_RE_SDA

◆ GPIO_BANK_I2C1_RE_SMBAI

◆ GPIO_BANK_I2C1_SCL

◆ GPIO_BANK_I2C1_SDA

◆ GPIO_BANK_I2C1_SMBAI

◆ GPIO_BANK_I2C2_SCL

◆ GPIO_BANK_I2C2_SDA

◆ GPIO_BANK_I2C2_SMBAI

◆ GPIO_BANK_JNTRST

◆ GPIO_BANK_JTCK_SWCLK

◆ GPIO_BANK_JTDI

◆ GPIO_BANK_JTDO_TRACESWO

◆ GPIO_BANK_JTMS_SWDIO

◆ GPIO_BANK_SPI1_MISO

◆ GPIO_BANK_SPI1_MOSI

◆ GPIO_BANK_SPI1_NSS

◆ GPIO_BANK_SPI1_RE_MISO

◆ GPIO_BANK_SPI1_RE_MOSI

◆ GPIO_BANK_SPI1_RE_NSS

◆ GPIO_BANK_SPI1_RE_SCK

◆ GPIO_BANK_SPI1_SCK

◆ GPIO_BANK_SPI2_MISO

◆ GPIO_BANK_SPI2_MOSI

◆ GPIO_BANK_SPI2_NSS

◆ GPIO_BANK_SPI2_SCK

◆ GPIO_BANK_SPI3_MISO

◆ GPIO_BANK_SPI3_MOSI

◆ GPIO_BANK_SPI3_NSS

◆ GPIO_BANK_SPI3_RE_MISO

◆ GPIO_BANK_SPI3_RE_MOSI

◆ GPIO_BANK_SPI3_RE_NSS

◆ GPIO_BANK_SPI3_RE_SCK

◆ GPIO_BANK_SPI3_SCK

◆ GPIO_BANK_TIM1_BKIN

◆ GPIO_BANK_TIM1_BKIN_CH123N

◆ GPIO_BANK_TIM1_CH1

◆ GPIO_BANK_TIM1_CH1N

◆ GPIO_BANK_TIM1_CH2

◆ GPIO_BANK_TIM1_CH2N

◆ GPIO_BANK_TIM1_CH3

◆ GPIO_BANK_TIM1_CH3N

◆ GPIO_BANK_TIM1_CH4

◆ GPIO_BANK_TIM1_ETR

◆ GPIO_BANK_TIM1_ETR_CH1234

◆ GPIO_BANK_TIM1_FR

◆ GPIO_BANK_TIM1_FR_BKIN

◆ GPIO_BANK_TIM1_FR_CH1

◆ GPIO_BANK_TIM1_FR_CH1N

◆ GPIO_BANK_TIM1_FR_CH2

◆ GPIO_BANK_TIM1_FR_CH2N

◆ GPIO_BANK_TIM1_FR_CH3

◆ GPIO_BANK_TIM1_FR_CH3N

◆ GPIO_BANK_TIM1_FR_CH4

◆ GPIO_BANK_TIM1_FR_ETR

◆ GPIO_BANK_TIM1_PR_BKIN

◆ GPIO_BANK_TIM1_PR_CH1

◆ GPIO_BANK_TIM1_PR_CH1N

◆ GPIO_BANK_TIM1_PR_CH2

◆ GPIO_BANK_TIM1_PR_CH23N

◆ GPIO_BANK_TIM1_PR_CH2N

◆ GPIO_BANK_TIM1_PR_CH3

◆ GPIO_BANK_TIM1_PR_CH3N

◆ GPIO_BANK_TIM1_PR_CH4

◆ GPIO_BANK_TIM1_PR_ETR

◆ GPIO_BANK_TIM1_PR_ETR_CH1234_BKIN_CH1N

◆ GPIO_BANK_TIM2

◆ GPIO_BANK_TIM2_CH1_ETR

◆ GPIO_BANK_TIM2_CH2

◆ GPIO_BANK_TIM2_CH3

◆ GPIO_BANK_TIM2_CH4

◆ GPIO_BANK_TIM2_FR_CH1_ETR

◆ GPIO_BANK_TIM2_FR_CH2

◆ GPIO_BANK_TIM2_FR_CH234

◆ GPIO_BANK_TIM2_FR_CH3

◆ GPIO_BANK_TIM2_FR_CH4

◆ GPIO_BANK_TIM2_PR1_CH134

◆ GPIO_BANK_TIM2_PR1_CH1_ETR

◆ GPIO_BANK_TIM2_PR1_CH2

◆ GPIO_BANK_TIM2_PR1_CH3

◆ GPIO_BANK_TIM2_PR1_CH4

◆ GPIO_BANK_TIM2_PR2_CH12

◆ GPIO_BANK_TIM2_PR2_CH1_ETR

◆ GPIO_BANK_TIM2_PR2_CH2

◆ GPIO_BANK_TIM2_PR2_CH3

◆ GPIO_BANK_TIM2_PR2_CH34

◆ GPIO_BANK_TIM2_PR2_CH4

◆ GPIO_BANK_TIM3_CH1

◆ GPIO_BANK_TIM3_CH12

◆ GPIO_BANK_TIM3_CH2

◆ GPIO_BANK_TIM3_CH3

◆ GPIO_BANK_TIM3_CH34

◆ GPIO_BANK_TIM3_CH4

◆ GPIO_BANK_TIM3_FR

◆ GPIO_BANK_TIM3_FR_CH1

◆ GPIO_BANK_TIM3_FR_CH2

◆ GPIO_BANK_TIM3_FR_CH3

◆ GPIO_BANK_TIM3_FR_CH4

◆ GPIO_BANK_TIM3_PR

◆ GPIO_BANK_TIM3_PR_CH1

◆ GPIO_BANK_TIM3_PR_CH2

◆ GPIO_BANK_TIM3_PR_CH3

◆ GPIO_BANK_TIM3_PR_CH4

◆ GPIO_BANK_TIM4

◆ GPIO_BANK_TIM4_CH1

◆ GPIO_BANK_TIM4_CH2

◆ GPIO_BANK_TIM4_CH3

◆ GPIO_BANK_TIM4_CH4

◆ GPIO_BANK_TIM4_RE

◆ GPIO_BANK_TIM4_RE_CH1

◆ GPIO_BANK_TIM4_RE_CH2

◆ GPIO_BANK_TIM4_RE_CH3

◆ GPIO_BANK_TIM4_RE_CH4

◆ GPIO_BANK_TIM5

◆ GPIO_BANK_TIM5_CH1

◆ GPIO_BANK_TIM5_CH2

◆ GPIO_BANK_TIM5_CH3

◆ GPIO_BANK_TIM5_CH4

◆ GPIO_BANK_TRACECK

◆ GPIO_BANK_TRACED0

◆ GPIO_BANK_TRACED1

◆ GPIO_BANK_TRACED2

◆ GPIO_BANK_TRACED3

◆ GPIO_BANK_UART4_RX

◆ GPIO_BANK_UART4_TX

◆ GPIO_BANK_UART5_RX

◆ GPIO_BANK_UART5_TX

◆ GPIO_BANK_USART1_CK

◆ GPIO_BANK_USART1_CTS

◆ GPIO_BANK_USART1_RE_RX

◆ GPIO_BANK_USART1_RE_TX

◆ GPIO_BANK_USART1_RTS

◆ GPIO_BANK_USART1_RX

◆ GPIO_BANK_USART1_TX

◆ GPIO_BANK_USART2_CK

◆ GPIO_BANK_USART2_CTS

◆ GPIO_BANK_USART2_RE_CK

◆ GPIO_BANK_USART2_RE_CTS

◆ GPIO_BANK_USART2_RE_RTS

◆ GPIO_BANK_USART2_RE_RX

◆ GPIO_BANK_USART2_RE_TX

◆ GPIO_BANK_USART2_RTS

◆ GPIO_BANK_USART2_RX

◆ GPIO_BANK_USART2_TX

◆ GPIO_BANK_USART3_CK

◆ GPIO_BANK_USART3_CTS

◆ GPIO_BANK_USART3_FR_CK

◆ GPIO_BANK_USART3_FR_CTS

◆ GPIO_BANK_USART3_FR_RTS

◆ GPIO_BANK_USART3_FR_RX

◆ GPIO_BANK_USART3_FR_TX

◆ GPIO_BANK_USART3_PR_CK

◆ GPIO_BANK_USART3_PR_CTS

◆ GPIO_BANK_USART3_PR_RTS

◆ GPIO_BANK_USART3_PR_RX

◆ GPIO_BANK_USART3_PR_TX

◆ GPIO_BANK_USART3_RTS

◆ GPIO_BANK_USART3_RX

◆ GPIO_BANK_USART3_TX

◆ GPIO_BRR

◆ GPIO_BSRR

◆ GPIO_CAN1_PB_RX

| #define GPIO_CAN1_PB_RX GPIO_CAN_PB_RX /* Alias */ |

◆ GPIO_CAN1_PB_TX

| #define GPIO_CAN1_PB_TX GPIO_CAN_PB_TX /* Alias */ |

◆ GPIO_CAN1_PD_RX

| #define GPIO_CAN1_PD_RX GPIO_CAN_PD_RX /* Alias */ |

◆ GPIO_CAN1_PD_TX

| #define GPIO_CAN1_PD_TX GPIO_CAN_PD_TX /* Alias */ |

◆ GPIO_CAN1_RX

◆ GPIO_CAN1_TX

◆ GPIO_CAN2_RE_RX

◆ GPIO_CAN2_RE_TX

◆ GPIO_CAN2_RX

◆ GPIO_CAN2_TX

◆ GPIO_CAN_PB_RX

◆ GPIO_CAN_PB_TX

◆ GPIO_CAN_PD_RX

◆ GPIO_CAN_PD_TX

◆ GPIO_CAN_RX

| #define GPIO_CAN_RX GPIO_CAN1_RX /* Alias */ |

◆ GPIO_CAN_TX

| #define GPIO_CAN_TX GPIO_CAN1_TX /* Alias */ |

◆ GPIO_CRH

◆ GPIO_CRL

◆ GPIO_ETH_RE_RX_DV_CRS_DV

◆ GPIO_ETH_RE_RXD0

◆ GPIO_ETH_RE_RXD1

◆ GPIO_ETH_RE_RXD2

◆ GPIO_ETH_RE_RXD3

◆ GPIO_ETH_RX_DV_CRS_DV

◆ GPIO_ETH_RXD0

◆ GPIO_ETH_RXD1

◆ GPIO_ETH_RXD2

◆ GPIO_ETH_RXD3

◆ GPIO_I2C1_RE_SCL

◆ GPIO_I2C1_RE_SDA

◆ GPIO_I2C1_RE_SMBAI

◆ GPIO_I2C1_SCL

◆ GPIO_I2C1_SDA

◆ GPIO_I2C1_SMBAI

◆ GPIO_I2C2_SCL

◆ GPIO_I2C2_SDA

◆ GPIO_I2C2_SMBAI

◆ GPIO_IDR

◆ GPIO_JNTRST

◆ GPIO_JTCK_SWCLK

◆ GPIO_JTDI

◆ GPIO_JTDO_TRACESWO

◆ GPIO_JTMS_SWDIO

◆ GPIO_LCKK

| #define GPIO_LCKK (1 << 16) |

Definition at line 45 of file gpio_common_all.h.

◆ GPIO_LCKR

◆ GPIO_ODR

◆ GPIO_SPI1_MISO

◆ GPIO_SPI1_MOSI

◆ GPIO_SPI1_NSS

◆ GPIO_SPI1_RE_MISO

◆ GPIO_SPI1_RE_MOSI

◆ GPIO_SPI1_RE_NSS

◆ GPIO_SPI1_RE_SCK

◆ GPIO_SPI1_SCK

◆ GPIO_SPI2_MISO

◆ GPIO_SPI2_MOSI

◆ GPIO_SPI2_NSS

◆ GPIO_SPI2_SCK

◆ GPIO_SPI3_MISO

◆ GPIO_SPI3_MOSI

◆ GPIO_SPI3_NSS

◆ GPIO_SPI3_RE_MISO

◆ GPIO_SPI3_RE_MOSI

◆ GPIO_SPI3_RE_NSS

◆ GPIO_SPI3_RE_SCK

◆ GPIO_SPI3_SCK

◆ GPIO_TIM1_BKIN

◆ GPIO_TIM1_CH1

◆ GPIO_TIM1_CH1N

◆ GPIO_TIM1_CH2

◆ GPIO_TIM1_CH2N

◆ GPIO_TIM1_CH3

◆ GPIO_TIM1_CH3N

◆ GPIO_TIM1_CH4

◆ GPIO_TIM1_ETR

◆ GPIO_TIM1_FR_BKIN

◆ GPIO_TIM1_FR_CH1

◆ GPIO_TIM1_FR_CH1N

◆ GPIO_TIM1_FR_CH2

◆ GPIO_TIM1_FR_CH2N

◆ GPIO_TIM1_FR_CH3

◆ GPIO_TIM1_FR_CH3N

◆ GPIO_TIM1_FR_CH4

◆ GPIO_TIM1_FR_ETR

◆ GPIO_TIM1_PR_BKIN

◆ GPIO_TIM1_PR_CH1

◆ GPIO_TIM1_PR_CH1N

◆ GPIO_TIM1_PR_CH2

◆ GPIO_TIM1_PR_CH2N

◆ GPIO_TIM1_PR_CH3

◆ GPIO_TIM1_PR_CH3N

◆ GPIO_TIM1_PR_CH4

◆ GPIO_TIM1_PR_ETR

◆ GPIO_TIM2_CH1_ETR

◆ GPIO_TIM2_CH2

◆ GPIO_TIM2_CH3

◆ GPIO_TIM2_CH4

◆ GPIO_TIM2_FR_CH1_ETR

◆ GPIO_TIM2_FR_CH2

◆ GPIO_TIM2_FR_CH3

◆ GPIO_TIM2_FR_CH4

◆ GPIO_TIM2_PR1_CH1_ETR

◆ GPIO_TIM2_PR1_CH2

◆ GPIO_TIM2_PR1_CH3

◆ GPIO_TIM2_PR1_CH4

◆ GPIO_TIM2_PR2_CH1_ETR

◆ GPIO_TIM2_PR2_CH2

◆ GPIO_TIM2_PR2_CH3

◆ GPIO_TIM2_PR2_CH4

◆ GPIO_TIM3_CH1

◆ GPIO_TIM3_CH2

◆ GPIO_TIM3_CH3

◆ GPIO_TIM3_CH4

◆ GPIO_TIM3_FR_CH1

◆ GPIO_TIM3_FR_CH2

◆ GPIO_TIM3_FR_CH3

◆ GPIO_TIM3_FR_CH4

◆ GPIO_TIM3_PR_CH1

◆ GPIO_TIM3_PR_CH2

◆ GPIO_TIM3_PR_CH3

◆ GPIO_TIM3_PR_CH4

◆ GPIO_TIM4_CH1

◆ GPIO_TIM4_CH2

◆ GPIO_TIM4_CH3

◆ GPIO_TIM4_CH4

◆ GPIO_TIM4_RE_CH1

◆ GPIO_TIM4_RE_CH2

◆ GPIO_TIM4_RE_CH3

◆ GPIO_TIM4_RE_CH4

◆ GPIO_TIM5_CH1

◆ GPIO_TIM5_CH2

◆ GPIO_TIM5_CH3

◆ GPIO_TIM5_CH4

◆ GPIO_TRACECK

◆ GPIO_TRACED0

◆ GPIO_TRACED1

◆ GPIO_TRACED2

◆ GPIO_TRACED3

◆ GPIO_UART4_RX

◆ GPIO_UART4_TX

◆ GPIO_UART5_RX

◆ GPIO_UART5_TX

◆ GPIO_USART1_CK

◆ GPIO_USART1_CTS

◆ GPIO_USART1_RE_RX

◆ GPIO_USART1_RE_TX

◆ GPIO_USART1_RTS

◆ GPIO_USART1_RX

◆ GPIO_USART1_TX

◆ GPIO_USART2_CK

◆ GPIO_USART2_CTS

◆ GPIO_USART2_RE_CK

◆ GPIO_USART2_RE_CTS

◆ GPIO_USART2_RE_RTS

◆ GPIO_USART2_RE_RX

◆ GPIO_USART2_RE_TX

◆ GPIO_USART2_RTS

◆ GPIO_USART2_RX

◆ GPIO_USART2_TX

◆ GPIO_USART3_CK

◆ GPIO_USART3_CTS

◆ GPIO_USART3_FR_CK

◆ GPIO_USART3_FR_CTS

◆ GPIO_USART3_FR_RTS

◆ GPIO_USART3_FR_RX

◆ GPIO_USART3_FR_TX

◆ GPIO_USART3_PR_CK

◆ GPIO_USART3_PR_CTS

◆ GPIO_USART3_PR_RTS

◆ GPIO_USART3_PR_RX

◆ GPIO_USART3_PR_TX

◆ GPIO_USART3_RTS

◆ GPIO_USART3_RX

◆ GPIO_USART3_TX

◆ GPIOA_BRR

◆ GPIOA_BSRR

◆ GPIOA_CRH

◆ GPIOA_CRL

◆ GPIOA_IDR

◆ GPIOA_LCKR

◆ GPIOA_ODR

◆ GPIOB_BRR

◆ GPIOB_BSRR

◆ GPIOB_CRH

◆ GPIOB_CRL

◆ GPIOB_IDR

◆ GPIOB_LCKR

◆ GPIOB_ODR

◆ GPIOC_BRR

◆ GPIOC_BSRR

◆ GPIOC_CRH

◆ GPIOC_CRL

◆ GPIOC_IDR

◆ GPIOC_LCKR

◆ GPIOC_ODR

◆ GPIOD_BRR

◆ GPIOD_BSRR

◆ GPIOD_CRH

◆ GPIOD_CRL

◆ GPIOD_IDR

◆ GPIOD_LCKR

◆ GPIOD_ODR

◆ GPIOE_BRR

◆ GPIOE_BSRR

◆ GPIOE_CRH

◆ GPIOE_CRL

◆ GPIOE_IDR

◆ GPIOE_LCKR

◆ GPIOE_ODR

◆ GPIOF_BRR

◆ GPIOF_BSRR

◆ GPIOF_CRH

◆ GPIOF_CRL

◆ GPIOF_IDR

◆ GPIOF_LCKR

◆ GPIOF_ODR

◆ GPIOG_BRR

◆ GPIOG_BSRR

◆ GPIOG_CRH

◆ GPIOG_CRL

◆ GPIOG_IDR

◆ GPIOG_LCKR

◆ GPIOG_ODR

Function Documentation

◆ gpio_clear()

| void gpio_clear | ( | uint32_t | gpioport, |

| uint16_t | gpios | ||

| ) |

Clear a Group of Pins Atomic.

Clear one or more pins of the given GPIO port to 0 in an atomic operation.

- Parameters

-

[in] gpioport Unsigned int32. Port identifier GPIO Port IDs [in] gpios Unsigned int16. Pin identifiers GPIO Pin Identifiers If multiple pins are to be changed, use bitwise OR '|' to separate them.

Definition at line 56 of file gpio_common_all.c.

References GPIO_BSRR.

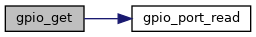

◆ gpio_get()

| uint16_t gpio_get | ( | uint32_t | gpioport, |

| uint16_t | gpios | ||

| ) |

Read a Group of Pins.

- Parameters

-

[in] gpioport Unsigned int32. Port identifier GPIO Port IDs [in] gpios Unsigned int16. Pin identifiers GPIO Pin Identifiers If multiple pins are to be read, use bitwise OR '|' to separate them.

- Returns

- Unsigned int16 value of the pin values. The bit position of the pin value returned corresponds to the pin number.

Definition at line 71 of file gpio_common_all.c.

References gpio_port_read().

◆ gpio_port_config_lock()

| void gpio_port_config_lock | ( | uint32_t | gpioport, |

| uint16_t | gpios | ||

| ) |

Lock the Configuration of a Group of Pins.

The configuration of one or more pins of the given GPIO port is locked. There is no mechanism to unlock these via software. Unlocking occurs at the next reset.

- Parameters

-

[in] gpioport Unsigned int32. Port identifier GPIO Port IDs [in] gpios Unsigned int16. Pin identifiers GPIO Pin Identifiers If multiple pins are to be locked, use bitwise OR '|' to separate them.

Definition at line 132 of file gpio_common_all.c.

◆ gpio_port_read()

| uint16_t gpio_port_read | ( | uint32_t | gpioport | ) |

Read from a Port.

Read the current value of the given GPIO port. Only the lower 16 bits contain valid pin data.

- Parameters

-

[in] gpioport Unsigned int32. Port identifier GPIO Port IDs

- Returns

- Unsigned int16. The value held in the specified GPIO port.

Definition at line 102 of file gpio_common_all.c.

References GPIO_IDR.

Referenced by gpio_get().

◆ gpio_port_write()

| void gpio_port_write | ( | uint32_t | gpioport, |

| uint16_t | data | ||

| ) |

Write to a Port.

Write a value to the given GPIO port.

- Parameters

-

[in] gpioport Unsigned int32. Port identifier GPIO Port IDs [in] data Unsigned int16. The value to be written to the GPIO port.

Definition at line 115 of file gpio_common_all.c.

References GPIO_ODR.

◆ gpio_primary_remap()

| void gpio_primary_remap | ( | uint32_t | swjdisable, |

| uint32_t | maps | ||

| ) |

Map Alternate Function Port Bits (Main Set)

A number of alternate function ports can be remapped to defined alternative port bits to avoid clashes in cases where multiple alternate functions are present. Refer to the datasheets for the particular mapping desired. This provides the main set of remap functionality. See gpio_secondary_remap for a number of lesser used remaps.

The AFIO remapping feature is used only with the STM32F10x series.

- Note

- The Serial Wire JTAG disable controls allow certain GPIO ports to become available in place of some of the SWJ signals. Full SWJ capability is obtained by setting this to zero. The value of this must be specified for every call to this function as its current value cannot be ascertained from the hardware.

- Parameters

-

[in] swjdisable Disable parts of the SWJ capability Serial Wire JTAG disables. [in] maps Bitwise OR of map enable controls you wish to enable from Alternate Function Remap Controls, Alternate Function Remap Controls for CAN 1, Alternate Function Remap Controls for Timer 3, Alternate Function Remap Controls for Timer 2, Alternate Function Remap Controls for Timer 1, Alternate Function Remap Controls for USART 3. For connectivity line devices only Alternate Function Remap Controls for Connectivity are also available.

Definition at line 167 of file gpio.c.

References AFIO_MAPR.

◆ gpio_secondary_remap()

| void gpio_secondary_remap | ( | uint32_t | maps | ) |

Map Alternate Function Port Bits (Secondary Set)

A number of alternate function ports can be remapped to defined alternative port bits to avoid clashes in cases where multiple alternate functions are present. Refer to the datasheets for the particular mapping desired. This provides the second smaller and less used set of remap functionality. See gpio_primary_remap for the main set of remaps.

The AFIO remapping feature is used only with the STM32F10x series.

- Parameters

-

[in] maps Unsigned int32. Bitwise OR of map enable controls from Alternate Function Remap Controls Secondary Set

Definition at line 192 of file gpio.c.

References AFIO_MAPR2.

◆ gpio_set()

| void gpio_set | ( | uint32_t | gpioport, |

| uint16_t | gpios | ||

| ) |

Set a Group of Pins Atomic.

Set one or more pins of the given GPIO port to 1 in an atomic operation.

- Parameters

-

[in] gpioport Unsigned int32. Port identifier GPIO Port IDs [in] gpios Unsigned int16. Pin identifiers GPIO Pin Identifiers If multiple pins are to be changed, use bitwise OR '|' to separate them.

Definition at line 41 of file gpio_common_all.c.

References GPIO_BSRR.

◆ gpio_set_eventout()

| void gpio_set_eventout | ( | uint8_t | evoutport, |

| uint8_t | evoutpin | ||

| ) |

Map the EVENTOUT signal.

Enable the EVENTOUT signal and select the port and pin to be used.

- Parameters

-

[in] evoutport Unsigned int8. Port for EVENTOUT signal EVENTOUT Port selection [in] evoutpin Unsigned int8. Pin for EVENTOUT signal EVENTOUT Pin selection

Definition at line 139 of file gpio.c.

References AFIO_EVCR, and AFIO_EVCR_EVOE.

◆ gpio_set_mode()

| void gpio_set_mode | ( | uint32_t | gpioport, |

| uint8_t | mode, | ||

| uint8_t | cnf, | ||

| uint16_t | gpios | ||

| ) |

Set GPIO Pin Mode.

Sets the mode (input/output) and configuration (analog/digitial and open drain/push pull), for a set of GPIO pins on a given GPIO port.

- Parameters

-

[in] gpioport Unsigned int32. Port identifier GPIO Port IDs [in] mode Unsigned int8. Pin mode GPIO Pin Mode [in] cnf Unsigned int8. Pin configuration GPIO Pin Configuration [in] gpios Unsigned int16. Pin identifiers GPIO Pin Identifiers If multiple pins are to be set, use bitwise OR '|' to separate them.

◆ gpio_toggle()

| void gpio_toggle | ( | uint32_t | gpioport, |

| uint16_t | gpios | ||

| ) |

Toggle a Group of Pins.

Toggle one or more pins of the given GPIO port. The toggling is not atomic, but the non-toggled pins are not affected.

- Parameters

-

[in] gpioport Unsigned int32. Port identifier GPIO Port IDs [in] gpios Unsigned int16. Pin identifiers GPIO Pin Identifiers If multiple pins are to be changed, use bitwise OR '|' to separate them.

Definition at line 87 of file gpio_common_all.c.