#include <libopencm3/stm32/common/adc_common_v1.h>

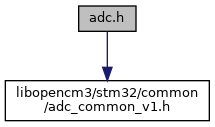

Include dependency graph for f1/adc.h:

Go to the source code of this file.

Macros | |

| #define | ADC_JOFR1(block) MMIO32((block) + 0x14) |

| #define | ADC_JOFR2(block) MMIO32((block) + 0x18) |

| #define | ADC_JOFR3(block) MMIO32((block) + 0x1c) |

| #define | ADC_JOFR4(block) MMIO32((block) + 0x20) |

| #define | ADC_HTR(block) MMIO32((block) + 0x24) |

| #define | ADC_LTR(block) MMIO32((block) + 0x28) |

| #define | ADC_SQR1(block) MMIO32((block) + 0x2c) |

| #define | ADC_SQR2(block) MMIO32((block) + 0x30) |

| #define | ADC_SQR3(block) MMIO32((block) + 0x34) |

| #define | ADC_JSQR(block) MMIO32((block) + 0x38) |

| #define | ADC_JDR1(block) MMIO32((block) + 0x3c) |

| #define | ADC_JDR2(block) MMIO32((block) + 0x40) |

| #define | ADC_JDR3(block) MMIO32((block) + 0x44) |

| #define | ADC_JDR4(block) MMIO32((block) + 0x48) |

| #define | ADC_DR(block) MMIO32((block) + 0x4c) |

| #define | ADC_CR1_DUALMOD_IND (0x0 << 16) |

| Independent (non-dual) mode. More... | |

| #define | ADC_CR1_DUALMOD_CRSISM (0x1 << 16) |

| Combined regular simultaneous + injected simultaneous mode. More... | |

| #define | ADC_CR1_DUALMOD_CRSATM (0x2 << 16) |

| Combined regular simultaneous + alternate trigger mode. More... | |

| #define | ADC_CR1_DUALMOD_CISFIM (0x3 << 16) |

| Combined injected simultaneous + fast interleaved mode. More... | |

| #define | ADC_CR1_DUALMOD_CISSIM (0x4 << 16) |

| Combined injected simultaneous + slow interleaved mode. More... | |

| #define | ADC_CR1_DUALMOD_ISM (0x5 << 16) |

| Injected simultaneous mode only. More... | |

| #define | ADC_CR1_DUALMOD_RSM (0x6 << 16) |

| Regular simultaneous mode only. More... | |

| #define | ADC_CR1_DUALMOD_FIM (0x7 << 16) |

| Fast interleaved mode only. More... | |

| #define | ADC_CR1_DUALMOD_SIM (0x8 << 16) |

| Slow interleaved mode only. More... | |

| #define | ADC_CR1_DUALMOD_ATM (0x9 << 16) |

| Alternate trigger mode only. More... | |

| #define | ADC_CR1_DUALMOD_MASK (0xF << 16) |

| #define | ADC_CR1_DUALMOD_SHIFT 16 |

| #define | ADC_CR1_AWDCH_MAX 17 |

| #define | ADC_CR2_TSVREFE (1 << 23) |

| Temperature sensor and V_REFINT enable. More... | |

| #define | ADC_CR2_SWSTART (1 << 22) |

| Start conversion of regular channels. More... | |

| #define | ADC_CR2_JSWSTART (1 << 21) |

| Start conversion of injected channels. More... | |

| #define | ADC_CR2_EXTTRIG (1 << 20) |

| External trigger conversion mode for regular channels. More... | |

| #define | ADC_CR2_EXTSEL_TIM1_CC1 (0x0 << 17) |

| Timer 1 Compare Output 1. More... | |

| #define | ADC_CR2_EXTSEL_TIM1_CC2 (0x1 << 17) |

| Timer 1 Compare Output 2. More... | |

| #define | ADC_CR2_EXTSEL_TIM1_CC3 (0x2 << 17) |

| Timer 1 Compare Output 3. More... | |

| #define | ADC_CR2_EXTSEL_TIM2_CC2 (0x3 << 17) |

| Timer 2 Compare Output 2. More... | |

| #define | ADC_CR2_EXTSEL_TIM3_TRGO (0x4 << 17) |

| Timer 3 Trigger Output. More... | |

| #define | ADC_CR2_EXTSEL_TIM4_CC4 (0x5 << 17) |

| Timer 4 Compare Output 4. More... | |

| #define | ADC_CR2_EXTSEL_EXTI11 (0x6 << 17) |

| External Interrupt 11. More... | |

| #define | ADC_CR2_EXTSEL_SWSTART (0x7 << 17) |

| Software Trigger. More... | |

| #define | ADC_CR2_EXTSEL_TIM3_CC1 (0x0 << 17) |

| Timer 2 Compare Output 1. More... | |

| #define | ADC_CR2_EXTSEL_TIM2_CC3 (0x1 << 17) |

| Timer 2 Compare Output 3. More... | |

| #define | ADC_CR2_EXTSEL_TIM1_CC3 (0x2 << 17) |

| Timer 1 Compare Output 3. More... | |

| #define | ADC_CR2_EXTSEL_TIM8_CC1 (0x3 << 17) |

| Timer 8 Compare Output 1. More... | |

| #define | ADC_CR2_EXTSEL_TIM8_TRGO (0x4 << 17) |

| Timer 8 Trigger Output. More... | |

| #define | ADC_CR2_EXTSEL_TIM5_CC1 (0x5 << 17) |

| Timer 5 Compare Output 1. More... | |

| #define | ADC_CR2_EXTSEL_TIM5_CC3 (0x6 << 17) |

| Timer 5 Compare Output 3. More... | |

| #define | ADC_CR2_EXTSEL_MASK (0x7 << 17) |

| #define | ADC_CR2_EXTSEL_SHIFT 17 |

| #define | ADC_CR2_JEXTTRIG (1 << 15) |

| #define | ADC_CR2_JEXTSEL_TIM1_TRGO (0x0 << 12) |

| Timer 1 Trigger Output. More... | |

| #define | ADC_CR2_JEXTSEL_TIM1_CC4 (0x1 << 12) |

| Timer 1 Compare Output 4. More... | |

| #define | ADC_CR2_JEXTSEL_TIM2_TRGO (0x2 << 12) |

| Timer 2 Trigger Output. More... | |

| #define | ADC_CR2_JEXTSEL_TIM2_CC1 (0x3 << 12) |

| Timer 2 Compare Output 1. More... | |

| #define | ADC_CR2_JEXTSEL_TIM3_CC4 (0x4 << 12) |

| Timer 3 Compare Output 4. More... | |

| #define | ADC_CR2_JEXTSEL_TIM4_TRGO (0x5 << 12) |

| Timer 4 Trigger Output. More... | |

| #define | ADC_CR2_JEXTSEL_EXTI15 (0x6 << 12) |

| External Interrupt 15. More... | |

| #define | ADC_CR2_JEXTSEL_JSWSTART (0x7 << 12) /* Software start. */ |

| Injected Software Trigger. More... | |

| #define | ADC_CR2_JEXTSEL_TIM1_TRGO (0x0 << 12) |

| Timer 1 Trigger Output. More... | |

| #define | ADC_CR2_JEXTSEL_TIM1_CC4 (0x1 << 12) |

| Timer 1 Compare Output 4. More... | |

| #define | ADC_CR2_JEXTSEL_TIM4_CC3 (0x2 << 12) |

| Timer 4 Compare Output 3. More... | |

| #define | ADC_CR2_JEXTSEL_TIM8_CC2 (0x3 << 12) |

| Timer 8 Compare Output 2. More... | |

| #define | ADC_CR2_JEXTSEL_TIM8_CC4 (0x4 << 12) |

| Timer 8 Compare Output 4. More... | |

| #define | ADC_CR2_JEXTSEL_TIM5_TRGO (0x5 << 12) |

| Timer 5 Trigger Output. More... | |

| #define | ADC_CR2_JEXTSEL_TIM5_CC4 (0x6 << 12) |

| Timer 5 Compare Output 4. More... | |

| #define | ADC_CR2_JEXTSEL_JSWSTART (0x7 << 12) /* Software start. */ |

| Injected Software Trigger. More... | |

| #define | ADC_CR2_JEXTSEL_MASK (0x7 << 12) |

| #define | ADC_CR2_JEXTSEL_SHIFT 12 |

| #define | ADC_CR2_ALIGN_RIGHT (0 << 11) |

| #define | ADC_CR2_ALIGN_LEFT (1 << 11) |

| #define | ADC_CR2_ALIGN (1 << 11) |

| #define | ADC_CR2_DMA (1 << 8) |

| #define | ADC_CR2_RSTCAL (1 << 3) |

| #define | ADC_CR2_CAL (1 << 2) |

| #define | ADC_CR2_CONT (1 << 1) |

| #define | ADC_CR2_ADON (1 << 0) |

| #define | ADC_SMPR1_SMP17_LSB 21 |

| #define | ADC_SMPR1_SMP16_LSB 18 |

| #define | ADC_SMPR1_SMP15_LSB 15 |

| #define | ADC_SMPR1_SMP14_LSB 12 |

| #define | ADC_SMPR1_SMP13_LSB 9 |

| #define | ADC_SMPR1_SMP12_LSB 6 |

| #define | ADC_SMPR1_SMP11_LSB 3 |

| #define | ADC_SMPR1_SMP10_LSB 0 |

| #define | ADC_SMPR1_SMP17_MSK (0x7 << ADC_SMPR1_SMP17_LSB) |

| #define | ADC_SMPR1_SMP16_MSK (0x7 << ADC_SMPR1_SMP16_LSB) |

| #define | ADC_SMPR1_SMP15_MSK (0x7 << ADC_SMPR1_SMP15_LSB) |

| #define | ADC_SMPR1_SMP14_MSK (0x7 << ADC_SMPR1_SMP14_LSB) |

| #define | ADC_SMPR1_SMP13_MSK (0x7 << ADC_SMPR1_SMP13_LSB) |

| #define | ADC_SMPR1_SMP12_MSK (0x7 << ADC_SMPR1_SMP12_LSB) |

| #define | ADC_SMPR1_SMP11_MSK (0x7 << ADC_SMPR1_SMP11_LSB) |

| #define | ADC_SMPR1_SMP10_MSK (0x7 << ADC_SMPR1_SMP10_LSB) |

| #define | ADC_SMPR2_SMP9_LSB 27 |

| #define | ADC_SMPR2_SMP8_LSB 24 |

| #define | ADC_SMPR2_SMP7_LSB 21 |

| #define | ADC_SMPR2_SMP6_LSB 18 |

| #define | ADC_SMPR2_SMP5_LSB 15 |

| #define | ADC_SMPR2_SMP4_LSB 12 |

| #define | ADC_SMPR2_SMP3_LSB 9 |

| #define | ADC_SMPR2_SMP2_LSB 6 |

| #define | ADC_SMPR2_SMP1_LSB 3 |

| #define | ADC_SMPR2_SMP0_LSB 0 |

| #define | ADC_SMPR2_SMP9_MSK (0x7 << ADC_SMPR2_SMP9_LSB) |

| #define | ADC_SMPR2_SMP8_MSK (0x7 << ADC_SMPR2_SMP8_LSB) |

| #define | ADC_SMPR2_SMP7_MSK (0x7 << ADC_SMPR2_SMP7_LSB) |

| #define | ADC_SMPR2_SMP6_MSK (0x7 << ADC_SMPR2_SMP6_LSB) |

| #define | ADC_SMPR2_SMP5_MSK (0x7 << ADC_SMPR2_SMP5_LSB) |

| #define | ADC_SMPR2_SMP4_MSK (0x7 << ADC_SMPR2_SMP4_LSB) |

| #define | ADC_SMPR2_SMP3_MSK (0x7 << ADC_SMPR2_SMP3_LSB) |

| #define | ADC_SMPR2_SMP2_MSK (0x7 << ADC_SMPR2_SMP2_LSB) |

| #define | ADC_SMPR2_SMP1_MSK (0x7 << ADC_SMPR2_SMP1_LSB) |

| #define | ADC_SMPR2_SMP0_MSK (0x7 << ADC_SMPR2_SMP0_LSB) |

| #define | ADC_SMPR_SMP_1DOT5CYC 0x0 |

| #define | ADC_SMPR_SMP_7DOT5CYC 0x1 |

| #define | ADC_SMPR_SMP_13DOT5CYC 0x2 |

| #define | ADC_SMPR_SMP_28DOT5CYC 0x3 |

| #define | ADC_SMPR_SMP_41DOT5CYC 0x4 |

| #define | ADC_SMPR_SMP_55DOT5CYC 0x5 |

| #define | ADC_SMPR_SMP_71DOT5CYC 0x6 |

| #define | ADC_SMPR_SMP_239DOT5CYC 0x7 |

| #define | ADC_SQR_MAX_CHANNELS_REGULAR 16 |

| #define | ADC_SQR1_SQ16_LSB 15 |

| #define | ADC_SQR1_SQ15_LSB 10 |

| #define | ADC_SQR1_SQ14_LSB 5 |

| #define | ADC_SQR1_SQ13_LSB 0 |

| #define | ADC_SQR1_L_MSK (0xf << ADC_SQR1_L_LSB) |

| #define | ADC_SQR1_SQ16_MSK (0x1f << ADC_SQR1_SQ16_LSB) |

| #define | ADC_SQR1_SQ15_MSK (0x1f << ADC_SQR1_SQ15_LSB) |

| #define | ADC_SQR1_SQ14_MSK (0x1f << ADC_SQR1_SQ14_LSB) |

| #define | ADC_SQR1_SQ13_MSK (0x1f << ADC_SQR1_SQ13_LSB) |

| #define | ADC_SQR2_SQ12_LSB 25 |

| #define | ADC_SQR2_SQ11_LSB 20 |

| #define | ADC_SQR2_SQ10_LSB 15 |

| #define | ADC_SQR2_SQ9_LSB 10 |

| #define | ADC_SQR2_SQ8_LSB 5 |

| #define | ADC_SQR2_SQ7_LSB 0 |

| #define | ADC_SQR2_SQ12_MSK (0x1f << ADC_SQR2_SQ12_LSB) |

| #define | ADC_SQR2_SQ11_MSK (0x1f << ADC_SQR2_SQ11_LSB) |

| #define | ADC_SQR2_SQ10_MSK (0x1f << ADC_SQR2_SQ10_LSB) |

| #define | ADC_SQR2_SQ9_MSK (0x1f << ADC_SQR2_SQ9_LSB) |

| #define | ADC_SQR2_SQ8_MSK (0x1f << ADC_SQR2_SQ8_LSB) |

| #define | ADC_SQR2_SQ7_MSK (0x1f << ADC_SQR2_SQ7_LSB) |

| #define | ADC_SQR3_SQ6_LSB 25 |

| #define | ADC_SQR3_SQ5_LSB 20 |

| #define | ADC_SQR3_SQ4_LSB 15 |

| #define | ADC_SQR3_SQ3_LSB 10 |

| #define | ADC_SQR3_SQ2_LSB 5 |

| #define | ADC_SQR3_SQ1_LSB 0 |

| #define | ADC_SQR3_SQ6_MSK (0x1f << ADC_SQR3_SQ6_LSB) |

| #define | ADC_SQR3_SQ5_MSK (0x1f << ADC_SQR3_SQ5_LSB) |

| #define | ADC_SQR3_SQ4_MSK (0x1f << ADC_SQR3_SQ4_LSB) |

| #define | ADC_SQR3_SQ3_MSK (0x1f << ADC_SQR3_SQ3_LSB) |

| #define | ADC_SQR3_SQ2_MSK (0x1f << ADC_SQR3_SQ2_LSB) |

| #define | ADC_SQR3_SQ1_MSK (0x1f << ADC_SQR3_SQ1_LSB) |

| #define | ADC_JDATA_LSB 0 |

| #define | ADC_DATA_LSB 0 |

| #define | ADC_ADC2DATA_LSB 16 /* ADC1 only (dual mode) */ |

| #define | ADC_JDATA_MSK (0xffff << ADC_JDATA_LSB) |

| #define | ADC_DATA_MSK (0xffff << ADC_DA) |

| #define | ADC_ADC2DATA_MSK (0xffff << ADC_ADC2DATA_LSB) |

| #define | ADC_CHANNEL_TEMP 16 |

| #define | ADC_CHANNEL_VREF 17 |

Functions | |

| void | adc_start_conversion_direct (uint32_t adc) |

| ADC Start a Conversion Without Trigger. More... | |

| void | adc_set_dual_mode (uint32_t mode) |

| ADC Set Dual A/D Mode. More... | |

| void | adc_enable_temperature_sensor (void) |

| ADC Enable The Temperature Sensor. More... | |

| void | adc_disable_temperature_sensor (void) |

| ADC Disable The Temperature Sensor. More... | |

| void | adc_enable_external_trigger_regular (uint32_t adc, uint32_t trigger) |

| ADC Enable an External Trigger for Regular Channels. More... | |

| void | adc_enable_external_trigger_injected (uint32_t adc, uint32_t trigger) |

| ADC Enable an External Trigger for Injected Channels. More... | |

| void | adc_reset_calibration (uint32_t adc) |

| ADC Initialize Calibration Registers. More... | |

| void | adc_calibration (uint32_t adc) LIBOPENCM3_DEPRECATED("see adc_calibrate/_async") |

| ADC Calibration. More... | |

| void | adc_calibrate_async (uint32_t adc) |

| Start the ADC calibration and immediately return. More... | |

| bool | adc_is_calibrating (uint32_t adc) |

| Is the ADC Calibrating? More... | |

| void | adc_calibrate (uint32_t adc) |

| Start ADC calibration and wait for it to finish. More... | |