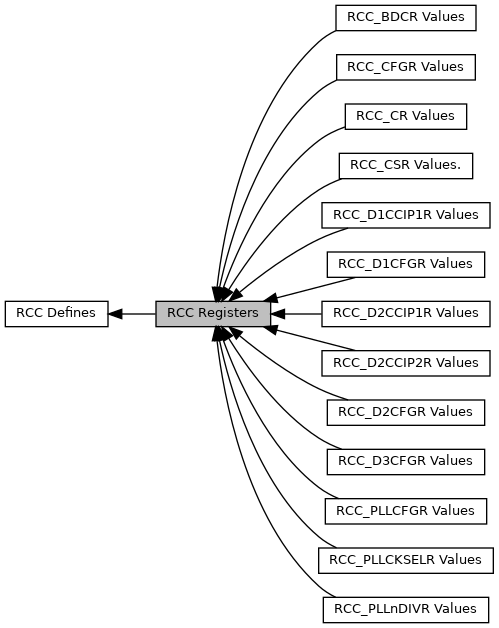

RCC Registers

Collaboration diagram for RCC Registers:

Detailed Description

Macro Definition Documentation

◆ RCC_AHB1ENR

◆ RCC_AHB1LPENR

◆ RCC_AHB1RSTR

◆ RCC_AHB2ENR

◆ RCC_AHB2LPENR

◆ RCC_AHB2RSTR

◆ RCC_AHB3ENR

◆ RCC_AHB3RSTR

◆ RCC_AHB4ENR

◆ RCC_AHB4LPENR

◆ RCC_AHB4RSTR

◆ RCC_APB1HENR

◆ RCC_APB1HLPENR

◆ RCC_APB1HRSTR

◆ RCC_APB1LENR

◆ RCC_APB1LLPENR

◆ RCC_APB1LRSTR

◆ RCC_APB2ENR

◆ RCC_APB2LPENR

◆ RCC_APB2RSTR

◆ RCC_APB3ENR

◆ RCC_APB3LPENR

◆ RCC_APB3RSTR

◆ RCC_APB4ENR

◆ RCC_APB4LPENR

◆ RCC_APB4RSTR

◆ RCC_BDCR

◆ RCC_CFGR

◆ RCC_CR

◆ RCC_CRRCR

◆ RCC_CSICFGR

◆ RCC_CSR

◆ RCC_D1CCIPR

◆ RCC_D1CFGR

◆ RCC_D2CCIP1R

◆ RCC_D2CCIP2R

◆ RCC_D2CFGR

◆ RCC_D3CCIPR

◆ RCC_D3CFGR

◆ RCC_DCKCFGR1

◆ RCC_DCKCFGR2

◆ RCC_HSICFGR

◆ RCC_ICSCR

◆ RCC_PLL1DIVR

| #define RCC_PLL1DIVR RCC_PLLDIVR(1) |

◆ RCC_PLL1FRACR

| #define RCC_PLL1FRACR RCC_PLLFRACR(1) |

◆ RCC_PLL2DIVR

| #define RCC_PLL2DIVR RCC_PLLDIVR(2) |

◆ RCC_PLL2FRACR

| #define RCC_PLL2FRACR RCC_PLLFRACR(2) |

◆ RCC_PLL3DIVR

| #define RCC_PLL3DIVR RCC_PLLDIVR(3) |

◆ RCC_PLL3FRACR

| #define RCC_PLL3FRACR RCC_PLLFRACR(3) |