h7/rcc.h File Reference

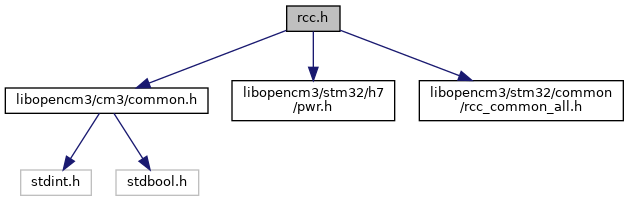

#include <libopencm3/cm3/common.h>#include <libopencm3/stm32/h7/pwr.h>#include <libopencm3/stm32/common/rcc_common_all.h>

Include dependency graph for h7/rcc.h:

Go to the source code of this file.

Data Structures | |

| struct | rcc_pll_config |

| PLL Configuration structure. More... | |

| struct | rcc_pll_config::pll_config |

Enumerations | |

| enum | rcc_clock_source { RCC_CPUCLK , RCC_SYSCLK , RCC_PERCLK , RCC_SYSTICKCLK , RCC_HCLK3 , RCC_AHBCLK , RCC_APB1CLK , RCC_APB2CLK , RCC_APB3CLK , RCC_APB4CLK } |

| Enumerations for core system/bus clocks for user/driver/system access to base bus clocks not directly associated with a peripheral. More... | |

| enum | rcc_osc { RCC_PLL , RCC_HSE , RCC_HSI , RCC_LSE , RCC_LSI } |

| enum | rcc_periph_clken { RCC_DMA1 = _REG_BIT(0xD8, 0) , RCC_DMA2 = _REG_BIT(0xD8, 1) , RCC_ADC12 = _REG_BIT(0xD8, 5) , RCC_ETH1MAC = _REG_BIT(0xD8, 15) , RCC_ETH1TX = _REG_BIT(0xD8, 16) , RCC_ETH1RX = _REG_BIT(0xD8, 17) , RCC_USB2OTGHSULPIEN = _REG_BIT(0xD8, 18) , RCC_USB1OTGHSEN = _REG_BIT(0xD8, 25) , RCC_USB1OTGHSULPIEN = _REG_BIT(0xD8, 26) , RCC_USB2OTGHSEN = _REG_BIT(0xD8, 27) , RCC_DCMI = _REG_BIT(0xDC, 0) , RCC_CRYP = _REG_BIT(0xDC, 4) , RCC_HASH = _REG_BIT(0xDC, 5) , RCC_RNG = _REG_BIT(0xDC, 6) , RCC_SDMMC2 = _REG_BIT(0xDC, 9) , RCC_SRAM1 = _REG_BIT(0xDC, 29) , RCC_SRAM2 = _REG_BIT(0xDC, 30) , RCC_SRAM3 = _REG_BIT(0xDC, 31) , RCC_MDMA = _REG_BIT(0xD4, 0) , RCC_DMA2D = _REG_BIT(0xD4, 4) , RCC_JPGDEC = _REG_BIT(0xD4, 5) , RCC_FMC = _REG_BIT(0xD4, 12) , RCC_QSPI = _REG_BIT(0xD4, 14) , RCC_SDMMC1 = _REG_BIT(0xD4, 16) , RCC_GPIOA = _REG_BIT(0xE0, 0) , RCC_GPIOB = _REG_BIT(0xE0, 1) , RCC_GPIOC = _REG_BIT(0xE0, 2) , RCC_GPIOD = _REG_BIT(0xE0, 3) , RCC_GPIOE = _REG_BIT(0xE0, 4) , RCC_GPIOF = _REG_BIT(0xE0, 5) , RCC_GPIOG = _REG_BIT(0xE0, 6) , RCC_GPIOH = _REG_BIT(0xE0, 7) , RCC_GPIOI = _REG_BIT(0xE0, 8) , RCC_GPIOJ = _REG_BIT(0xE0, 9) , RCC_GPIOK = _REG_BIT(0xE0, 10) , RCC_CRC = _REG_BIT(0xE0, 19) , RCC_BDMA = _REG_BIT(0xE0, 21) , RCC_ADC3 = _REG_BIT(0xE0, 24) , RCC_HSEM = _REG_BIT(0xE0, 25) , RCC_BKPSRAM = _REG_BIT(0xE0, 28) , RCC_TIM2 = _REG_BIT(0xE8, 0) , RCC_TIM3 = _REG_BIT(0xE8, 1) , RCC_TIM4 = _REG_BIT(0xE8, 2) , RCC_TIM5 = _REG_BIT(0xE8, 3) , RCC_TIM6 = _REG_BIT(0xE8, 4) , RCC_TIM7 = _REG_BIT(0xE8, 5) , RCC_TIM12 = _REG_BIT(0xE8, 6) , RCC_TIM13 = _REG_BIT(0xE8, 7) , RCC_TIM14 = _REG_BIT(0xE8, 8) , RCC_LPTIM1 = _REG_BIT(0xE8, 9) , RCC_SPI2 = _REG_BIT(0xE8, 14) , RCC_SPI3 = _REG_BIT(0xE8, 15) , RCC_SPDIFRX = _REG_BIT(0xE8, 16) , RCC_USART2 = _REG_BIT(0xE8, 17) , RCC_USART3 = _REG_BIT(0xE8, 18) , RCC_UART4 = _REG_BIT(0xE8, 19) , RCC_UART5 = _REG_BIT(0xE8, 20) , RCC_I2C1 = _REG_BIT(0xE8, 21) , RCC_I2C2 = _REG_BIT(0xE8, 22) , RCC_I2C3 = _REG_BIT(0xE8, 23) , RCC_CEC = _REG_BIT(0xE8, 27) , RCC_DAC = _REG_BIT(0xE8, 29) , RCC_UART7 = _REG_BIT(0xE8, 30) , RCC_UART8 = _REG_BIT(0xE8, 31) , RCC_CRS = _REG_BIT(0xEC, 1) , RCC_SWP = _REG_BIT(0xEC, 2) , RCC_OPAMP = _REG_BIT(0xEC, 4) , RCC_MDIO = _REG_BIT(0xEC, 5) , RCC_FDCAN = _REG_BIT(0xEC, 8) , RCC_TIM1 = _REG_BIT(0xF0, 0) , RCC_TIM8 = _REG_BIT(0xF0, 1) , RCC_USART1 = _REG_BIT(0xF0, 4) , RCC_USART6 = _REG_BIT(0xF0, 5) , RCC_SPI1 = _REG_BIT(0xF0, 12) , RCC_SPI4 = _REG_BIT(0xF0, 13) , RCC_TIM15 = _REG_BIT(0xF0, 16) , RCC_TIM16 = _REG_BIT(0xF0, 17) , RCC_TIM17 = _REG_BIT(0xF0, 18) , RCC_SPI5 = _REG_BIT(0xF0, 20) , RCC_SAI1 = _REG_BIT(0xF0, 22) , RCC_SAI2 = _REG_BIT(0xF0, 23) , RCC_SAI3 = _REG_BIT(0xF0, 24) , RCC_DFSDM = _REG_BIT(0xF0, 28) , RCC_HRTIM = _REG_BIT(0xF0, 29) , RCC_LTDCEN = _REG_BIT(0xE4, 3) , RCC_WWDG1EN = _REG_BIT(0xE4, 6) , RCC_SYSCFG = _REG_BIT(0xF4, 1) , RCC_LPUART1 = _REG_BIT(0xF4, 3) , RCC_SPI6 = _REG_BIT(0xF4, 5) , RCC_I2C4 = _REG_BIT(0xF4, 7) , RCC_LPTIM2 = _REG_BIT(0xF4, 9) , RCC_LPTIM3 = _REG_BIT(0xF4, 10) , RCC_LPTIM4 = _REG_BIT(0xF4, 11) , RCC_LPTIM5 = _REG_BIT(0xF4, 12) , RCC_COMP12 = _REG_BIT(0xF4, 14) , RCC_VREF = _REG_BIT(0xF4, 15) , RCC_RTCAPB = _REG_BIT(0xF4, 16) , RCC_SAI4 = _REG_BIT(0xF4, 21) } |

| enum | rcc_periph_rst { RST_DMA1 = _REG_BIT(0x80, 0) , RST_DMA2 = _REG_BIT(0x80, 1) , RST_ADC12 = _REG_BIT(0x80, 5) , RST_ETH1MAC = _REG_BIT(0x80, 15) , RST_USB1OTGRST = _REG_BIT(0x80, 25) , RST_USB2OTGRST = _REG_BIT(0x80, 27) , RST_DCMI = _REG_BIT(0xDC, 0) , RST_CRYP = _REG_BIT(0xDC, 4) , RST_HASH = _REG_BIT(0xDC, 5) , RST_RNG = _REG_BIT(0xDC, 6) , RST_SDMMC2 = _REG_BIT(0xDC, 9) , RST_MDMA = _REG_BIT(0x7C, 0) , RST_DMA2D = _REG_BIT(0x7C, 4) , RST_JPGDEC = _REG_BIT(0x7C, 5) , RST_FMC = _REG_BIT(0x7C, 12) , RST_QSPI = _REG_BIT(0x7C, 14) , RST_SDMMC1 = _REG_BIT(0x7C, 16) , RST_GPIOA = _REG_BIT(0x88, 0) , RST_GPIOB = _REG_BIT(0x88, 1) , RST_GPIOC = _REG_BIT(0x88, 2) , RST_GPIOD = _REG_BIT(0x88, 3) , RST_GPIOE = _REG_BIT(0x88, 4) , RST_GPIOF = _REG_BIT(0x88, 5) , RST_GPIOG = _REG_BIT(0x88, 6) , RST_GPIOH = _REG_BIT(0x88, 7) , RST_GPIOI = _REG_BIT(0x88, 8) , RST_GPIOJ = _REG_BIT(0x88, 9) , RST_GPIOK = _REG_BIT(0x88, 10) , RST_CRC = _REG_BIT(0x88, 19) , RST_BDMA = _REG_BIT(0x88, 21) , RST_ADC3 = _REG_BIT(0x88, 24) , RST_HSEM = _REG_BIT(0x88, 25) , RST_TIM2 = _REG_BIT(0x90, 0) , RST_TIM3 = _REG_BIT(0x90, 1) , RST_TIM4 = _REG_BIT(0x90, 2) , RST_TIM5 = _REG_BIT(0x90, 3) , RST_TIM6 = _REG_BIT(0x90, 4) , RST_TIM7 = _REG_BIT(0x90, 5) , RST_TIM12 = _REG_BIT(0x90, 6) , RST_TIM13 = _REG_BIT(0x90, 7) , RST_TIM14 = _REG_BIT(0x90, 8) , RST_LPTIM1 = _REG_BIT(0x90, 9) , RST_SPI2 = _REG_BIT(0x90, 14) , RST_SPI3 = _REG_BIT(0x90, 15) , RST_SPDIFRX = _REG_BIT(0x90, 16) , RST_USART2 = _REG_BIT(0x90, 17) , RST_USART3 = _REG_BIT(0x90, 18) , RST_UART4 = _REG_BIT(0x90, 19) , RST_UART5 = _REG_BIT(0x90, 20) , RST_I2C1 = _REG_BIT(0x90, 21) , RST_I2C2 = _REG_BIT(0x90, 22) , RST_I2C3 = _REG_BIT(0x90, 23) , RST_CEC = _REG_BIT(0x90, 27) , RST_DAC = _REG_BIT(0x90, 29) , RST_UART7 = _REG_BIT(0x90, 30) , RST_UART8 = _REG_BIT(0x90, 31) , RST_CRS = _REG_BIT(0x94, 1) , RST_SWP = _REG_BIT(0x94, 2) , RST_OPAMP = _REG_BIT(0x94, 4) , RST_MDIO = _REG_BIT(0x94, 5) , RST_FDCAN = _REG_BIT(0x94, 8) , RST_TIM1 = _REG_BIT(0x98, 0) , RST_TIM8 = _REG_BIT(0x98, 1) , RST_USART1 = _REG_BIT(0x98, 4) , RST_USART6 = _REG_BIT(0x98, 5) , RST_SPI1 = _REG_BIT(0x98, 12) , RST_SPI4 = _REG_BIT(0x98, 13) , RST_TIM15 = _REG_BIT(0x98, 16) , RST_TIM16 = _REG_BIT(0x98, 17) , RST_TIM17 = _REG_BIT(0x98, 18) , RST_SPI5 = _REG_BIT(0x98, 20) , RST_SAI1 = _REG_BIT(0x98, 22) , RST_SAI2 = _REG_BIT(0x98, 23) , RST_SAI3 = _REG_BIT(0x98, 24) , RST_DFSDM = _REG_BIT(0x98, 28) , RST_HRTIM = _REG_BIT(0x98, 29) , RST_LTDCRST = _REG_BIT(0x8C, 3) , RST_SYSCFG = _REG_BIT(0x9C, 1) , RST_LPUART1 = _REG_BIT(0x9C, 3) , RST_SPI6 = _REG_BIT(0x9C, 5) , RST_I2C4 = _REG_BIT(0x9C, 7) , RST_LPTIM2 = _REG_BIT(0x9C, 9) , RST_LPTIM3 = _REG_BIT(0x9C, 10) , RST_LPTIM4 = _REG_BIT(0x9C, 11) , RST_LPTIM5 = _REG_BIT(0x9C, 12) , RST_COMP12 = _REG_BIT(0x9C, 14) , RST_VREF = _REG_BIT(0x9C, 15) , RST_SAI4 = _REG_BIT(0x9C, 21) } |

Functions | |

| void | rcc_clock_setup_pll (const struct rcc_pll_config *config) |

| Setup the base PLLs and clock domains for the STM32H7. More... | |

| uint32_t | rcc_get_bus_clk_freq (enum rcc_clock_source source) |

| Get the clock rate (in Hz) of the specified clock source. More... | |

| uint32_t | rcc_get_usart_clk_freq (uint32_t usart) |

| Get the peripheral clock speed for the USART at base specified. More... | |

| uint32_t | rcc_get_timer_clk_freq (uint32_t timer) |

| Get the peripheral clock speed for the Timer at base specified. More... | |

| uint32_t | rcc_get_i2c_clk_freq (uint32_t i2c) |

| Get the peripheral clock speed for the I2C device at base specified. More... | |

| uint32_t | rcc_get_spi_clk_freq (uint32_t spi) |

| Get the peripheral clock speed for the SPI device at base specified. More... | |

| uint32_t | rcc_get_fdcan_clk_freq (uint32_t fdcan) |

| Get the peripheral clock speed for the FDCAN device at base specified. More... | |

| void | rcc_set_peripheral_clk_sel (uint32_t periph, uint32_t clksel) |

| Set the clksel value for the specified peripheral. More... | |

| void | rcc_set_fdcan_clksel (uint8_t clksel) |

| Set the clock select for the FDCAN devices. More... | |

| void | rcc_set_spi123_clksel (uint8_t clksel) |

| Set the clock select for the SPI 1/2/3 devices. More... | |

| void | rcc_set_spi45_clksel (uint8_t clksel) |

| Set the clock select for the SPI 4/5 devices. More... | |

| void | rcc_set_rng_clksel (uint8_t clksel) |

| Set the clock select for the RNG device. More... | |